- ICDł¶Ķś≤ŮÕ•Ĺ®ľ„ľÍĻ÷Īťĺř

- "•’•Ū°ľ•∆•£•ů•į•≤°ľ•»§™§Ť§”•Ń•„°ľ•ł•»•ť•√•◊TLC NAND•’•ť•√•∑•Ś•Š•‚•Í§ň§™§Ī§Ž•»°ľ•Ņ•Ž•…°ľ•ļłķ≤Ő§ő•«°ľ•Ņ•—•Ņ°ľ•ůįÕ¬łņ≠",ĺģŖ∑¬ņīű, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2024«Į5∑Ó10∆Łľűĺř)

- •«•∂•§•ů•¨•§•ĘÕ•Ĺ®•›•Ļ•Ņ°ľĺř

- "•’•Ū°ľ•∆•£•ů•į•≤°ľ•»§™§Ť§”•Ń•„°ľ•ł•»•ť•√•◊TLC NAND•’•ť•√•∑•Ś•Š•‚•Í§ň§™§Ī§Ž•»°ľ•Ņ•Ž•…°ľ•ļłķ≤Ő§ő•«°ľ•Ņ•—•Ņ°ľ•ůįÕ¬łņ≠",ĺģŖ∑¬ņīű(2023«Į11∑Ó17∆Łľűĺř)

- •«•∂•§•ů•¨•§•ĘÕ•Ĺ®•›•Ļ•Ņ°ľĺř

- "¶ŃņĢĺ»ľÕ§ň§Ť§Ž65nm bulk•◊•Ū•Ľ•Ļ§ň§™§Ī§ŽPMOSĶ৔NMOS•»•ť•ů•ł•Ļ•Ņ§őSEUī∂ŇŔ",Ķ»Ňń∑ŬŃ(2023«Į£Ī£Ī∑Ó17∆Łľűĺř)

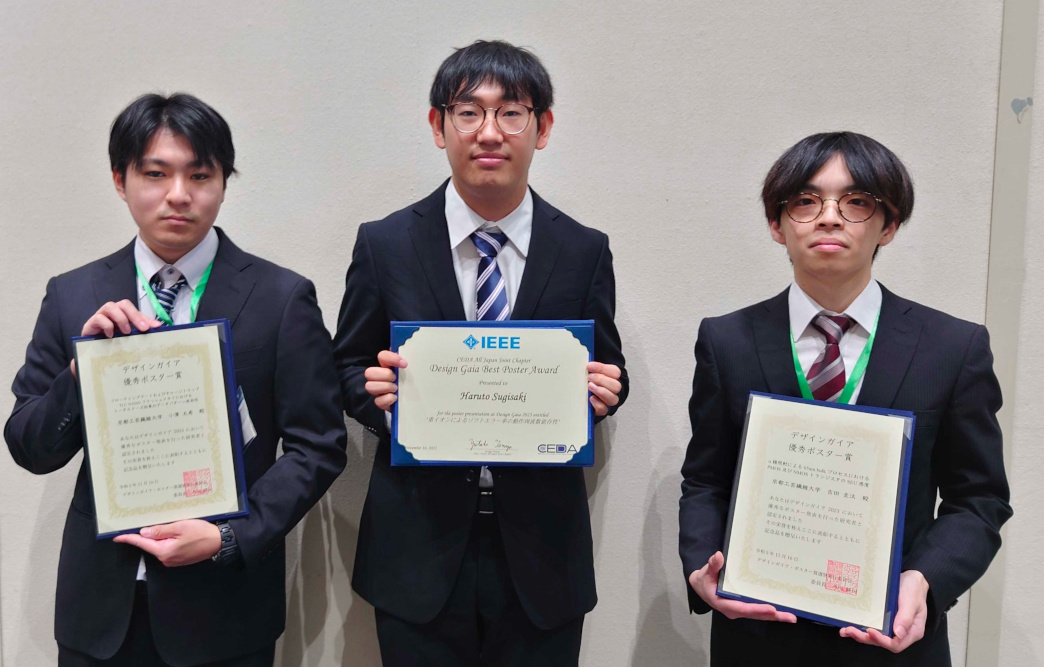

- IEEE CEDA All Japan Joint Chapter Design Gaia Best Paper Award

- "•Ę•Ž•’•°ņĢ§»ĹŇ•§•™•ů§ň§Ť§Ž•Ĺ•’•»•®•ť°ľő®§őľĢ«»ŅŰįÕ¬łņ≠§ő¬¨ńÍ",ŅýļÍĹ’ŇÕ(2023«Į£Ī£Ī∑Ó17∆Łľűĺř)

- SLDM WIPļ«Õ•Ĺ®ĺř

- "Ķ°≥£≥ōŨ§ňīū§Ň§Į«Ųňž•Š•ŗ•≠•„•—•∑•Ņ§ő•‚•«•Ž≤ŧňīō§Ļ§ŽįžĻÕĽ°", ĪļŇń ő√≤Ū (ĶĢŇ‘Ļ©Ń°¬Á), Őା ň” (ő∂√ę¬Á≥ō), Ņ∑√ę ∆ĽĻ≠ (ĶĢŇ‘Ļ©Ń°¬Á) (2023«Į11∑Ó7∆Łľűĺř)

- Excellent Student Paper Certificate of Honor of 2023 15th IEEE International Conference on ASIC

- "Ring Oscillators with Identical Circuit Structure to Measure Bias Temperature Instability", Daisuke Kikuta, Ryo Kishida, Kazutoshi Kobayashi (2023«Į10∑Ó27∆Łľűĺř)

- IEEE CEDA All Japan Joint Chapter Academic Research Award

- "C-element§ň§Ť§Í√Īįž•ő°ľ•…»ŅŇĺ§ň∂ĮŅŔ§ ¬—•Ĺ•’•»•®•ť°ľ•’•Í•√•◊•’•Ū•√•◊§őńůį∆", įň∆£ĶģĽň, √śŇÁőīįž, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2023«Į8∑Ó30∆Łľűĺř), https://site.ieee.org/jc-ceda/awards/ieee-ceda-all-japan-joint-chapter-best-student-award/

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2022•Ľ•√•∑•Á•ů∆√ Őĺř

- "C-element§ň§Ť§Í√Īįž•ő°ľ•…»ŅŇĺ§ň∂ĮŅŔ§ ¬—•Ĺ•’•»•®•ť°ľ•’•Í•√•◊•’•Ū•√•◊§őńůį∆", įň∆£ĶģĽň, √śŇÁőīįž, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2023«Į8∑Ó30∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2022Õ•Ĺ®»Į…Ĺĺř

- "C-element§ň§Ť§Í√Īįž•ő°ľ•…»ŅŇĺ§ň∂ĮŅŔ§ ¬—•Ĺ•’•»•®•ť°ľ•’•Í•√•◊•’•Ū•√•◊§őńůį∆", įň∆£ĶģĽň, √śŇÁőīįž, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2023«Į8∑Ó30∆Łľűĺř)

- •≠•™•Į•∑•Ęĺ©őŚł¶Ķś2022«ĮŇŔ•∑•Ļ•∆•ŗ…ŰŐÁÕ•Ĺ®ł¶Ķśĺř

- Ņ∑√ę∆ĽĻ≠(2023«Į6∑Ó1∆Łľűĺř),https://www.kioxia.com/ja-jp/rd/collaboration/award-fy2022.html

- IEEE CEDA All Japan Joint Chapter Academic Research Award

- "ī÷∑Á∆įļÓ§ÚĻ‘§¶IoTłĢ§Ī•◊•Ū•Ľ•√•Ķ§ňҨ§∑§ŅFiCC∑Ņ…‘īÝ»Į•’•Í•√•◊•’•Ū•√•◊§őľ¬¬¨…ĺ≤Ń",į§…ŰÕ§Ķģ, ĺģő”Ō¬Ĺ , ĪŘ√“ÕĶ«∑(2022«Į11∑Ó29∆Łľűĺř), https://site.ieee.org/jc-ceda/awards/ieee-ceda-all-japan-joint-chapter-best-student-award/

- [•≠•™•Į•∑•Ęĺ©őŚł¶Ķś2022«ĮŇŔ•∑•Ļ•∆•ŗ…ŰŐÁÕ•Ĺ®ł¶Ķśĺř|https

- //www.kioxia.com/ja-jp/rd/collaboration/award-fy2022.html]:Ņ∑√ę∆ĽĻ≠(2023«Į6∑Ó1∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů WIPļ«Õ•Ĺ®ĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•Ļ•Ņ•√•ĮĻŬ§§ÚÕ—§§§Ņ•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§őľ¬¬¨…ĺ≤Ń", Ņý√ęĺļ¬ņŌļ°§ √śŇÁőīįž°§ łŇŇńĹŠ°§ ĺģő”Ō¬Ĺ (2022«Į11∑Ó11∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2022Õ•Ĺ®•›•Ļ•Ņ°ľĺř

- "FiCC∑Ņ…‘īÝ»Į•’•Í•√•◊•’•Ū•√•◊§ÚÕ—§§§Ņī÷∑Á∆įļÓ≤ń«Ĺ§ •ę•¶•ů•Ņ§őľ¬¬¨…ĺ≤Ń, į§…Ű Õ§Ķģ(2022«Į9∑Ó1∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů Õ•Ĺ®»Į…Ĺĺř

- "TCAD§ÚÕ—§§§Ņ≤ůŌ©§»•ž•§•Ę•¶•»ĻŬ§§ň§Ť§Ž•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ő…ĺ≤Ń", ĺģ√ęň®ĻŠ(2022«Į8∑Ó31∆Łľűĺř)

- •≠•™•Į•∑•Ęĺ©őŚł¶Ķś2022«ĮŇŔ•∑•Ļ•∆•ŗ…ŰŐÁÕ•Ĺ®ł¶Ķśĺř

- Ņ∑√ę∆ĽĻ≠(2022«Į6∑Ó1∆Łľűĺř), https://www.kioxia.com/ja-jp/rd/collaboration/award-fy2022.html

- LSI§»•∑•Ļ•∆•ŗ§ő•Ô°ľ•Į•∑•Á•√•◊ļ«Õ•Ĺ®•›•Ļ•Ņ°ľĺř

- ľÚłĢő (∑≤«Ō¬Á≥ō)°§ Ł‚įśŅ≠Ō¬(2022«Į5∑Ó10∆Łľűĺř)

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤ŮīōņĺĽŔ…Ű ĽŔ…ŰńĻĺř łýŌęĺř

- į§…ŰÕ§Ķģ°§įň∆£ĶģĽň°§ĺģ√ęň®ĻŠ°§√śŇÁőīįž° 2022«Į3∑Ó10∆Łľűĺř°ň, https://www.ieice.org/kansai/student/kourou2021.html

- IEEE CEDA All Japan Joint Chapter (AJJC) Design Gaia Best Poster Award

- "Soft Errors on Flip-flops Depending on Circuit and Layout Structures Estimated by TCAD Simulations", ĺģ√ęň®ĻŠ(2021«Į12∑Ó2∆Łľűĺř), https://site.ieee.org/jc-ceda/awards/ieee-ceda-all-japan-joint-chapter-design-gaia-best-poster-award/

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů ¬Ť24≤ů•®•ž•Į•»•Ū•ň•Į•Ļ•Ĺ•Ķ•§•®•∆•£ĺř

- "Ĺłņ—≤ůŌ©§ő•Ĺ•’•»•®•ť°ľ§őĻ‚¬—≤ĹĶĽĹ—§őņŤ∂ÓŇ™ł¶Ķś",ĺģő”Ō¬Ĺ (2021«Į9∑Ó14∆Łľűĺř)https://www.ieice.org/es/jpn/award/es.php

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů•Í•≥•ů•’•£•ģ•„•ť•÷•Ž•∑•Ļ•∆•ŗł¶Ķś≤ŮÕ•Ĺ®Ļ÷Īťĺř(ľ„ľÍ…ŰŐÁ)

- "•∑•’•»•ž•ł•Ļ•Ņ§ň§Ť§ŽSRAM∑Ņ§»•’•ť•√•∑•Ś•Š•‚•Í∑ŅFPGA§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ő»ś≥”",≤ŌŐÓÕļŐť(2021«Į£Ļ∑Ó£Ī£į∆Łľűĺř)

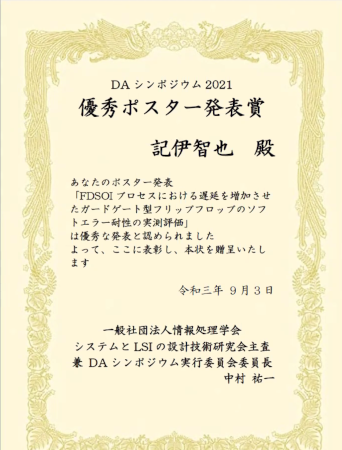

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2021Õ•Ĺ®•›•Ļ•Ņ°ľĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž√ŔĪš§ÚŃż≤√§Ķ§Ľ§Ņ•¨°ľ•…•≤°ľ•»∑Ņ•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§őľ¬¬¨…ĺ≤Ń", Ķ≠įň√“Őť(2021«Į9∑Ó3∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů Õ•Ĺ®Ōņ łĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•¨°ľ•…•≤°ľ•»ĻŬ§§ÚÕ—§§§Ņ•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§őľ¬¬¨…ĺ≤Ń", Ķ≠įň√“Őť, Ī›ł∂łų¬ß, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2021«Į9∑Ó£Ī∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů Õ•Ĺ®»Į…Ĺĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•¨°ľ•…•≤°ľ•»ĻŬ§§ÚÕ—§§§Ņ•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§őľ¬¬¨…ĺ≤Ń", Ķ≠įň√“Őť, Ī›ł∂łų¬ß, łŇŇńĹŠ, ĺģő”Ō¬Ĺ (2021«Į9∑Ó£Ī∆Łľűĺř)

- IEEE CEDA All Japan Joint Chapter Academic Research Award

- "Evalution of Soft Error Tolerance by Flip-Flop Using Guard Gate", Ķ≠įň√“Őť(2021«Į9∑Ó1∆Łľűĺř)

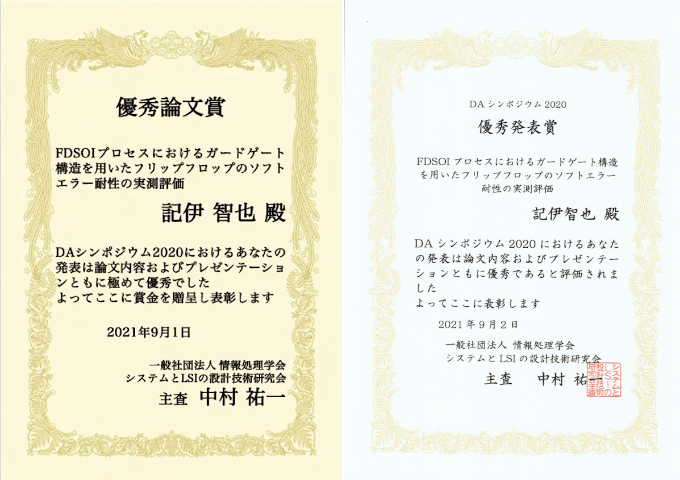

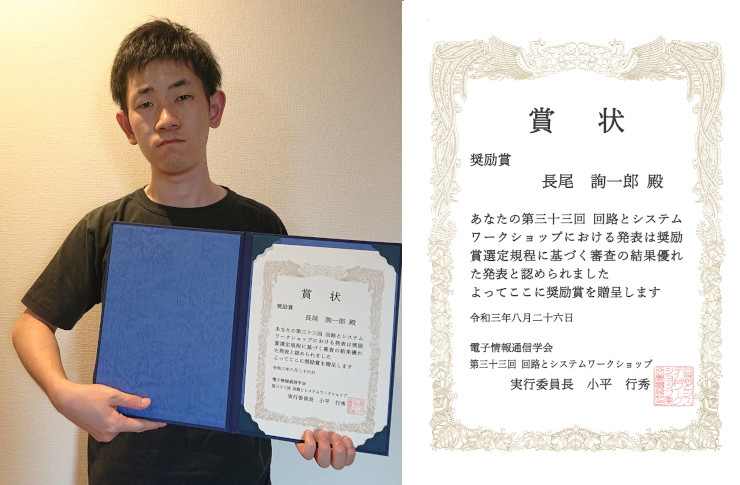

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů ¬Ť£≥£≥≤ů≤ůŌ©§»•∑•Ļ•∆•ŗ•Ô°ľ•Į•∑•Á•√•◊ ĺ©őŚĺř

- "•÷•Í•√•ł≤ůŌ©§ňҨ§∑§ŅGaN HEMTłĢ§Ī√ĪįžŇŇłĽ∂Ó∆į3•ž•Ŕ•ŽŇŇįĶņ©łś•≤°ľ•»•…•ť•§•–" ńĻ»ÝŽőįžŌļ (2020«Į12∑Ó19∆ŁľűĺřńŐ√ő, 2021«Į8∑Ó26∆Łľűĺř) https://www.ieice.org/~kws/last_award.html

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2019 Õ•Ĺ®Ōņ łĺř

- " "īń∂≠ —∆į§Ú¬«§Ńĺ√§∑∑–«ĮőŰ≤ŧőŇŇįĶįÕ¬łņ≠§Úī—¬¨§Ļ§Ž•Í•ů•į•™•∑•ž°ľ•Ņ§őńůį∆" ĺģĻ‚Ļ¶ūů° ŇžĶĢÕż≤ ¬Á°ň (£≤£į£≤£į«Į8∑Ó£∑∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2019 Õ•Ĺ®≥ōņł»Į…Ĺĺř

- "īń∂≠ —∆į§Ú¬«§Ńĺ√§∑∑–«ĮőŰ≤ŧőŇŇįĶįÕ¬łņ≠§Úī—¬¨§Ļ§Ž•Í•ů•į•™•∑•ž°ľ•Ņ§őńůį∆" ĺģĻ‚Ļ¶ūů° ŇžĶĢÕż≤ ¬Á°ň (£≤£į£≤£į«Į8∑Ó£∑∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2019 Õ•Ĺ®≥ōņł»Į…Ĺĺř

- " "•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§ŅFDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•ť•√•ŃĻŬ§§őį„§§§ň§Ť§Ž•Ĺ•’•»•®•ť°ľ¬—ņ≠§őīū»ńŇŇįĶįÕ¬łņ≠§ő…ĺ≤Ń" ĺģŇÁ∑Ú¬ņŌļ (£≤£į£≤£į«Į8∑Ó£∑∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •≥•ů•‘•Ś°ľ•Ņ•Ķ•§•®•ů•ĻőőįŤĺ©őŚĺř° CSőőįŤĺ©őŚĺř°ň

- "•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§ŅFDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•ť•√•ŃĻŬ§§őį„§§§ň§Ť§Ž•Ĺ•’•»•®•ť°ľ¬—ņ≠§őīū»ńŇŇįĶįÕ¬łņ≠§ő…ĺ≤Ń" ĺģŇÁ∑Ú¬ņŌļ (2020«Į7∑Ó7∆Łľűĺř) https://www.ipsj.or.jp/award/cs-award-2020.html

- ĺū ůĹŤÕż≥ō≤ŮĽ≥≤ľĶ≠«įĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•Ļ•Ņ•√•ĮĻŬ§§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ÚĻ‚§Š§Ž¬–ļŲľÍň°§őńůį∆§™§Ť§”•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ…ĺ≤Ń",Ľ≥ŇńĻł¬Á° £≤£į£≤£į«Į£≥∑Ó£∂∆Łľűĺř°ňhttps://www.ipsj.or.jp/award/yamasita2019-detail.html#sldm

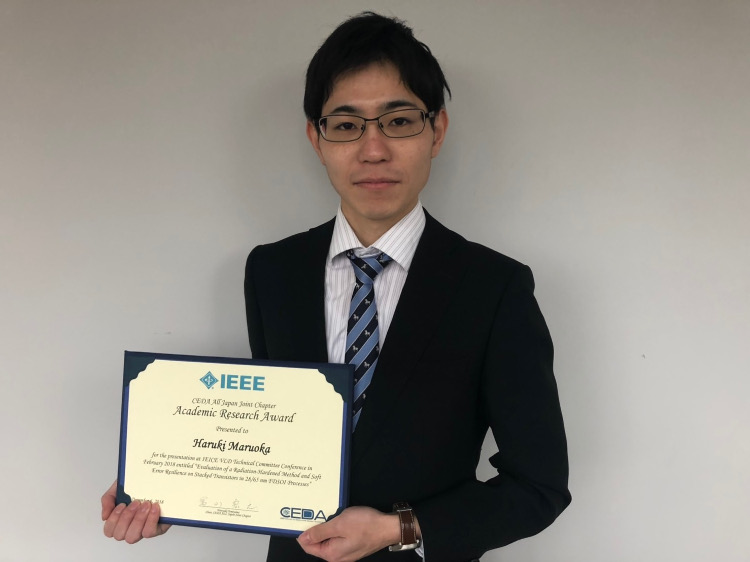

- IEEE CEDA All Japan Joint Chapter Academic Research Award

- "Evaluation of Radiation-hardened Structure for Stacked Transistors in FDSOI Process by Device Simulations", Ľ≥ŇńĻł¬Á(2019«Į8∑Ó28∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ£Ő£”£…ņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů2018«ĮŇŔļ«Õ•Ĺ®»Į…Ĺ≥ōņłĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•Ļ•Ņ•√•ĮĻŬ§§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ÚĻ‚§Š§Ž¬–ļŲľÍň°§őńůį∆§™§Ť§”•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ…ĺ≤Ń", Ľ≥ŇńĻł¬Á(2019«Į£ł∑Ó£≤£ł∆Łľűĺř°ň

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ£Ő£”£…ņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů2018«ĮŇŔÕ•Ĺ®»Į…Ĺ≥ōņłĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•Ļ•Ņ•√•ĮĻŬ§§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ÚĻ‚§Š§Ž¬–ļŲľÍň°§őńůį∆§™§Ť§”•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ…ĺ≤Ń", Ľ≥ŇńĻł¬Á(2019«Į£ł∑Ó£≤£ł∆Łľűĺř°ň

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ£Ő£”£…ņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů2018«ĮŇŔÕ•Ĺ®»Į…Ĺ≥ōņłĺř

- "•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ65nm FDSOI•«•–•§•Ļ§őņŇ∆√ņ≠§ő —≤ŧ»•Ĺ•’•»•®•ť°ľ¬—ņ≠§ő…ĺ≤Ń", ĺģŇÁ∑Ú¬ņŌļ(2019«Į£ł∑Ó£≤£ł∆Łľűĺř°ň

- ICMTS(International Conference on Microelectronic Test Structure) Best Paper Award

- "Extracting BTI-induced Degradation without Temporal Factors by Using BTI-Sensitive and BTI-Insensitive Ring Oscillators", R. Kishida, T. Asuke, J. Furuta, and K. Kobayashi (2019«Į£≥∑Óľűĺř)

- IEEE īōņĺĽŔ…Ű ≥ōņłł¶Ķśĺ©őŚĺř

- "Radiation-Hardened Flip-Flops with Low-Delay Overhead Using PMOS Pass-Transistors to Suppress SET Pulses in a 65 nm FDSOI Process",Ľ≥ŇńĻł¬Á(2019«Į2∑Ó25∆Łľűĺř)

- IEEE CEDA All Japan Joint Chapter (AJJC) Design Gaia Best Poster Award

- "√ŔĪš§ÚÕř§®§Ņ•Ļ•Ņ•√•ĮĻŬ§§ň§Ť§ŽSOI•◊•Ū•Ľ•ĻłĢ§Ī¬—•Ĺ•’•»•®•ť°ľFF§őńůį∆§™§Ť§”ľ¬¬¨…ĺ≤Ń", Ī›ł∂łų¬ß (2018«Į12∑Ó6∆Łľűĺř) https://site.ieee.org/jc-ceda/awards/ieee-ceda-all-japan-joint-chapter-design-gaia-best-poster-award/

- IEEE CEDA All Japan Joint Chapter Academic Research Award

- °…FDSOI§ňҨ§∑§Ņ•Ļ•Ņ•√•ĮĻŬ§§ň§™§Ī§Ž•Ĺ•’•»•®•ť°ľ¬–ļŲľÍň°§őńůį∆°¶…ĺ≤ѧ»»ýļŔ≤ŧň§Ť§ŽĪ∆∂ѧő…ĺ≤Ń", ī›≤¨ ņ≤īÓ (2018«Į12∑Ó6∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2018 ļ«Õ•Ĺ®•›•Ļ•Ņ°ľ»Į…Ĺĺř

- "FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•Ļ•Ņ•√•ĮĻŬ§§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§ÚĻ‚§Š§Ž¬–ļŲľÍň°§őńůį∆§™§Ť§”•«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ…ĺ≤Ń", Ľ≥ŇńĻł¬Á (2018«Į8∑Ó30∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2018 Õ•Ĺ®•›•Ļ•Ņ°ľ»Į…Ĺĺř

- " •«•–•§•Ļ•∑•Ŗ•Ś•ž°ľ•∑•Á•ů§ÚÕ—§§§Ņ65nm FDSOI•«•–•§•Ļ§őņŇ∆√ņ≠§ő —≤ŧ»•Ĺ•’•»•®•ť°ľ¬—ņ≠§ő…ĺ≤Ń", ĺģŇÁ∑Ú¬ņŌļ (2018«Į8∑Ó30∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2017Õ•Ĺ®»Į…Ĺ≥ōņłĺř

- "PMOS•—•Ļ•»•ť•ů•ł•Ļ•Ņ§ÚÕ—§§§Ņ»ů¬ŅĹŇ≤Ŭ—•Ĺ•’•»•®•ť°ľFF§őńůį∆Ķ৔…ĺ≤Ń", Ľ≥ŇńĻł¬Á (2018«Į8∑Ó29∆Łľűĺř) https://www.ipsj.or.jp/award/sldm-award1.html

- ĺū ůĹŤÕż≥ō≤Ů •≥•ů•‘•Ś°ľ•Ņ•Ķ•§•®•ů•ĻőőįŤĺ©őŚĺř° CSőőįŤĺ©őŚĺř°ň

- PMOS•—•Ļ•»•ť•ů•ł•Ļ•Ņ§ÚÕ—§§§Ņ»ů¬ŅĹŇ≤Ŭ—•Ĺ•’•»•®•ť°ľFF§őńůį∆Ķ৔…ĺ≤Ń, Ľ≥ŇńĻł¬Á (2018«Į8∑Ó29∆Łľűĺř) https://www.ipsj.or.jp/award/cs-awardee-2018.html

- TPEC 2018 Second-Place Best Poster Award

- "Design of gate driver monolithically integrated with power p-GaN HEMT based on E-mode GaN-on-Si technology", Yuki Yamashita (2018«Į2∑Ó9∆Łľűĺř)

- •∑•Ļ•∆•ŗ§»LSI§ő•Ô°ľ•Į•∑•Á•√•◊2017 ≥ōņł…ŰŐÁÕ•Ĺ®ĺř

- "FDSOI§ň§™§Ī§Ž»ů¬ŅĹŇ≤Ŭ—•Ĺ•’•»•®•ť°ľFF§őņŖ∑◊§»…ĺ≤Ń", Ľ≥ŇńĻł¬Á°§ī›≤¨ņ≤īÓ°§łŇŇńĹŠ°§ĺģő”Ō¬Ĺ (2017«Į5∑Ó17∆Łľűĺř)

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů ¬Ť29≤ů≤ůŌ©§»•∑•Ļ•∆•ŗ•Ô°ľ•Į•∑•Á•√•◊ ĺ©őŚĺř

- "65nm FDSOI•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž•ť•ů•ņ•ŗ•∆•ž•į•ť•’•ő•§•ļ§ő¬¨ńͧ»…ĺ≤Ń", ∂ūŌ∆¬ůŐÔ, ¬ÁŇÁįī, īŖŇńőľ, ĺģő”Ō¬Ĺ (2017«Į5∑Ó11∆Łľűĺř)

- COOL Chips 20 Best Poster Award

- Kodai Yamada, Haruki Maruoka, Jun Furuta, Kazutoshi Kobayashi, (2017«Į£ī∑Ó£≤£Ī∆Łľűĺř°ňhttp://www.coolchips.org/2017/

- IEEE EDS Kansai Chapter MFSK Award

- Negative Bias Temperature Instability Caused by Plasma Induced Damage in 65 nm Bulk and Silicon On Thin BOX (SOTB) Processes in IRPS 2015, Ryo Kishida (2017«Į1∑Ó30∆Łľűĺř), MFSK_2017_kishida.pdf(650)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2015 Õ•Ĺ®≥ōņł»Į…Ĺĺř

- "65nm•–•Ž•Į§™§Ť§”SOTB•◊•Ū•Ľ•Ļ§«§ő•Ę•ů•∆• »ś§ň§Ť§ŽņŬ§ĽĢőŰ≤ŧő¬¨ńͧ»…ĺ≤Ń", īŖŇń őľ, ĺģő”Ō¬Ĺ (2016«Į9∑Ó14∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů Õ•Ĺ®Ōņ łĺř

- "65nm•–•Ž•Į§™§Ť§”SOTB•◊•Ū•Ľ•Ļ§«§ő•Ę•ů•∆• »ś§ň§Ť§ŽņŬ§ĽĢőŰ≤ŧő¬¨ńͧ»…ĺ≤Ń", īŖŇń őľ, ĺģő”Ō¬Ĺ (2016«Į9∑Ó14∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2014 Õ•Ĺ®»Į…Ĺ≥ōņłĺř

- "•Í•ů•į•™•∑•ž°ľ•Ņ§ő»ĮŅ∂ľĢ«»Ņ۬¨ńͧ꧝ĶŠ§Š§Ņ•Ę•ů•∆• •ņ•Š°ľ•ł§ň§Ť§ŽĹťīŁ§™§Ť§”∑–«ĮőŰ≤Ĺ…ĺ≤Ń" īŖŇńőľ°Ę¬ÁŇÁįī°Ęšō∆‚»Ģ√“¬ņŌļ°Ęĺģő”Ō¬Ĺ (2015«Į8∑Ó27∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2014 Õ•Ĺ®»Į…Ĺ≥ōņłĺř

- "•Í•ů•į∑Ņ»ĮŅ∂īÔ§ő∑–«ĮőŰ≤ŧ»∆√ņ≠§–§ť§ń§≠§őŃÍīō§ő…ĺ≤Ń" šō∆‚»Ģ√“¬ņŌļ°ĘīŖŇńőľ°Ę¬ÁŇÁįī°Ęĺģő”Ō¬Ĺ (2015«Į8∑Ó27∆Łľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗ§»LSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů DA•∑•ů•›•ł•¶•ŗ2014 Õ•Ĺ®»Į…Ĺ≥ōņłĺř

- "65nm«Ųňž BOX-SOI §»•–•Ž•Į•◊•Ū•Ľ•Ļ§ň§™§Ī§Ž SET •—•Ž•Ļ…ż§őŇŇįĶįÕ¬łņ≠§ő…ĺ≤Ń" Ńĺļ¨ļÍĪ”∆ů°¶łŇŇń°°ĹŠ°¶ĺģő”Ō¬Ĺ (2015«Į8∑Ó27∆Łľűĺř)

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů Õ•Ĺ®•Í•≥•ů•’•£•ģ•„•ť•÷•Ž•∑•Ļ•∆•ŗŌņ łĺř

- "Reliability-Configurable Mixed-Grained Reconfigurable Array Supporting C-Based Design and Its Irradiation Testing" Hiroaki Konoura, Dawood Alnajjar (Osaka Univ.), Yukio Mitsuyama (Kochi Inst. Tech), Hajime Shimada(Nagoya U.), Kazutoshi Kobayashi (Kyoto Inst. Tech.), Hiroyuki Kanbara (ASTEM), Hiroyuki Ochi (Ritsumeikan U.), Takashi Imagawa, Kazutoshi Wakabayashi (NEC), Masanori Hashimoto, Takao Onoye (Osaka U.), Hidetoshi Onodera(Kyoto Univ.) (2015«Į6∑Ó19∆Łľűĺř)

- VDEC•«•∂•§•ů•Ę•Ô°ľ•…Õ•Ĺ®ĺř

- ŅņŇńś∆ Ņ°§¬ÁŇÁįī (2014/8/29) http://www.vdec.u-tokyo.ac.jp/designAward/welcome.html

- Best Poster Paper Award of 2013 International Reliability Physics Symposium

- "Contributions of Charge Sharing and Bipolar Effects to Cause or Suppress MCUs on Redundant Latches" by K. Zhang and K. Kobayashi (2014/06/03ľűĺř, https://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=7112664)

- ŇŇĽ“ńŐŅģĺū ů≥ō≤Ů īūŃ√°¶∂≠≥¶•Ĺ•Ķ•§•®•∆•£ ‘Ĺł≥Ť∆įī∂ľ’ĺű

- ĺģő”Ō¬Ĺ (2013/9/18ľűĺř°ň

- ŇŇĽ“ńŐŅģĺū ů≥ō≤Ů īūŃ√°¶∂≠≥¶•Ĺ•Ķ•§•®•∆•£ Ļ◊ł•ĺř

- ĺģő”Ō¬Ĺ (2012/9/12ľűĺř°ň

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤Ů°°≥ōĹ—ĺ©őŚĺř

- D2 šō∆‚»Ģ√“¬ņŌļ (2012/3/21ľűĺř)

- ĺū ůĹŤÕż≥ō≤Ů •∑•Ļ•∆•ŗLSIņŖ∑◊ĶĽĹ—ł¶Ķś≤Ů Õ•Ĺ®Ōņ łĺř

- "SET•—•Ž•Ļ§ň§Ť§ŽłŪ∆įļÓ§Úň…ĽŖ§Ļ§Ž√ŔĪšŃř∆Ģ•’•Í•√•◊•’•Ū•√•◊§ő•Ĺ•’•»•®•ť°ľ¬—ņ≠§őł°∆§" ĺģő”Ō¬Ĺ (2009/8/26ľűĺř°ň

- ŇŇĽ“ĺū ůńŐŅģ≥ō≤ŮŌņ łĺř

- "A 90nm 48x48 LUT-based FPGA Enhancing Spped and Yield Utilizing WIthin-Die Delay Variations" by K.Kobayashi et.al. (2009/5/23ľűĺř, https://www.ieice.org/jpn/about/rekidai/ronbunshou.html

http://www.kit.ac.jp/campus_index/life_fee/report/