# on **Electronics**

VOL. E98-C NO. 7 JULY 2015

The usage of this PDF file must comply with the IEICE Provisions on Copyright.

The author(s) can distribute this PDF file for research and educational (nonprofit) purposes only.

Distribution by anyone other than the author(s) is prohibited.

A PUBLICATION OF THE ELECTRONICS SOCIETY

The Institute of Electronics, Information and Communication Engineers Kikai-Shinko-Kaikan Bldg., 5-8, Shibakoen 3chome, Minato-ku, TOKYO, 105-0011 JAPAN

# PAPER Special Section on Low-Power and High-Speed Chips

# A Perpetuum Mobile 32bit CPU on 65nm SOTB CMOS Technology with Reverse-Body-Bias Assisted Sleep Mode

Koichiro ISHIBASHI<sup>†</sup>, Member, Nobuyuki SUGII<sup>††</sup>, Shiro KAMOHARA<sup>††</sup>, Nonmembers, Kimiyoshi USAMI<sup>†††</sup>, Hideharu AMANO<sup>††††</sup>, Senior Members, Kazutoshi KOBAYASHI<sup>†††††</sup>, and Cong-Kha PHAM<sup>†</sup>, Members

**SUMMARY** A 32bit CPU, which can operate more than 15 years with 220mAH Li battery, or eternally operate with an energy harvester of in-door light is presented. The CPU was fabricated by using 65nm SOTB CMOS technology (Silicon on Thin Buried oxide) where gate length is 60nm and BOX layer thickness is 10nm. The threshold voltage was designed to be as low as 0.19V so that the CPU operates at over threshold region, even at lower supply voltages down to 0.22V. Large reverse body bias up to -2.5V can be applied to bodies of SOTB devices without increasing gate induced drain leak current to reduce the sleep current of the CPU. It operated at 14MHz and 0.35V with the lowest energy of 13.4 pJ/cycle. The sleep current of 0.14 $\mu$ A at 0.35V with the body bias voltage of -2.5V was obtained. These characteristics are suitable for such new applications as energy harvesting sensor network systems, and long lasting wearable computers. *key words: microprocessor, low power design*

# 1. Introduction

Perpetuum mobile computing is one of the key technologies to achieve trillion sensor universe, in which sensors along with super low power micro-controller unit (MCU) operate with harvesting energy or small coin batteries without maintenance. The super low power MCU should consume very tiny energy not only in operation mode but in sleep mode. When the average power of the MCU is less than the average harvesting power, the sensor nodes can operate eternally. This paper describes the first CPU which attains the conditions above by using the key technology called silicon on thin buried oxide (SOTB). As a step forward from the previous papers on the SOTB technology itself [1]–[3], [9], [10], this paper focuses on 32bit CPU implemented with the SOTB. The contribution of this paper is summarized as follows.

(1) This paper shows the first practical CPU implementation with the SOTB technology. Additional evaluation results, a comparison to other competitors and discussion for perpetuum mobile computing are added to the extended ab-

Manuscript revised February 25, 2015.

<sup>†</sup>The authors are with The Univ. of Electro-Communications, Chofu-shi, 182–8585 Japan.

<sup>††</sup>The authors are with Low-power Electronics Association & Project (LEAP), Tsukuba-shi, 305–8569 Japan.

<sup>†††</sup>The author is with Shibaura Inst. of Tech., Tokyo, 135–8548 Japan.

<sup>††††</sup>The author is with Keio Univ., Yokohama-shi, 223–8522 Japan.

<sup>+++++</sup>The author is with Kyoto Inst. of Tech., Kyoto-shi, 603–8335 Japan.

DOI: 10.1587/transele.E98.C.536

stract paper [4] which is the basis of the paper.

(2) This paper also shows the chip with practical size of logic gates and memory cells. Although some specialized chips with practical size (an FPGA [11] and an accelerator [12]) with the SOTB were reported, no report has been done for common chips with logic gates and memory cells.

This paper is organized as follows. Section 2 describes the structure of 65nm SOTB devices for the fabrication of the CPU. Then in Sect. 3, we will introduce the structure and circuits of the CPU. Characteristics of the fabricated CPU are evaluated in Sect. 4 followed by the discussion in Sect. 5, and Sect. 6 concludes this paper.

# 2. SOTB Structure and Advantage for Low Power Micro Controller Unit (MCU)

The CPU was fabricated by using the 65nm SOTB CMOS technology.

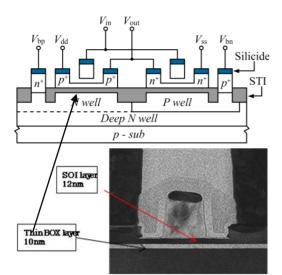

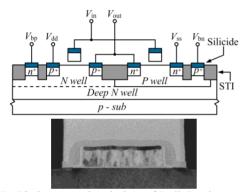

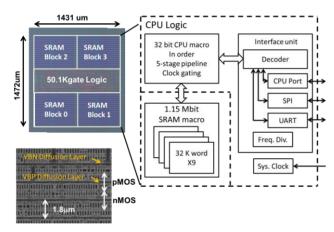

The technology consists of two kinds of devices, one is SOTB devices whose gate length is 60nm for core logic and SRAM (Fig. 1 (a)), and the other is bulk devices (Fig. 1 (b)) whose gate length is 400nm for IO circuits. In the structures of 65nm SOTB as shown in Fig. 1 (a), the SOTB devices has an SOI layer thickness of 12 nm [1]. The specification of each region is summarized in Table 1. The BOX layer and gate oxide thicknesses are 10-and 2.0 nm, respectively. The body biases for NMOS "VBN" and PMOS "VBP" are applied from the Pwell and Nwell, respectively. Since Pwell and Nwell have neither source nor drain junctions due to dielectric isolation by the BOX layer, we can apply large reverse body bias up to -2.5V, which corresponds to the limitations on junctions between the Pwell and the Nwell. The original threshold voltage at body bias of 0V can be decreased to 0.20V for NMOS and 0.19V for PMOS to attain low voltage and fast operation of the CPU.

Thanks to the thin BOX layer, the body bias coefficients  $\gamma$  of the SOTB devices are so large [2]. We can apply large reverse body bias (RBB) to both NMOS and PMOS devices, as shown in the equation below.

$$VBB = VBN = VDD - VBP,$$

(1)

where VBN is body bias of NMOS and VBP is that of PMOS transistors. The value " $\gamma$ " is defined in the following equation.

$$\gamma = \Delta V th / |\Delta VBB| \tag{2}$$

Manuscript received October 20, 2014.

(a) Cross-sectional view of Core and SRAM regions of 65nm SOTB technology

(b) IO Cross-sectional view of Bulk Region

**Fig. 1** Structures of devices and photomicrographs of the IO Region and Core and SRAM regions of 65nm SOTB technology.

| Table 1 | Specifi | cation | of IO | and | Core | Region |

|---------|---------|--------|-------|-----|------|--------|

|---------|---------|--------|-------|-----|------|--------|

| 1 0                                   |  |  |  |  |

|---------------------------------------|--|--|--|--|

| 3.3V Lg=400nm, Tsion=7.5nm, Twin Well |  |  |  |  |

| 0.2-1.2V Lg=60nm, Tsion=2.0nm,        |  |  |  |  |

| TSOI=12nm, TBOX=10nm, Triple Well     |  |  |  |  |

| VTP/VTN(VBB=0)=0.20V/0.19V(Logic)     |  |  |  |  |

| =0.24V/0.22V(Memory)                  |  |  |  |  |

| 7 metal(5 fine, 2 Semiglobal), 1 AL   |  |  |  |  |

|                                       |  |  |  |  |

The value can be increased to 150 mV/V, which is almost three times higher than bulk devices at the same technology node.

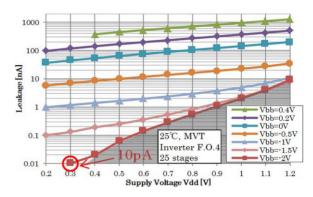

Leakage which flows on an F.O 4 25-stage ring oscillator of inverters was measured as shown in Fig. 2 [3]. When we applied RBB, the leakage monotonically decreased without increasing GIDL (Gate Induced Drain Leakage) except for the shaded region. The GIDL current was smaller than the bulk devices of the same 65-nm technology. The GIDL current reduction for SOTB is easier than bulk because of its simple doping profile, that is, no halo implants is necessary [14]. The  $I_{ds}$ - $V_{gs}$  characteristics of SOTB transistor at  $V_{bb} = -2$  V (not shown) indicate that the subthreshold current dominates at  $V_{ds} = 0.4$  V or lower whereas GIDL dom-

**Fig.2** Measured leakage of a ring oscillator on SOTB devices. The ring oscillator consists of 25-stage FO4 inverters. The shadow region shows the area where influence of GIDL current appears.

inates the off-current at  $V_{ds} = 1.2$  V. We can thus decrease the leakage down to 10pA at a supply voltage of 0.3V and VBB of -2V on the 100 -inverter ring oscillator.

# 3. Structure and Circuit for 32 bit CPU

# 3.1 V850EStar CPU

A 32 bit microcontroller with a core compatible to the V850Estar [13] for signal processing, car electronics and digital servo motor control was implemented. It has RISC instruction set including operations for multiplies, saturation calculations, and bit manipulations. 5-stage standard in-order pipeline can execute most of instructions in a clock cycle. Here, instead of using the cache memory, local data memory was provided, and instructions are fetched from the memory outside the chip.

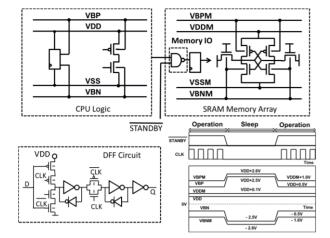

Structure of power lines, FF circuits, and power line operating waveforms of CPU are shown in Fig. 3. The power lines for CPU logic and SRAM were separated [4]. As for the CPU logic, VDD and VSS are power lines, and VBN and VBP are body biases for NMOS and PMOS, respectively. The VBB for logic was tuned to -0.5 V and that for SRAM was tuned to -1.0 V so as to attain minimum energy per cycle value. As for the SRAM memory array, supply voltage of SRAM, VDDM, was 0.1V higher than VDD to attain stable operation of SRAMs. In order to prevent leakage on the boundary between SRAM array and CPU logic, memory IO circuits that consist of NAND gates were introduced. Clocked CMOS input type DFF was introduced to attain low voltage operations of logic circuits.

We confirmed the data retention in SRAM fabricated by our SOTB technology under reverse body bias condition at  $V_{dd}$  less than 0.4 V [1]. The data stored in the DFF is thus not gone in standby mode when the large body bias is applied. This means that we need neither extra back up latch [5] nor retention FF [6] to restore the data during standby. As soon as the mode of the CPU changes from sleep to operation mode, the CPU can resume operation by using data stored in the FF latch. This is an advantage of the body bias techniques from the viewpoints of compatibility

**Fig. 3** Structure of power lines of CPU, circuit of DFF, and schematic operating waveforms of CPU.

**Fig.4** CPU chip photomicrograph, CPU structure, and SEM photomicrograph of the region where primitive logic cells are paved.

with legacy design and area overhead.

A photomicrograph of the CPU core and the chip architecture are shown in Fig. 4. The CPU core consists of in-order 5-stage pipeline, and 4 blocks of 32Kword X 9 data memory. Instructions are fed from an instruction memory out of the chip through the IO circuits. The CPU core consists of 50.1K gate logic and 1.15 Mbit 6T SRAM arrays, and occupies 2.1 mm<sup>2</sup>. The CPU chips were also fabricated by 65nm bulk-only CMOS using the same mask pattern to compare characteristics of CPUs for SOTB and Bulk devices.

Layout pattern of the region where primitive cells are located is also shown in Fig. 4. The cell height is 9 grids of 200nm M1 pitch, which corresponds to 1.8  $\mu$ m height. We use silicided diffusion layers for VBN and VBP wires. Since the diffusion layers run horizontally without any gap, noise occurred in the primitive cells in operation mode can be reduced, thereby obtaining stable operations of the circuits, even applying RBB in operation mode.

# 3.2 Low Power Body Bias Generator

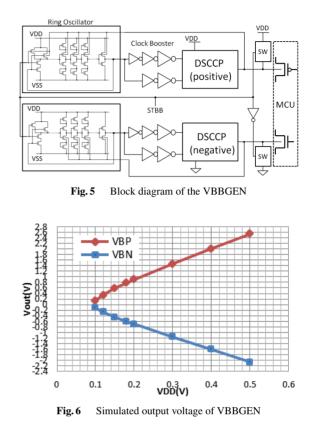

Low power body bias generator is necessary to reduce the standby current of the CPU, so that a large body bias voltage should be generated from the low supply voltages. Also the power consumption of the body bias generator itself must be low.

We have proposed body bias generator (VBBGEN), where body bias is generated by using Dynamic Substrate Controlled Charge Pump (DSCCP) [15]. The block diagram of the VBBGEN is shown in Fig. 5. The VBBGEN consists of Ring Oscillator, Clock Booster, and DSCCP. The outputs of the DSCCPs correspond to the body bias voltages (VBN and VBP) where VBN and VBP are connected to bodies of NMOS and PMOS in the Ring Oscillators so that the Ring Oscillators run and drive the DSCCP until the VBN and VBP reached to the predetermined voltages. As shown in Fig. 6, large |VBN| and VBP-VDD voltages of around 2.1V were obtained by the VBBGEN at a supply voltage of 0.5V by simulation.

Simulated current consumption of the VBBGEN was 361nA at a load current of 10 nA. Since load current of SOTB devices are extremely low due to the BOX insulation, the current consumption of the VBBGEN can be further reduced to sub 100 nA level.

#### 3.3 Bias Control

Another issue is how to find optimal VDD, VDDM, VBB

and VBBM. There are a lot of researches to find the supply voltage and Vth for the smallest energy consumption [16]. In the CPU built with SOTB, *Vth* can be controlled by VBB/VBBM. By applying expressions in [17], we can find the optimal ones. However, from the viewpoint of practical usage of CPUs, a certain performance is needed. Thus, the optimal VDD, VDDM, VDD and VBBM must achieve the smallest energy consumption with a required clock frequency. Su and his colleague evaluated it for an accelerator using SOTB [12], and the same approach is useful to find such optimal parameters for CPUs.

The method of controlling both the optimum VBB and VBBM includes mainly these two points: (1) memory stability and (2) leakage/delay optimization.

Regarding the memory stability, we can control VBBM of both p-type (load) and n-type (access and driver) transistors independently against temperature and process variation. We demonstrated that the SRAM stability at 0.32 V is secured against the temperature variation by the back biasing [1].

Regarding the leakage/delay optimization, balancing the p- and n-type transistors by independent (VBP and VBN) back-bias voltage control is important. It is also essential for the SRAM stability. We demonstrated that the delay can be controlled over the temperature variation by the back biasing [18]. The leakage can be controlled because  $V_{\text{th}}$  can be controlled to be nearly constant over the temperature variation although a slight increase can be observed due to increasing the S factor at elevated temperatures.

#### 4. Evaluation of the 32 bit CPU

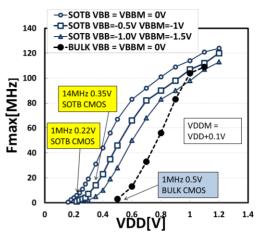

Recently low power and low voltage operation of CPU is attained by lowering the supply voltage below threshold voltages of MOSFETs [7]. However, the CPU cannot operate fast due to sub threshold operation of logic circuits. The threshold voltages of CPU on SOTB can be decreased so that the CPU operates at over-threshold region, thereby operating at fast speed even at lower supply voltages.

Fmax of 32bit CPU core which was fabricated by bulk and SOTB processes are shown in Fig. 7. A simple test program to check the CPU functions including ADD instruction and the data memory read/write operations was carried out for the measurements. While instructions were supplied from the ROM outside the chip, data were stored in the data memory inside the chip. CPU on bulk CMOS operated down to 0.5V however the Fmax was only 1MHz. The maximum operating frequency of CPU on SOTB changed depending on VBB. At the optimized VBB condition, where VBB was -0.5V and VBBM was -1.0V, the CPU operated down to 0.22V and 1MHz. This is the lowest supply voltage of CPU ever reported [5]. The CPU on SOTB also operated at 14MHz at 0.35V and 46MHz at 0.5V. The CPU on SOTB operated at lower supply voltage than bulk by 0.28V, and operated faster by a factor of X46 at a supply voltage of 0.5V.

The power consumption of synchronous logic circuit is

**Fig.7** Maximum operating frequency of CPUs by bulk and SOTB, where VBB is parameterized for SOTB.

expressed as Eq. (3).

$$P = P_{AC} + P_{DC} = 1/2AnCV^2f + nI_LV$$

(3)

Where A is activity ratio of the circuit, n is number of logic gates, C is average capacitance of each gate, V is supply voltage, f is operating frequency, and  $I_L$  is leakage of each gate. When we divide the power by cycle frequency, we can obtain energy per cycle value as shown as Eq. (4)

$$\mathbf{E} = \mathbf{E}_{\rm AC} + \mathbf{E}_{\rm DC} = 1/2 \mathrm{AnCV}^2 + \mathrm{nI}_{\rm L} \mathrm{V/f} \tag{4}$$

The energy per cycle value consists of AC energy and DC energy. AC energy can be reduced as supply voltage is reduced, however, the DC energy will increase because frequency reduces rapidly. The energy per cycle value normally has a minimum value called as Emin [19], [20].

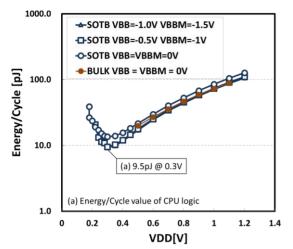

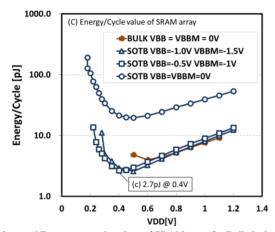

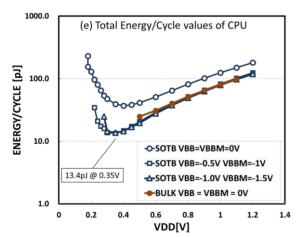

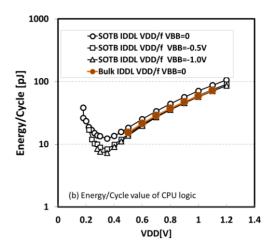

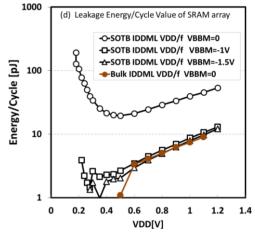

Measured energy per cycle of the 32bit CPU is shown in Fig. 8. The body biases, VBN, VBP, VBNM, and VBPM were externally applied. The leakage currents of these terminals were measured and they were less than the resolution of the measurement instrument, which is less than 20 nA. The values do not affect the total energy per cycle values. Figure 8 (a) shows the energy/cycle value of CPU logic, while Fig. 8 (b) shows the leakage energy/cycle value of CPU logic. Here, cycle means clock cycle used in the CPU. Figure 8 (c) shows the energy/cycle value of SRAM array, while Fig. 8 (d) shows the leakage energy/cycle value of SRAM array. The total energy/cycle value is shown in Fig. 8 (e).

Since leakage increases exponentially as drain voltage increases as shown in Fig. 2, and original threshold voltage of SOTB is quite low, the leakage energy becomes dominant factor even at higher supply voltages. As shown in Fig. 8 (b) and Fig. 8 (d), Leakage-energy/cycle value shown in the 2<sup>nd</sup> factor in Eq. (4) exhibits minimum values, and it dominates the total energy/cycle values of the CPU. The supply voltages which give Emin appeared to be almost the same at different VBB conditions, and it comes from that leakage energy becomes dominant factors.

(a) Measured Energy per cycle values of CPU logic for Bulk devices and SOTB devices.

(c) Measured Energy per cycle values of SRAM array for Bulk devices and SOTB devices.

(e) Measured Total energy per cycle values of CPU for Bulk devices and SOTB devices.

Fig. 8 Measured Total energy per cycle valves.

The lowest Emin of 9.5pJ/cycle was obtained at a supply voltage of 0.3V and VBB of -1.0V as for the CPU logic in Fig. 8 (a).

As for the SRAM shown in Fig. 8 (d), DC energy was

(b) Measured Leakage-energy per cycle values of CPU logic for Bulk devices and SOTB devices. Clock is stopped during the measurement.

(d) Measured Leakage-energy per cycle values of SRAM array for Bulk devices and SOTB devices. Clock is stopped during the measurement.

more dominant at VBB = 0V even at high supply voltages. Therefore larger body bias should be added to reduce energy/cycle value. The lowest value of 2.7pJ/cycle was obtained at VBBM of -1.5V and a supply voltage of 0.5V as

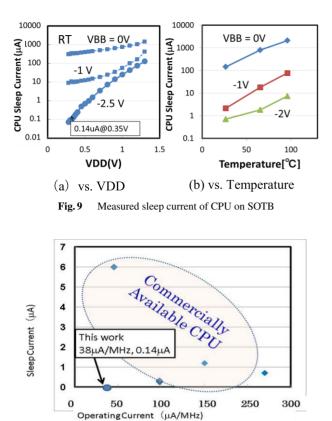

Fig. 10 Mapping for sleep current vs operating current

shown in Fig. 8 (c).

The Emin of CPU was obtained when VDD was 0.35V at VBB of -1.0V and VDDM was 0.45V at VBBM of -1.5V. It reached to 13.4pJ/cycle. Even when the CPU operated with Emin at 0.35V, it operated at high frequency of 14MHz, while CPU in the paper [7] operated at only 73KHz at the Emin condition. Therefore, the CPU on SOTB can achieve high performance with the smallest energy per cycle value.

Sleep current of the 32bit CPU under large reverse VBB is shown in Fig. 9 (a). We reduced the sleep current by more than three orders of magnitude when the VBB of -2.5V was applied. The sleep current of 0.14  $\mu$ A was obtained at a supply voltage of 0.35V. The sleep current reduction was effective even when the temperature increased as shown in Fig. 9 (b). Therefore, we can prevent thermal runaway which is caused by positive feedback of leakage and temperature rise due to Joule heating.

The operating and sleep current of CPU are normally the trade-off on MCUs. Figure 10 shows a comparison of sleep current and operating current of commercially available MCU and the proposed CPU. Table 3 shows the specification of CPUs under comparison. The proposed CPU can reduce both sleep current and operating current simultaneously, and it can reach  $38\mu$ A/MHz operating current and  $0.14\mu$ A sleep current.

Table 2

Conditions for obtaining Perpetuum mobile CPU

| Operation time/<br>Sleep Time | Average<br>Current<br>(μΑ) | 220mAH<br>Battery<br>Life | Capable Harvest<br>Power<br>(cm-2)  |

|-------------------------------|----------------------------|---------------------------|-------------------------------------|

| 100ms/30s                     | 1.66                       | 15 Year                   | Ambient Linght<br>In door (10µW)    |

| 100ms/3s                      | 13.1                       | 1.9 Year                  | Thermal Energy<br>(30µW)            |

| 100ms/300ms                   | 127                        | 72 day                    | Vibration<br>(100µW)                |

| Always in operation           | 380                        | 24 day                    | Ambient light<br>Out door (10000µW) |

@ 380µA active current at 10MHz, 0.14µA sleep current 1%/Year battery self discharge

|                           | This work                                                     | Ref [8]                                                    | Ref[7]                       |

|---------------------------|---------------------------------------------------------------|------------------------------------------------------------|------------------------------|

| Technology                | 65nm SOTB<br>CMOS                                             | 32nm<br>CMOS                                               | 0.18um<br>CMOS               |

| IP                        | 32bit CPU, 50Kgate                                            | IA-32 processor                                            | 32bit M3                     |

| VDD range                 | <u>0.22V(Vmin)</u> – 1.2V                                     | 0.28V – 1.2V                                               | 0.35V – 0.75V                |

| SRAM                      | 1.15 Mbit<br>Data memory<br>6T High density [1]<br>VDD + 0.1V | 8KByte Code \$<br>8KByte Data \$<br>10T<br>0.55V operation | 24Kbit<br>(Retention)<br>10T |

| Energy/Cycle              | <u>13.4pJ 0.35V</u>                                           | 170pJ 0.45V                                                | 28.9 pJ 0.4V                 |

| Frequency                 | 1MHz 0.22V<br>4MHz 0.28V<br>14MHz 0.35V                       | 3MHz 0.28V<br>915MHz 1.2V                                  | 73kHz 0.4V<br>/1MHz 0.5V     |

| Sleep Current,<br>Leakage | 0.14 μΑ                                                       | -                                                          | 100pW/460pW                  |

Table 3

Comparison with related work

#### 5. Discussion on Perpetuum Computing

We have estimated average current and battery life when the CPU is used with a 220 mAH battery (equivalent to CR2032 Li coin battery), and compatible energy harvesters as shown in Table 2. When the CPU becomes sleep mode for 30s after it operates for 100ms periodically on SOTB, the estimated life of the battery becomes 15 years. This life is longer than that uses commercially available CPUs at any operation-sleep time ratio. The CPU operates at average current of 1.66  $\mu$ A, and it eternally continues to operate even with the ambient light energy harvesters that generate  $10\mu$ A/cm<sup>2</sup> indoors. Therefore, the proposed CPU can realize the Perpetuum mobile computing.

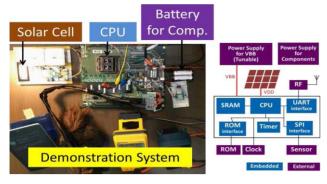

In order to make sure the operation of the Perpetuum computing, we made a demonstration system as shown in Fig. 11. The system has a small Si solar cell of 3cm by 6cm for the supply of the chip including CPU, SRAMs, and IOs. The acceleration sensor detected the motion of a horse doll and the CPU could operate with the power from indoor light intensity. So the demo system proves that the CPU can operate eternally as long as indoor light ists.

#### 6. Conclusions

A 32bit CPU which can operate eternally with an energy

Fig. 11 A picture and block diagram of the demonstration system.

harvester was demonstrated. The CPU was fabricated by using 65nm SOTB CMOS technology. Large reverse body bias up to -2.5V can be applied to bodies of SOTB in sleep mode. It operated at 14MHz and 0.35V with the lowest energy of 13.4 pJ/cycle. The sleep current of 0.14 $\mu$ A at 0.35V with VBB of -2.5V was obtained. These characteristics are suitable for such new applications as energy harvesting sensor network systems, and long lasting wearable computers.

## Acknowledgments

This work was performed as "Ultra-Low Voltage Device Project" funded and supported by the Ministry of Economy, Trade and Industry (METI) and the New Energy and Industrial Technology Development Organization (NEDO). The chip design was supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys, Inc, Cadence Design Systems, Inc, and Mentor Graphics, Inc.

## References

- Y. Yamamoto, H. Makiyama, H. Shinohara, T. Iwamatsu, et al., "Ultralow-Voltage Operation of Silicon-on-Thin-BOX (SOTB) 2Mbit SRAM Down to 0.37 V Utilizing Adaptive Back Bias," VLSI Technology Symposium, pp.T212–213, June 2013.

- [2] H. Makiyama, K. Horita, T. Iwamatsu, H. Oda, N. Sugii, Y. Inoue, and Y. Yamamoto, "Design Consideration of 0.4V-Operation SOTB MOSFET for Super Low Power Application," 2011 Int. Meeting for Future of Electron Devices, Kansai, pp.42–43, 2011.

- [3] S. Morohashi, N. Sugii, T. Iwamatsu, S. Kamohara, Y. Kato, C.-K. Pham, and K. Ishibashi, "A 44μW/10MHz Minimum Power Operation of 50K Logic Gate using 65nm SOTB Devices with Back Gate Control," 2013 S3S Conference, Monterey, CA, pp.1–2, Oct. 2013.

- [4] K. Ishibashi, N. Sugii, K. Usami, H. Amano, K. Kobayashi, C.-K. Pham, H. Makiyama, Y. Yamamoto, H. Shinohara, T. Iwamatsu, Y. Yamaguchi, H. Oda, T. Hasegawa, S. Okanishi, H. Yanagita, S. Kamohara, M. Kadoshima, K. Maekawa, T. Yamashita, D.-H. Le, T. Yomogita, M. Kudo, K. Kitamori, S. Kondo, and Y. Manzawa, "A Perpetuum Mobile 32bit CPU with 13.4pJ/cycle, 0.14μA Sleep Current using Reverse Body Bias Assisted 65nm SOTB CMOS Technology," Cool Chips XVII, Yokohama, Japan, pp.1–3, April 2014.

- [5] Y. Kanno, H. Mizuno, Y. Yasu, K. Hirose, Y. Shimazaki, T. Hoshi, Y. Miyairi, T. Ishii, T. Yamada, T. Irita, T. Hattori, K. Yanagisawa, and N. Irie, "Hierarchical Power Distribution with 20 Power Domains in 90-nm Low-Power Multi-CPU Processor," 2007 IEEE International Conference on Integrated Circuit Design and Technology, pp.1–4, 2007.

- [6] O. Ozawa, K. Fukuoka, Y. Igarashi, T. Kuraishi, Y. Yasu, Y. Maki, T. Ipposhi, T. Ochiai, M. Shirahata, and K. Ishibashi, "Low Power SOC Design Using Partial-Trench-Isolation ABC SOI (PTI-ABC SOI) for Sub-100-nm LSTP Technology," 2006 VLSI Circuit Symposium, Honolulu, Hawaii, pp.186–187, June 2006.

- [7] G. Chen, M. Fojtik, D. Kim, D. Fick, J. Park, M. Seok, M.-T. Chen, Z. Foo, D. Sylvester, and D. Blaauw, "Millimeter-Scale Nearly Perpetual Sensor System with Stacked Battery and Solar Cells," ISSCC Dig. Tech. Papers, pp.288–289, Feb. 2010.

- [8] S. Jain, S. Khare, S. Yada, V. Ambili, P. Salihundam, S. Ramani, S. Muthukumar, M. Srinivasan, A. Kumar, S.K. Gb, R. Ramanarayanan, V. Erraguntla, J. Howard, S. Vangal, S. Dighe, G. Ruhl, P. Aseron, H. Wilson, N. Borkar, V. De, and S. Borkar, "A 280mV-to-1.2V Wide-Operating-Range IA-32 Processor in 32nm CMOS," ISSCC Dig. Tech. Papers, pp.66–68, Feb. 2012.

- [9] S. Morohashi, N. Sugii, T. Iwamatsu, S. Kamohara, Y. Kato, C.-K. Pham, and K. Ishibashi, "A 44uW/10MHz Minimum Power Operation of 50K Logic Gate using 65nm SOTB Devices with Back Gate control," Proc. of IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), pp.1–2, 2013.

- [10] N. Sugii, Y. Yamamoto, H. Makiyama, T. Yamashita, H. Oda, S. Kamohara, Y. Yamaguchi, K. Ishibashi, T. Mizutani, and T. Hiramoto, "Ultralow-Power SOTB CMOS Technology Operating Down to 0.4V," J. Low Power Electron. Appl., vol.4, no.2, pp.65–76, 2014.

- [11] M. Hioki, C. Ma, T. Kawanami, Y. Ogasahara, T. Nakagawa, T. Sekigawa, T. Tsutsumi, and H. Koike, "SOTB Implementation of a Field Programmable Gate Array with Fine-Grained Vt Programmablity," J. Low Power Electron., vol.4, no.3, pp.188–200, 2014.

- [12] H. Su, Y. Fujita, and H. Amano, "Body Bias Control for a Coarse Grained Reconfigurable Accelerator Implemented with Silicon on Thin BOX Technology," Proc. of FPL2014, pp.1–6, Sept. 2014.

- [13] http://japan.renesas.com/products/mpumcu/v850/

- [14] T. Ishigaki, R. Tsuchiya, Y. Morita, H. Yoshimoto, N. Sugii, T. Iwamatsu, H. Oda, Y. Inoue, T. Ohtou, T. Hiramoto, and S. Kimura, "Silicon on thin BOX (SOTB) CMOS for ultralow standby power with forward-biasing performance booster," Journal of Solid-State Electronics, vol.53, no.7, pp.717–722, 2009.

- [15] H. Nagatomi, N. Sugii, S. Kamohara, and K. Ishibashi, "A 361nA Thermal Run-away Immune VBB Generator using Dynamic Substrate Controlled Charge Pump for Ultra Low Sleep Current Logic on 65nm SOTB," 2014 IEEE S3S Conference, San Francisco, pp.1–2, Oct. 2014.

- [16] B.H. Calhoun, A. Wang, and A. Chandrakasan, "Modeling and Sizing for Minimum Energy Operation in Subthreshold Circuits," IEEE J. Solid-State Circuits, vol.40, no.9, pp.1778–1786, Spet. 2005.

- [17] S. Nakamura, J. Kawasaki, Y. Kumagai, and K. Usami, "Measurement of the Minimum Energy Point in Silicon on Thin-BOX (SOTB) and Bulk MOSFET," Proc. EUROSOI-ULIS 2015, Bologna, Italy, pp.193–196, Jan. 26-28, 2015.

- [18] H. Makiyama, Y. Yamamoto, H. Shinohara, T. Iwamatsu, H. Oda, N. Sugii, K. Ishibashi, T. Mizutani, T. Hiramoto, and Y. Yamaguchi, "Suppression of die-to-die delay variability of silicon on thin buried oxide (SOTB) CMOS circuits by balanced P/N drivability control with back-bias for ultralow-voltage (0.4 V) operation," International Conference on Electron Devices Meeting (IEDM), pp.33.2.1–33.2.4, 9-11 Dec. 2013

- [19] D. Bol, D. Kamel, D. Flandre, and J.-D. Legat, "Nanometer MOS-FET Effects on the Minimum-Energy Point of 45nm Subthreshold Logic," In Proceedings of the 14th IEEE/ACM International Symposium on Low-Power Electronics and Design, San Francisco, CA, USA, pp.3–8, 19–21 Aug. 2009.

- [20] A.P. Chandrakasan, D.C. Daly, D.F. Finchelstein, J. Kwong, Y.K. Ramadass, M.E. Sinangil, V. Sze, and N. Vermaet, "Technologies for ultradynamic voltage scaling," Proceedings of the IEEE, vol.98, no.2, pp.191–214, 2010.

**Koichiro Ishibashi** received PH. D degree from Tokyo Institute of Technology in 1985. He has been a professor of The University of Electro-Communications, Tokyo, Japan since April 2011. He has served gust professors at Ho Chi Minh City University of Science and Ho Chi Minh City University of Technology since 2012. He is a member of IEICE and a Fellow of IEEE.

**Kazutoshi Kobayashi** received his B.E., M.E. and Ph. D. in Electronic Engineering from Kyoto University, Japan in 1991, 1993, 1999, respectively. Since 2009, he has been a professor at Kyoto Institute of Technology. He was the recipient of the IEICE best paper award in 2009 and the IRPS best poster award in 2013.

**Nobuyuki Sugii** received the B.S., M.S., and Ph.D. degrees from the University of Tokyo. He leads the SOTB (Silicon on Thin Buried Oxide) research group in the Low-power Electronics Device Association & Project (LEAP). Since 2004, he also serves as a visiting professor for the Tokyo Institute of Technology.

**Cong-Kha Pham** received the B.S., M.S., and Ph.D. degrees in 1988, 1990 and 1992, respectively, all from the Sophia University, Tokyo, Japan, in Electrical and Electronics Engineering. Since April 2000, he has been an Associate Professor of the Department of Electronic Engineering at the University of Electro-Communications, Tokyo, Japan. He is a member of the IEEE and IEICE.

**Shiro Kamohara** received the B.S. degree in physics from Keio University in 1986, M.E. degree from University of Tokyo Institute Technology in nuclear engineering in 1988 and Ph.D. from Tokyo metropolitan University in electrical and electronic engineering in 2008. He is a member of Renesas Electronics Corp since 2010. He concurrently served as Semiconductor Leading Edge Technologies, Inc (Selete) since 2006. Now he has doubled as LEAP.

**Kimiyoshi Usami** received Ph.D in electric engineering from Waseda University. He is a professor in the Department of Information Science and Engineering at the Shibaura Institute of Technology. His research interests include energy-aware computing and ultra-lowpower voltage design. He is a member of IEICE and IEEE.

**Hideharu Amano** received a Ph.D in electric engineering from Keio Unviersity. He is a professor of Information and Computer Science at Keio University. His research interests include parallel architecture and reconfigurable computing.