# 重イオン照射測定による FDSOI における FF のソフトエラー耐性の評価

# 一二三 潤 梅原 成宏 丸岡 晴喜 古田 潤 小林 和淑

### †京都工芸繊維大学

E-mail: †{mhifumi,sumehara,hmaruoka,furuta}@vlsi.es.kit.ac.jp, ††kazutoshi.kobayashi@kit.ac.jp

あらまし 微細プロセスではレイアウト構造を変更することで様々な影響が及ぶ.本研究では  $65~\mathrm{nm}$  と  $28~\mathrm{nm}$  の FDSOI プロセスにおいてレイアウト構造の異なる FF を試作,重イオン照射測定を実施しソフトエラー耐性への影響を評価する. $65~\mathrm{nm}$  ではレイアウト構造によるソフトエラー耐性への影響は見られなかったが, $28~\mathrm{nm}$  ではラッチを構成するトランジスタ間の距離が広いレイアウトで,高い LET を持つ重イオンを照射した場合のソフトエラー耐性が大きく低下することが分かった.

キーワード ソフトエラー, 重イオン, FDSOI, フリップフロップ

Evaluation of Soft Error Rates of Flip Flops on FDSOI by Heavy Ions

Masashi HIFUMI $^\dagger,$ Shigehiro UMEHARA $^\dagger,$ Haruki MARUOKA $^\dagger,$ Jun FURUTA $^\dagger,$  and Kazutoshi

# KOBAYASHI†

† Kyoto Institute of Technology

E-mail: †{mhifumi,sumehara,hmaruoka,furuta}@vlsi.es.kit.ac.jp, ††kazutoshi.kobayashi@kit.ac.jp

**Abstract** We evaluate tolerance for soft errors of FFs on 65/28 nm FDSOI processes. We fabricated three different layouts of non-redundant FFs with same circuit area and carried out heavy-ion beam tests. Radiation hardbess is influenced by layout structures. Heavy ion irradiation reveals that the separated diffusion layout structure in 28 nm have 2x more cross section than the shared diffusion one by the irradation of 40 MeV-cm<sup>2</sup>/mg ions. On the other hand flip-flops in 65 nm have almost equivalent cross sections at any energy. It is due to flucations of soft error tolerance caused by effects of layout structures of the highly-scaled scaled 28 nm node.

Key words Soft Error, Heavy Ion, FDSOI, Flip Flop

### 1. 序 論

近年の半導体デバイスの微細化に伴い,信頼性の問題が深刻化しており,中でも放射性起因で発生する一次故障(ソフトエラー)は,現在地上でも無視できない問題となっている[1].ソフトエラーはデバイスの再起動により動作を回復することができるが,自動車,医療機器,航空機などの一度のエラーが人命を左右しかねない高い信頼性を求められる機器ではソフトエラー対策は必須である[2].

一般的に,微細化により同面積のチップあたりのソフトエラー率は高くなるが[3],SOI (Silicon on Insulator) 構造のデバイスでは,ソフトエラーの有感領域も小さくなることでソフトエラー率は低下している[4].

微細化デバイスでは、レイアウト構造を変更することに様々な利点がある、ソフトエラーの要因の一過性のパルスを減衰させる、パルス減衰効果というものがある[5].トランジスタが

近接して配置されているとき,チャージシェアリングが発生することで値の反転が起こりにくくなる.また,STI (Shallow Torench Isolation) による圧縮ストレスを用いて CMOS のパフォーマンスを向上する技術も存在する [6], [7]. しかし,STIによる意図しない圧縮ストレスはソフトエラー耐性に影響を及ぼすと考えられる.

本稿では、65 nm と 28 nm の 2 種類の FDSOI (Fully Depleted SOI) プロセスにおいて、テストチップを試作し、フリップフロップ (FF) の持つソフトエラー耐性を重イオン照射測定を実施する.また、レイアウト構造の違いがソフトエラー耐性に与える影響を確認するため 3 種類の異なるレイアウトを持つ FF を設計した.第 2 節では,ソフトエラーの要因,種類,対策及び FDSOI,レイアウト構造の CMOS への影響について述べる.第 3 節では,重イオン照射ソフトエラー測定の内容,測定対象,測定条件について述べる.第 4 節では,測定結果,第 5 節で考察を述べる.第 6 節で本稿の結論を述べる.

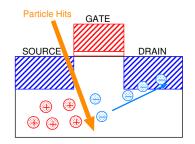

図 1 ソフトエラー発生機構

### 2. ソフトエラー

ソフトエラーとは,集積回路に粒子線等が突入することにより電子正孔対が生成され,一時的にラッチの保持値が反転する現象である.物理的損傷,故障によって永久に正常動作を行えないハードエラーとは異なり,一過性のエラーであるためデバイスの再起動を行うことで正常動作に復帰が可能である.しかし,常に正常動作することが求められる航空機,医療機器,人工衛星などでは無視できない問題であり,対策は必須である.ソフトエラーの発生機構を図1に示す.粒子線が集積回路に突入することによって基板部に電子正孔対が発生,ドレイン領域に電子が収集され,電位が変化し保持値が反転する(電荷収集起因).基板に残留する正孔は基板の電位を上昇させ,基板・ソース・ドレインからなる寄生バイポーラトランジスタが ON 状態となり.保持値を反転させる(寄生バイポーラ効果).

#### 2.1 Single Event Effect

先に述べた粒子線等が LSI に突入することによって発生する一時的もしくは定常的な故障を総称して SEE (Single Event Effect) と呼ぶ . SEE はいくつかの種類があり , 代表的なものとしては SEU (Single Event Upset) , SET (Single Event Transient) , SEL (Single Event Latch-up) 等がある [8] .

# 2.1.1 Single Event Upset

SRAM やラッチ等のデータを保持するループ状の構造に粒子線などが衝突することによって直接的に保持しているデータが反転する現象である. 反転する bit 数が 1 つの場合は SBU (Single Bit Upset), 2 つ以上の場合は MBU (Multiple Bit Upset) と分類される. 微細化による電源電圧の低下に伴い,保持データが反転するために必要な電荷量が減少しているため発生する確率も上昇する傾向にある.

### 2.1.2 Single Event Transient

SRAM やラッチのデータ保持部以外で,粒子線の突入により生じた電子正孔対がパルスを発生させる.このパルスが CLK の立ち上がり時にラッチに取り込まれることで保持データが反転する現象である.このパルス波は SET パルスと呼ぶ.ラッチ部以外で SET パルスが発生した場合,パルスがラッチに取り込まれない限りエラーは発生しない.SET パルスは CLK の周期が短くなるとデータ保持部へ取り込まれる確率が上昇する.

#### 2.1.3 Single Event Latch-up

CMOS 構造には回路構成の組み合わせにより寄生サイリスタが存在する.そのサイリスタ (pnpn 型, npnp 型) に粒子線

が突入し,電子正孔対が生成され ON 状態になることで,本来 意図しない経路で電流が流れる.再起動によって回復するが,電流が増加するとデバイスが故障する永久故障 (ハードエラー) となる.

#### 2.2 ソフトエラー対策

ソフトエラーの対策には回路レベル,デバイスレベル,システムレベルの対策が存在する.ここではデバイスレベルの対策として SOI (Silicon On Insulator) について説明する.

#### 2.3 SOI

SOI はプレーナ型の CMOS 回路構造の一種である.シリコン基板とトランジスタ (表面シリコン) の間に, 絶縁物 (BOX, Buried OXide) の層を構築した構造である. BOX 層には主に,  $SiO_2$  やサファイアが用いられる.

#### 2.3.1 SOI の利点

BOX 層上にトランジスタが作成されることにより、短チャネル効果を抑制することができ、さらにドレイン・ソースと基板間の接合容量も小さくなる、従来のバルク構造では粒子線の突入によって発生した電荷はドレイン領域に収集される、それに対し、SOI ではボディで発生した電荷はドレイン領域に収集されるが、BOX 層以下の基板で発生した電荷は絶縁膜層によって遮られるためドレイン領域では収集されず、バルク構造と比較して高いソフトエラー耐性を持つ、

### **2.3.2** SOI の欠点

SOI の欠点としてセルフヒーティングが挙げられる.BOX 層が断熱材の役割をしてトランジスタの動作により発生した熱が基板に逃げずトランジスタに蓄積する.それによってトランジスタが高温になり,電流が減少し動作が遅くなる.特にトランジスタのオンオフが多いクロックバッファ,I/O トランジスタで問題となる.またバルクプロセスに比べて ESD 耐性 (静電気による LSI の破壊耐圧) が低い.トランジスタと基板やウェルへの接合がないために,静電気による電流が入った時に,電流が逃げる場所が保護トランジスタのみになるためデバイスが壊れやすい.ウェハ処理中や組み立て時に発生する静電気を抑えることで対策出来る.

### 2.4 FDSOI

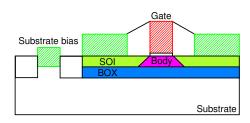

SOI には空乏層が BOX 層まで達しない PDSOI (Partially Depleted SOI) と空乏層が BOX 層まで達する FDSOI (Fully Depleted SOI) が存在する. FDSOI は BOX 層を持たない従来のバルク構造とは異なり,ボディに不純物を添加しないで済むために特性のばらつきを抑えやすい. ここでは試作に用いた2種類の FDSOI プロセスについて説明を行う. FDSOI の断面図を図2に,試作した2種類の FDSOI プロセスのパラメータを表1に示す. FDSOI は非常に薄いボディ層を持ち,不純物なしで製造できるため,ばらつきを低減できる. さらに,基板バイアスを制御でき,ボディの寄生容量を抑え,ボディを流れる電子を効率的に制御するため,リーク電流が大幅に低減する.基板に正の電圧をかける FBB (Forward Body Bias) では高速動作を可能とする[9].

SOTB SOTB (Silicon On Thin BOX) とは,65 nm のプロセスノードを持ち,通常のSOI では約100 nm あるBOX 層が

図 2 FDSOI 構造の断面図

$10~\mathrm{nm}$  程度の絶縁膜に変更したプロセスである [10] . これにより,基板バイアスによるしきい値電圧の制御が他のプロセスと比較して効きやすい.

**UTBB** UTBB (Ultra Thin Body and BOX) は,28 nm のプロセスノードを持ち,BOX 層に加えて空乏層部のボディも同様に薄くした構造である.BOX 層の厚さは25 nm,SOI 層は7 nm である.UTBB のゲートには従来のプロセスで使用されていた $SiO_2$ とは異なり $HfO_2$ (ハフニウム酸化膜)系の材料を使用したHigh-k Metal Gate が用いられる.

### 2.5 レイアウト構造が与える影響

トランジスタはレイアウト構造を変化させることで様々な影響を受ける.

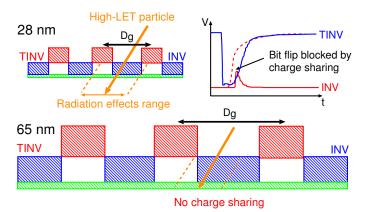

パルス軽減効果 パルス軽減効果とは,ソフトエラーの要因の一つである一過性のパルスを軽減する効果である[5].ラッチ回路を構成するインバータとトライステートインバータ間の距離を短くすることでチャージシェアリングが発生し,値の反転が発生しにくくなる.

STI による圧縮ストレス STI (Shallow Trench Isoration) とは,隣り合うトランジスタを電気的に分離させる技術で,寄生トランジスタによる漏れ電流を抑えるために埋め込まれる酸化膜であり,隣接するトランジスタに圧縮ストレスを与える.レイアウト上における横方向のチャネル長を圧縮するストレスは,PMOS のパフォーマンスを向上(正孔の移動度上昇)させ,NMOS のパフォーマンスを減衰(電子の移動度を減少)させる [11], [12].

### 3. 重イオン照射ソフトエラー測定

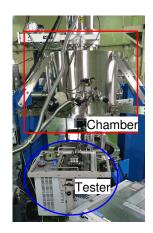

重イオンは大気と磁場により遮断されるため地上には存在しない.実測は真空状態を作るチャンバー内部で行う必要がある. 宇宙空間では Fe が主要因とされているが,実測では希ガス類をサイクロトロン加速器を用いて加速して照射を行う.

# 3.1 測定対象

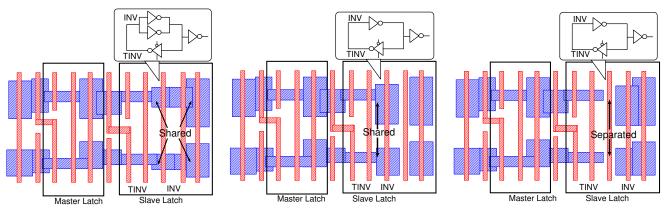

### 3.1.1 設計した FF のレイアウト

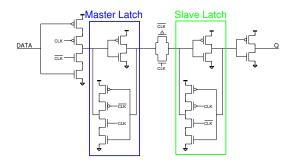

3 種類の異なるレイアウトをもつ DFF (図 3) を 28 nm UTBB, 65 nm SOTB の 2 つのプロセスで試作した.設計したレイアウトを図 4 に示す.同一プロセス内においてそれぞれのレイア

表 1 65 nm SOTB と 28 nm UTBB のパラメータ

| 2 1 00 mm 50 1B C 20 mm 6 1BB 07 (57) |           |             |            |  |

|---------------------------------------|-----------|-------------|------------|--|

|                                       | ゲート長 [nm] | Body 層 [nm] | BOX 層 [nm] |  |

| SOTB                                  | 65        | 12          | 10         |  |

| UTBB                                  | 28        | 7           | 25         |  |

図 3 一般的な FlipFlop (DFF) の回路図

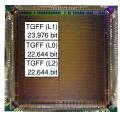

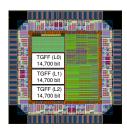

(a) 65 nm SOTB (3 mm×3 mm)

(b) 28 nm UTBB (1 mm×1 mm)

図 5 設計したテストチップ

図 6 重イオン照射用の真空チャンバーとテスタ

ウトの持つ回路図,回路面積は等しくなるように設計をする.これにより,レイアウト構造の変更が FF のソフトエラー耐性に与える影響,およびプロセスの微細化によるソフトエラー耐性への影響を確認することができる.L2 のレイアウトではラッチを構成するインバータ,トライステートインバータ間の距離が広く,STI が埋め込まれているため,パルス軽減効果が発生しないと予想される.

### 3.1.2 テストチップ

実際に設計した FF のレイアウトを搭載したチップと各 FF で構成されているシフトレジスタの段数を図 5 に示す.

### 3.2 測定施設

重イオン照射ソフトエラー測定は高崎量子応用研究所 (TIARA) で行った.図 6 に,実際に使用した測定装置を示す.実験で照射した重イオンの種類は,ネオン (Ne),アルゴン (Ar),クリプトン (Kr) の 3 種類である.それぞれの持つエネルギー,Linear Energy Transfar (LET),シリコンでの透過距離を表 2 に示す.

(a) L0: SL を構成するインバータおよび出力のイン バータの diffusion を共有

(b) L1 : SL を構成するインバータの diffusion を 共有

(c) L2: SL を構成するインパータの diffusion を 分離

図 4 設計した 3 種類の FF のレイアウト

### 3.3 測定手順

重イオン照射ソフトエラー測定は以下の手順で行う.

- 1. シフトレジスタを構成する FF 全てに同じ値を書き込み 初期化する.

- 2. クロック信号を停止し,重イオンを照射する.

- 3. 照射後シフトレジスタの値を読み出し,値が反転したFFの個数を数える.

この手順を 1 つの条件に対し ,5 回行う  $(Ne \ order=0.75)$  では セス依存性は全動作状態の平均値 ( 各条件 1 回測定) で比較する . レイアウト構造依存性は , レイアウト構造の異なる SL ( スレイブラッチ) で値を保持する (DATA, CLK)=(1,0),(0,0)の 2 つの動作状態の測定結果で比較する .

### 3.4 衝突断面積

評価には衝突断面積 (CS) を用いる.式 1 に衝突断面積の算出式を示す.計算には,観測ソフトエラー数  $(N_{

m error})$ ,単位面積当たりのイオン総数  $(N_{

m ion})$ , ${

m FF}$  の合計ビット数  $(N_{

m FF})$  使用する.

$$CS \left[ \text{cm}^2 / \text{bit} \right] = \frac{N_{\text{error}}}{N_{\text{ion}} \times N_{\text{FF}}}$$

(1)

# 4. 測定結果

重イオン照射ソフトエラー測定の結果を以下に示す.

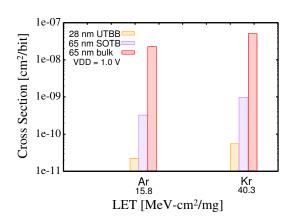

#### 4.1 プロセス依存性

$65~\mathrm{nm}~\mathrm{bulk}$ , SOTB ,  $28~\mathrm{nm}~\mathrm{UTBB}$  の衝突断面積と LET の 関係を図 7 , 表  $3~\mathrm{lc}$ 示す .  $65~\mathrm{nm}~\mathrm{bulk}$  とは従来構造の CMOS プロセスであり ,  $2~\mathrm{tag}$ の FDSOI のソフトエラー耐性の評価 のため結果を示す . グラフの縦軸は対数を用い , 電源電圧は  $1.0~\mathrm{V}$  , 全動作状態の平均値である .

表 2 使用した重イオンの各パラメータ

|              | Energy [MeV] | LET $[MeV-cm^2/mg]$ | Range [um] |

|--------------|--------------|---------------------|------------|

| Ne (Neon)    | 75           | 6.5                 | 38.9       |

| Ar (Argon)   | 150          | 15.8                | 36.1       |

| Kr (Krypton) | 322          | 40.3                | 37.3       |

図 7 各プロセスにおける電源電圧  $1.0\mathrm{V}$  時の衝突断面積と LET の 関係

#### 4.2 レイアウト構造依存性

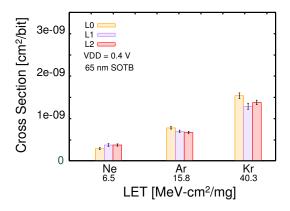

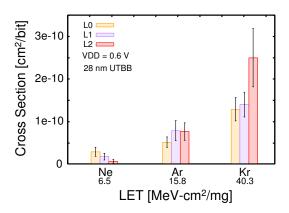

各プロセスにおける衝突断面積のレイアウト構造依存性を図8,9,表4,5にそれぞれ示す.縦軸は線形を用いており,電源電圧はそれぞれ0.6 V, 0.4 V で測定をおこなった.

# 5. 考 察

測定結果から 2 種の FDSOI で試作した FF のソフトエラー耐性について,プロセス依存性,レイアウト構造依存性についての考察を行う.

# 5.1 プロセス依存性について

Kr 照射時で比較すると SOTB は bulk よりも約 52 倍高い エラー耐性を持ち, UTBB は SOTB よりもデバイス単体は約 18 倍高いソフトエラー耐性を持つ. 微細化が進むとチップ当た

表 3 各プロセスにおける電源電圧 1.0 V 時の衝突断面積

|     | Cross Section [cm <sup>2</sup> /bit] |                        |                        |

|-----|--------------------------------------|------------------------|------------------------|

| ion | 65 nm bulk                           | 65 nm SOTB             | 28 nm UTBB             |

| Ne  | _(注1)                                | _(注1)                  | 0                      |

| Ar  | $2.32 \times 10^{-08}$               | $3.38 \times 10^{-10}$ | $2.18 \times 10^{-11}$ |

| Kr  | $5.02 \times 10^{-08}$               | $9.65 \times 10^{-10}$ | $5.29 \times 10^{-11}$ |

(注1):測定を行なっていない条件

図 8 65 nm SOTB における電源電圧 0.4 V 時の 衝突断面積のレイアウト構造依存性

りのソフトエラー耐性は高くなると考えられているが,今回の結果からは同一面積でのエラー率を比較しても 28 nm UTBB のソフトエラー耐性の方が約 5 倍高い.この理由は FDSOI はエラーの原因となる電子正孔対の発生するボディの体積が小さく,微細化が進むと幅が小さくなるのに加えてより薄くなることでエラーが発生しにくくなるためであると考えられる.

### 5.2 レイアウト構造依存性について

$65~\mathrm{nm}$  SOTB においては,レイアウト構造が異なることで発生したソフトエラーの耐性差は最大でも約  $1.2~\mathrm{flat}$  倍程度であった.このことから,レイアウト構造を変化させてもソフトエラー耐性への影響は無いと考えられる. $28~\mathrm{nm}$  UTBB においては, $1.0~\mathrm{L}$  に大いでは、以下の $1.0~\mathrm{l}$  と比較して  $1.0~\mathrm{l}$  に対けて、以下の $1.0~\mathrm{l}$  の衝突断面積が約  $1.0~\mathrm{l}$  にかた.この結果について,以下の $1.0~\mathrm{l}$  つの原因が考えられる.パルス軽減効果  $1.0~\mathrm{l}$  のレイアウトでは,チャージシェアリングによってソフトエラーの要因であるパルスを軽減する効果が働いていると考えられる.表  $1.0~\mathrm{l}$  に各プロセスにおけるスレイブラッチを構成するインバータとトライステートインバータ間の距離  $1.0~\mathrm{l}$  を原射すると軽減率が高くなるため, $1.0~\mathrm{l}$  における  $1.0~\mathrm{l}$  に別すると軽減率が高くなるため, $1.0~\mathrm{l}$  における  $1.0~\mathrm{l}$  に別すると軽減率が高くなるため, $1.0~\mathrm{l}$  における  $1.0~\mathrm{l}$  に別すると軽減率が高くなるため, $1.0~\mathrm{l}$  における  $1.0~\mathrm{l}$  に

表 4 65 nm SOTB における電源電圧 0.4 V 時のレイアウト毎の衝突 断面積

|     | Cross Section [cm <sup>2</sup> /bit] |                        |                        |

|-----|--------------------------------------|------------------------|------------------------|

| ion | L0                                   | L1                     | L2                     |

| Ne  | $2.95 \times 10^{-10}$               | $3.82 \times 10^{-10}$ | $3.82 \times 10^{-10}$ |

| Ar  | $7.85 \times 10^{-10}$               | $7.03 \times 10^{-10}$ | $6.75 \times 10^{-10}$ |

| Kr  | $1.54 \times 10^{-09}$               | $1.29 \times 10^{-09}$ | $1.38 \times 10^{-09}$ |

表 5 28 nm UTBB における電源電圧 0.6 V 時のレイアウト毎の衝 突断面積

|     | Cross Section [cm <sup>2</sup> /bit] |                        |                        |

|-----|--------------------------------------|------------------------|------------------------|

| ion | L0                                   | L1                     | L2                     |

| Ne  | $2.95 \times 10^{-11}$               | $1.81 \times 10^{-11}$ | $7.08 \times 10^{-12}$ |

| Ar  | $5.19 \times 10^{-11}$               | $7.89 \times 10^{-11}$ | $7.68 \times 10^{-11}$ |

| Kr  | $1.29 \times 10^{-10}$               | $1.40 \times 10^{-10}$ | $2.50 \times 10^{-10}$ |

図 9 28 nm UTBB における電源電圧 0.6 V 時の 衝突断面積のレイアウト構造依存性

の  ${\rm Kr}$  照射時にチャージシェアリングが発生する. $28~{\rm nm}$  における  ${\rm L2}$ , $65~{\rm nm}$  における全てのレイアウトでは, $D_{\rm g}$  がチャージシェアリングが発生する範囲よりも広いためにパルス軽減効果が発生していない. ${\rm L2}$  ではインバータとトライステートインバータの拡散領域を分割し, ${\rm STI}$  を埋め込んだ構造になっているため,チャージシェアリングの発生を妨げていると考えられる

圧縮ストレスの影響 L2 のレイアウトでは,インバータとトライステートインバータ間に STI が埋め込まれており,左右のトランジスタに圧縮ストレスがかかる.通常の STI による圧縮ストレスはトランジスタのパフォーマンス向上に用いられる. 65 nm プロセスでは圧縮ストレスの影響を軽減するためにチップ作成の面方位は <100> を用いている [13]. 28 nm の面方位も <100> を用いていると予想される.しかし,より微細なプロセスである 28 nm では軽減しきれなかった圧縮ストレスの影響が及んでいると考えられる.STI によって,チャネル長方向に圧縮ストレスを受けた PMOS のパフォーマンスが向上することにより,電荷収集量が増加し一過性のパルス幅が拡大し,ソフトエラー耐性が低下したと考えられる.圧縮ストレスによるソフトエラー耐性への影響は,デバイスシミュレーションを用いて検証を行う予定である.

### 6. 結 論

65 nm SOTB と 28 nm UTBB における FF のソフトエラー耐性の比較を行った.重イオン照射ソフトエラー測定を実施し,プロセス依存性,レイアウト依存性について評価を行った.実測結果より,一般的には微細化に伴い同一面積当たりのソフトエラー耐性が上昇すると考えられているが,65 nm SOTB を28 nm UTBB に変更することで同ビット数で比較すると約 18 倍,同面積では約 5 倍ソフトエラー耐性が向上することが分

表 6 インバータとトライステートインバータ間距離  $(D_g)$ .

|            | $D_{\rm g} \ [{\rm nm}]$ |     |     |

|------------|--------------------------|-----|-----|

| Process    | L0                       | L1  | L2  |

| 28 nm UTBB | 133                      | 133 | 274 |

| 65 nm SOTB | 390                      | 300 | 780 |

図 10 チャージシェアリングによるパルス減衰効果の概念図

かった.これは,ソフトエラーの原因である電子正孔対が発生 するボディ部が微細化に伴い幅,薄さ共に減少したことでソフ トエラー耐性が向上したと考えられる . 65 nm SOTB ではレ イアウト構造依存性は観測出来なかった.一方,28 nm UTBB では,拡散領域を分割した L2 の Kr 照射時の衝突断面積が約 2 倍という結果となった.この原因として,スレイブラッチを 構成するインバータとトライステートインバータ間の距離が チャージシェアリングが発生する範囲より長かったこと,埋め こまれた STI によってチャージシェアリングの発生を妨げた ことが原因であると考えられる.軽減しきれなかったSTIによ る圧縮ストレスによって PMOS のエラー耐性が低下したこと も影響していると考えられる.高い LET を持つイオンの存在 する宇宙空間での利用を見据えた機器を製作する際には,イン バータとトライステートインバータの拡散領域を共有したレイ アウトを使用することで面積オーバヘッド無しでソフトエラー 耐性を向上させることが出来る.

# 7. 謝辞

本研究は , JSPS 科研費 15H02677 助成を受けたものである . また , チップ試作は , 東京大学大規模集積システム設計教育研究センターを通し , シノプシス , 日本ケイデンス , メンターグラフィックス各社ならびに , CMP , ルネサスエレクトロニクス , ST マイクロエレクトロニクスの協力で行われたものである .

### 文 献

- N. Seifert et al. In *Proc. Int. Rel. Phys. Symp.*, pages 188– 197, May 2010.

- [2] S. Buchner et al. IEEE Transactions on Nuclear Science, 44(6):2209–2216, Dec 1997.

- [3] H. Liu et al. In IEDM, pages 25.5.1–25.5.4, Dec 2012.

- [4] K. Zhang, S. Kanda, J. Yamaguchi, J. Furuta, and K. Kobayashi. Analysis of the soft error rates on 65-nm sotb and 28-nm utbb fd-soi structures by a phits-tcad based simulation tool. In 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pages 1–4, Sept 2015.

- [5] L. Sheng, H. Wei, Z. Zhun, H. Lingxian, C. Jianmin, and W. Qingyang. Investigation of double peak voltage in pulse quenching effect on the single-event transient. In 2016 IEEE International Nanoelectronics Conference (INEC), pages 1– 2, May 2016.

- [6] R. Radojcic. In 2016 IEEE International Interconnect Technology Conference / Advanced Metallization Conference (IITC/AMC), pages 98–98, May 2016.

- [7] C. C. Tan et al. In 2016 IEEE International Conference on Semiconductor Electronics (ICSE), pages 228–231, Aug 2016.

- [8] E. Petersen. Single event effects in aerospace. John Wiley & Sons, 2011.

- [9] N. H. Weste and D. M. Harris. Cmos vlsi design: A circuits and systems perspective 4th. 2010.

- [10] N. Sugii, R. Tsuchiya, T. Ishigaki, Y. Morita, H. Yoshimoto, and S. Kimura. Local v<sub>th</sub> variability and scalability in Silicon-on-Thin-BOX (SOTB) CMOS with small random-dopant fluctuation. *IEEE Trans. Elec. Dev.*, 57(4):835-845, Apr. 2010.

- [11] C. H. Ge, C. C. Lin, C. H. Ko, C. C. Huang, Y. C. Huang, B. W. Chan, B. C. Perng, C. C. Sheu, P. Y. Tsai, L. G. Yao, C. L. Wu, T. L. Lee, C. J. Chen, C. T. Wang, S. C. Lin, Y. C. Yeo, and C. Hu. Process-strained si (pss) cmos technology featuring 3d strain engineering. In *Electron Devices Meeting*, 2003. IEDM '03 Technical Digest. IEEE International, pages 3.7.1–3.7.4, Dec 2003.

- [12] T. Philip Beow Yew. Compact Modeling Of Deep Submicron CMOS Transistor With Shallow Trench Isolation Mechanical Stress Effect [TK7871. 99. M44 T161 2008 f rb]. PhD thesis, University Sains Malaysia, 2008.

- [13] T. Iwamatsu, T. Terada, K. Ishikawa, H. Oda, and Y. Inoue. Electrical characteristics and crystal quality analysis of thin-body channel silicon-on-insulator metal oxide semiconductor field-effect transistors using two-step elevated silicon epitaxial process. *Japanese Journal of Applied Physics*, 48(4S):04C045, 2009.