# Extracting Voltage Dependence of BTI-induced Degradation without Temporal Factors by Using BTI-Sensitive and BTI-Insensitive Ring Oscillators

Ryo Kishida\*, *Member, IEEE*, Takuya Asuke<sup>†</sup>, Jun Furuta<sup>†</sup>, *Member, IEEE*, and Kazutoshi Kobayashi<sup>†</sup> *Member, IEEE*,

Abstract—Measuring bias temperature instability (BTI) by ring oscillators (ROs) is frequently used. However, the performance of a semiconductor chip is fluctuated dynamically due to bias, temperature and etc. BTI-sensitive and -insensitive ROs are implemented in order to extract BTI-induced degradation without temporal fluctuation factors. A test chip including those 840 ROs was fabricated in a 65 nm process. BTI-induced degradation without temporal fluctuation was successfully measured by subtracting results of BTI-insensitive ROs from those of BTI-sensitive ones. Extraction of BTI-induced degradation is useful in any supply voltage. Performance degradation of NMOS and PMOS transistors mainly due to BTI increases along power law function and fitting parameters decreases as the supply voltage decreases.

Index Terms—Bias Temperature Instability (BTI), voltage dependence, Negative BTI (NBTI), Positive BTI (PBTI), Ring Oscillator (RO)

## I. INTRODUCTION

DEVICE sizes of semiconductor chips have been shrinked with the Moore's law [1]. It has brought a lot of advantages, for example, high-performance and low-power electronic gadgets such as smartphones, smart watches and so on. However, reliability problems have appeared in nanometer-scale devices. Particularly, bias temperature instability (BTI) has become a significant concern with the miniaturization of the device size [2]. BTI is one of aging degradation. Transistor performance is degrading with time due to BTI, which results in decreasing timing margins of implemented circuits. BTI-induced degradation accelerates as voltage and temperature increase. BTI is a serious reliability issue that shortens the lifetime of circuits.

BTI measurement circuits to extract BTI-induced degradations without temporal fluctuations are required because measurement results include fluctuation factors from ambient environments. Our motivation is to extract degradation rates from only BTI-induced degradation by comparing the BTI-sensitive with the BTI-insensitive ring oscillators (ROs). It is impossible to remove BTI-induced degradation in random logic circuits including processors or hardware accelerators

Manuscript received \*\*\*\*, 20xx; revised \*\*\*\*, 20xx.

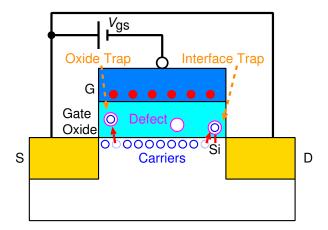

Fig. 1. Atomistic trap-based BTI (ATB) model. BTI occurs when defects trap carriers.

since input pins are not fixed. It is important to estimate BTI-induced degradation accurately by the proposed method.

BTI-sensitive and -insensitive ROs are used to extract BTI-induced degradation without temporal factors. The fluctuation factors are removed by subtracting results of those two type ROs. Our research focused on the extracting BTI-induced degradation at only 2.0 V supply voltage in ICMTS 2019 [3].

In this paper, BTI-induced degradation are measured from nominal 1.0 V to 2.0 V using BTI-sensitive and -insensitive ROs. The measurement results are fitted and degradation factors are extracted from the fitting curves. This paper shows BTI-sensitive and -insensitive ROs are useful to extract the degradation in any supply voltage.

We explain BTI in section II. Section III introduces related work of BTI. Section IV shows the structures of those ROs. In section V, measurement results are presented. Finally, section VI shows our conclusion.

# II. BIAS TEMPERATURE INSTABILITY (BTI)

Bias temperature instability (BTI) is one of the aging degradations and transistor performance is degrading with time as voltage and temperature increase [4]–[6]. BTI-induced degradation occurs when defects trap carriers. This degradation can be explained by the atomistic trap-based BTI (ATB) model as shown in Fig. 1 [7], [8]. There are oxygen vacancy defects in the gate oxide and dangling bonds in the interface between

<sup>\*</sup>Department of Electrical Engineering, Faculty of Science and Technology, Tokyo University of Science, 2641 Yamazaki, Noda, Chiba, Japan E-mail: kishida@rs.tus.ac.jp

<sup>†</sup>Department of Electronics, Graduate School of Science and Technology, Kyoto Institute of Technology, Japan

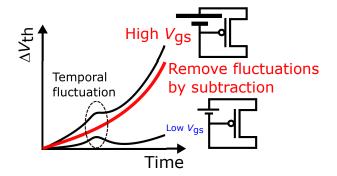

Fig. 2. BTI-induced degradation in Higher and lower gate-source voltage ( $V_{\rm gs}$ ). Temporal fluctuations are removed by subtracting results of Higher and lower  $V_{\rm gs}$ .

the gate oxide and silicon substrate. When these defects trap carriers, the electric field in the gate oxide decreases and drain-source current decreases. Each defect has an individual time constant to trap a carrier. Those time constants are distributed from  $10^{-9}$  s to  $10^9$  s [8]. Particularly, defects with large time constants affect aging degradations induced by BTI. BTI-induced degradation is recovered when carrier emission is promoted as  $V_{\rm gs}$  is reduced because trapped carriers in the gate oxide are easily emitted to channel.

There are negative BTI (NBTI) and positive BTI (PBTI). NBTI occurs on PMOS when  $V_{\rm gs}$  is negative. Likewise, PBTI is observed on NMOS especially in technologies with high-k (HK) gate dielectrics [9]. NBTI-induced degradation is higher than PBTI-induced degradation in larger than 90 nm process. One of the reasons is assumed that  $V_{\rm th}$  sensitivity is different in NMOS and PMOS due to band gap even if same charge is trapped to the gate oxide [10]. However, high-k (HK) gate dielectrics has much defects and PBTI cannot negligible in recent nano-scaled devices.

BTI-induced degradation is accelerated as  $V_{\rm gs}$  increases as shown in Fig. 2. Threshold voltage shift ( $\Delta V_{\rm th}$ ) degrades along with Eq. (1) [11],

$$\Delta V_{\rm th} = A * t^n * V_{\rm gs}^m , \qquad (1)$$

where A is the pre-factor, t is the stress time, n is the power law time exponent, and m is the power law voltage acceleration. BTI-induced degradation with higher  $V_{\rm gs}$  is larger than that with lower  $V_{\rm gs}$ . However, temporal fluctuations caused by temperature and voltage affect both ROs. Temperature and voltage are fluctuated by feedback system of measurement instruments. Oscillation frequency of both ROs increases or decreases by the same amount. BTI-induced degradation without temporal factors are extracted by taking difference between BTI-sensitive and -insensitive ROs.

## III. RELATED WORK

There are several countermeasures of BTI. BTI-induced degradation is predicted during chip design. Circuit topology is changed to suppress BTI-induced degradation. Critical path changes and delay time decreases by arranging circuit topologies [12].

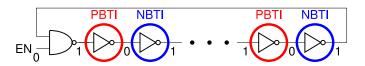

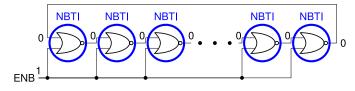

Fig. 3. An inverter-based ring oscillator (RO). PBTI and NBTI occurs in every other inverters when the RO stops. NAND gate is to control oscillation.

After chip design, degradation is monitored and suppressed by body bias in real-time [13], [14]. BTI is suppressed with decreasing supply voltage and applying the forward body bias because forward body bias compensates performance degradation by  $V_{\rm gs}$  decrease. However, body bias generators and threshold voltage  $(V_{\rm th})$  monitors are required.

Drain current is measured to evaluate BTI-induced degradation of a single transistor [15]. This single transistor measurement is useful to evaluate BTI of individual devices. However, it takes a lot of time to measure huge number of transistors. By using ROs, performance degradation caused by BTI can be evaluated to count the number of oscillations in a short period [16]. However, measurement results include temporal fluctuations such as temperature and voltage fluctuations. Our measurement circuits remove those fluctuations and evaluate accurate BTI-induced degradation by subtracting BTI-sensitive ROs from -insensitive ROs.

## IV. MEASUREMENT CIRCUITS

An inverter-based RO is shown in Fig. 3. The leftmost NAND-gate controls oscillation by one of input pins (EN) in the NAND-gate. The RO oscillates when EN is high because truth table of the NAND-gate is the same as inverter. When EN is low, the nodes between the inverters are alternately fixed to 0 or 1 and the RO stops oscillation. The RO suffers from BTI when it stops oscillation since  $V_{\rm gs}$  is applied to transistors in all gates. The oscillation frequency is degraded when the  $V_{\rm th}$  of those transistors is degraded.

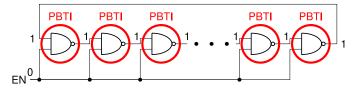

PBTI becomes dominant since all inverters are replaced to NAND-gates as shown in Fig. 4. When EN is high, all outputs of NAND-gates are 1. On the other hand, NBTI becomes dominant in the RO composed of NOR-gates as shown in Fig. 5. Oscillation is controlled by ENB. When ENB is high, all outputs of NOR-gates are 0 to accelerate only NBTI.

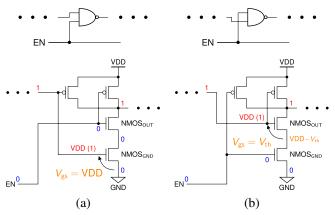

Sensitivities to BTI can be changed by changing input connections. Figure 6 shows two-types of NAND ROs in the transistor level. NMOS is connected in series from the output terminal to ground (GND). NMOS connected to the output pin is NMOS $_{\rm OUT}$  and that connected to GND is NMOS $_{\rm GND}$ . In Fig 6 (a), the gate terminals of NMOS $_{\rm OUT}$  and NMOS $_{\rm GND}$  are connected to EN and the output pins of previous stages, respectively. When EN is low, all output pins of NAND-gates become 0. PBTI is accelerated in NMOS $_{\rm GND}$  in all stages because the  $V_{\rm gs}$  become supply voltage (VDD). Here this RO is called the PBTI-sensitive RO.

PBTI is suppressed by changing input connections on the PBTI-insensitive RO as shown in Fig 6 (b). Gate terminals of those NMOS are exchanged between EN and the output pins of previous stages. When EN is low,  $V_{\rm gs}$  of NMOS $_{\rm OUT}$  is

Fig. 4. RO composed NAND gates. PBTI becomes dominant when RO stops.

Fig. 5. RO composed NOR gates. NBTI becomes dominant when RO stops.

Fig. 6. NAND RO in transistor level. (a) PBTI-sensitive RO. (b) PBTI-insensitive RO

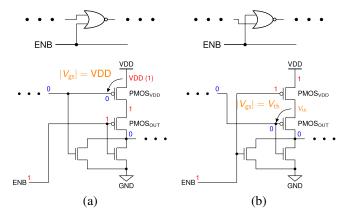

Fig. 7. NOR RO in transistor level. (a) NBTI-sensitive RO. (b) NBTI-insensitive RO.

decreased to threshold voltage  $(V_{\rm th})$  instead of VDD. Although PMOS connected to EN suffers from NBTI, the oscillation frequency does not change because it is determined by delay time in MOSFETs connected to the output pins of the previous stages. This PBTI-insensitive RO suppresses PBTI because of lower  $V_{\rm gs}$  than that in PBTI-sensitive RO.

Likewise, NBTI is suppressed by arranging the input connections in NOR ROs as shown in Fig. 7. Gate terminals of  $PMOS_{\rm OUT}$  and  $PMOS_{\rm VDD}$  are connected to ENB and to

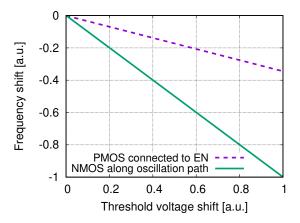

Fig. 8. Simulation results of  $V_{\rm th}$  sensitivity. NMOS along the oscillation path have a three times or more sensitivity to  $V_{\rm th}$  fluctuation than PMOS connected to EN terminal.

the output pins of previous stages, respectively as shown in Fig. 7 (a). When ENB is high, PMOS<sub>VDD</sub> suffers from NBTI. NBTI is suppressed by changing input connections as shown in Fig. 7 (b).  $|V_{\rm gs}|$  of PMOS<sub>OUT</sub> is decreased to  $V_{\rm th}$ . These ROs are named as the NBTI-sensitive RO and the NBTI-insensitive RO, respectively.

Simulation results obtained by changing the  $V_{\rm th}$  of transistors in NAND RO is shown in Fig. 8. The X- and Y-axis show  $V_{\rm th}$  shift and the frequency degradation, respectively. Oscillation frequencies proportionally change with  $V_{\rm th}$  shift. The oscillation frequency changes when the  $V_{\rm th}$  of the PMOS connected to EN shifts as shown by the dotted line in Fig. 8. However, it is one-third or less sensitive than those of NMOS along the oscillation path. In addition,  $V_{\rm gs}$  of NMOS connected to EN and PMOS along the oscillation path are 0 during the stress (no oscillation) phase. Thus, PBTI-induced degradation can be measured in NAND RO of Fig. 6. NOR RO of Fig. 7 also has the same tendency in  $V_{\rm th}$  sensitivity.

They were fabricated in a 65 nm fully depleted silicon-on-insulator (FDSOI) process and BTI-induced degradations of them were measured. The nominal power supply voltage is 1.0 V in the 65 nm process. We measure the degradation to investigate acceleration of BTI from the nominal voltage.

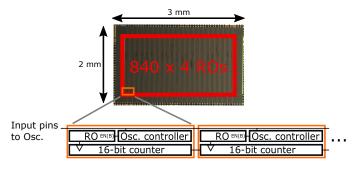

Table I shows fabricated RO structures and Fig. 9 shows a chip micrograph of the test chip. The chip size is  $3 \times 2 \text{ mm}^2$  in which  $840 \times 4$  11-stage ROs are embedded. The number of ROs is limited by the chip area. The chip is designed to implement as many ROs as possible. Oscillation of ROs is controlled by the oscillation (Osc.) controller and input pins. The number of oscillations is counted by the 16-bit counter. Those controller and counter are mainly composed by standard flip-flops. Each RO has its own controller and counter. They formed a unit that is connected in series. The number of oscillation in counters are measured and oscillation frequencies are calculated by dividing oscillation time.

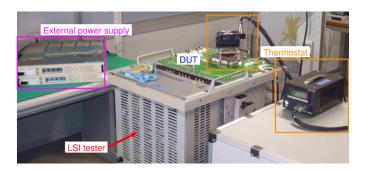

Our measurement system is shown in Fig. 10. The test chip (Device Under Test, DUT) is measured by LSI tester. An external power supply and a Peltier module are used to apply higher bias and temperature stress. It is difficult to

Fig. 9. Test chip micrograph. The number of oscillations is counted by embedded 16-bit counter.

Fig. 10. Measurement system. Test chip (Device Under Test, DUT) is measured by LSI tester. Voltage is supplied by external power supply and temperature is fixed by Peltier module with temperature controller.

cover whole measurement system within higher temperature. In this system, the voltage and temperature are fluctuated by the feedback system of the measurement instruments. The subtraction method using BTI-sensitive ROs and -insensitive ROs is useful.

#### V. MEASUREMENT RESULTS

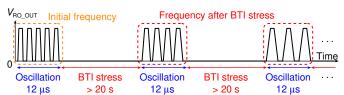

Figure 11 shows a measurement flow to measure BTI-induced degradations. ROs oscillate for 12  $\mu s$  in the order of gigahertz. Those stop oscillation for over 20 s for BTI stress after measuring frequencies. ROs suffer from BTI stress when it stop oscillation. Frequencies are measured every time after BTI stress. The oscillation and BTI stress are repeated. The measurements are performed at a temperature of 120 °C and a supply voltage of 2.0 V to accelerate BTI-induced degradation. Degradation rate ( $D_{\rm rate}$ ) is calculated as

$$D_{\text{rate}} = \frac{f_0 - f(t)}{f_0} ,$$

(2)

where  $f_0$  is the initial frequency at t=0 and f(t) is the measured frequency at time t.

TABLE I FABRICATED RO STRUCTURES.

| Structure        | Figure     | Number of ROs |

|------------------|------------|---------------|

| PBTI-sensitive   | Fig. 6 (a) |               |

| PBTI-insensitive | Fig. 6 (b) | 840           |

| NBTI-sensitive   | Fig. 7 (a) | in all ROs    |

| NBTI-insensitive | Fig. 7 (b) |               |

Fig. 11. Measurement flow of BTI-induced degradations.

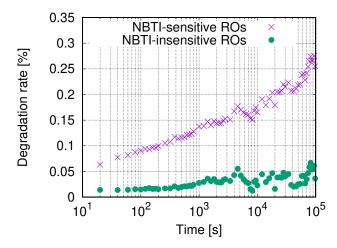

Fig. 12. Measurement results of PBTI-induced degradation.

Fig. 13. Measurement results of NBTI-induced degradation.

#### A. Subtraction Results

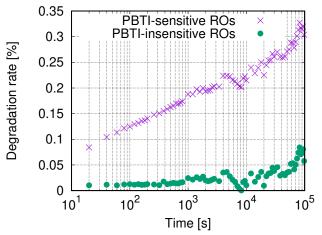

Figure 12 shows the measured BTI-induced degradations in NAND ROs for PBTI-induced degradation. The X-axis and the Y-axis show the BTI stress time and  $D_{\rm rate}$ , respectively.  $D_{\rm rate}$  is averaged in 840 ROs. The  $D_{\rm rate}$  values of PBTI-sensitive ROs [in Fig. 6 (a)] increase with time. However, The  $D_{\rm rate}$  of PBTI-insensitive ROs [in Fig. 6 (b)] is almost constant. The degradation of BTI-sensitive ROs is 5x larger than that of BTI-insensitive ROs at  $10^5$  s. Figure 13 shows the measurement results in NOR ROs for NBTI stress. NBTI is also suppressed by arranging input connections like NAND ROs.

These results are dynamically fluctuated mainly due to temperature or voltage fluctuations. For example,  $D_{\rm rate}$  suddenly increased at 5 ks and decreased at 10 ks. Both results

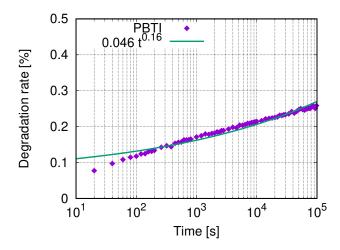

Fig. 14. Difference between PBTI-sensitive and -insensitive ROs.

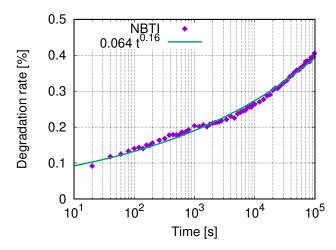

Fig. 15. Difference between NBTI-sensitive and -insensitive ROs.

from BTI-sensitive and -insensitive ROs are correlated. Those fluctuation can be removed by subtracting BTI-insensitive results from BTI-sensitive ones. Figures 14 and 15 show the difference in NAND and NOR ROs, respectively. Fluctuations are removed and  $D_{\rm rate}$  clearly increases with time. Subtracted data are fitted by Eq. (3) following Eq. (1).

$$\Delta V_{\rm th} = A * t^n * V_{\rm param} , \qquad (3)$$

where t is the stress time, A and  $V_{\rm param}$  are fitting parameters, and n is time exponent, which is 0.16 as in [17] because the same transistor size and process are used in NAND and NOR ROs.  $V_{\rm param}$  represents acceleration factor of  $V_{\rm gs}$ . Slope of the fitting fuction becomes more slightly as  $V_{\rm param}$  is lower, which means the lower BTI-induced degradation. Measurement results are along with the fitting curve in both PBTI- and NBTI-induced degradations.

# B. Voltage Dependence

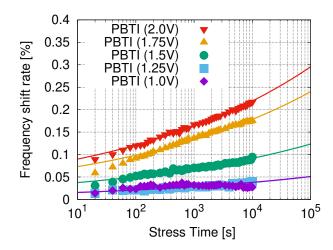

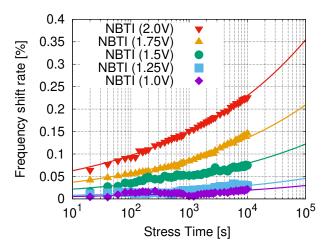

Figure 16 shows the voltage dependence of BTI-induced degradations in NAND ROs for PBTI-induced degradation. PBTI-induced degradations without ambient fluctuations are extracted by subtraction in any voltage. Figure 17 shows the

Fig. 16. Measurement results of voltage dependence in PBTI-induced degradation.

Fig. 17. Measurement results of voltage dependence in NBTI-induced degradation.

TABLE II FITTED PARAMETERS OF  $V_{\mathrm{param}}$  .

| Voltage [V] | NBTI  | PBTI |

|-------------|-------|------|

| 2.0         | 1     | 1    |

| 1.75        | 0.59  | 0.81 |

| 1.5         | 0.34  | 0.42 |

| 1.25        | 0.13  | 0.17 |

| 1.0         | 0.084 | 0.17 |

voltage dependence in NOR ROs for NBTI stress. NBTI-induced degradations are also extracted like PBTI.

$V_{\mathrm{param}}$  in Eq. (3) is the voltage dependence parameter. Table II shows fitted parameters  $V_{\mathrm{param}}$ . A and n are fixed to those parameters at 2.0 V. Parameters  $V_{\mathrm{param}}$  decreases as supply voltage decreases as shown in Table II. BTI-induced degradations without ambient fluctuations are extracted in any voltage.

#### VI. CONCLUSIONS

BTI-sensitive and BTI-insensitive ROs are used to extract BTI-induced degradations without fluctuations of ambient

environments. The test chip was fabricated in the 65 nm process and BTI-induced degradations were measured. The degradation of PBTI/NBTI-sensitive ROs is five times larger than PBTI/NBTI-insensitive ROs at 10 ks. Fluctuation originated from ambient environments are successfully removed by subtracting results of BTI-insensitive ROs from those of BTI-sensitive ones. This subtraction is useful in any voltage.

#### ACKNOWLEDGMENTS

This work is supported by JSPS KAKENHI Grant Number 15H02677. The chip for this work was fabricated by Renesas Electronics and designed by utilizing the EDA system supported by the VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys Inc., Cadence Design System, and Mentor Graphics Inc.

#### REFERENCES

- [1] M. Bohr, "The Evolution of Scaling from the Homogeneous Era to the Heterogeneous Era," *IEEE International Electron Devices Meeting (IEDM)*, pp. 1.1.1–1.1.6, Dec. 2011.

- [2] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, F. Schanovsky, J. Franco, M. T. Luque, and M. Nelhiebel, "The Paradigm Shift in Understanding the Bias Temperature Instability: From Reaction-Diffusion to Switching Oxide Traps," *IEEE Transactions on Electron Devices*, vol. 58, pp. 3652–3666, Nov. 2011.

- [3] R. Kishida, T. Asuke, J. Furuta, and K. Kobayashi, "Extracting BTI-induced Degradation without Temporal Factors by Using BTI-Sensitive and BTI-Insensitive Ring Oscillators," *IEEE International Conference on Microelectronic Test Structures (ICMTS)*, pp. 24–27, March 2019.

- [4] R. Kishida, A. Oshima, and K. Kobayashi, "Negative Bias Temperature Instability Caused by Plasma Induced Damage in 65 nm Bulk and Silicon on Thin BOX (SOTB) Processes," *IEEE International Reliability Physics Symposium (IRPS)*, pp. CA.2.1–CA.2.5, April 2015.

- [5] V. Huard, C. Parthasarathy, C. Guerin, T. Valentin, E. Pion, M. Mammasse, N. Planes, and L. Camus, "NBTI Degradation: From Transistor to SRAM Arrays," *IEEE International Reliability Physics Symposium (IRPS)*, pp. 289–300, April 2008.

- [6] D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing," *Journal of Applied Physics*, vol. 94, pp. 1–18, July 2003.

- [7] H. Kukner, S. Khan, P. Weckx, P. Raghavan, S. Hamdioui, B. Kaczer, F. Catthoor, L. V. der Perre, R. Lauwereins, and G. Groeseneken, "Comparison of Reaction-Diffusion and Atomistic Trap-Based BTI Models for Logic Gates," *IEEE Transactions on Device and Materials Reliability*, vol. 14, pp. 182–193, March 2014.

- [8] B. Kaczer, S. Mahato, V. V. de Almeida Camargo, M. Toledano-Luque, P. J. Roussel, T. Grasser, F. Catthoor, P. Dobrovolny, P. Zuber, G. Wirth, and G. Groeseneken, "Atomistic Approach to Variability of Bias-Temperature Instability in Circuit Simulations," *IEEE International Reliability Physics Symposium (IRPS)*, pp. XT.3.1–XT.3.5, April 2011.

- [9] S. Zafar, Y. Kim, V. Narayanan, C. Cabral, V. Paruchuri, B. Doris, J. Stathis, A. Callegari, and M. Chudzik, "A Comparative Study of NBTI and PBTI (Charge Trapping) in SiO2/HfO2 Stacks with FUSI, TiN, Re Gates," Symposium on VLSI Technology, pp. 23–25, June 2006.

- [10] D. Schroder, "Negative bias temperature instability: What do we understand?," *Microelectronics Reliability*, vol. 47, pp. 841–852, June 2007.

- [11] B. P. Linder and T. Ando, "Combined Ramp Voltage Stress and Constant Voltage Stress for optimal BTI voltage acceleration and lifetime modeling," *IEEE International Reliability Physics Symposium (IRPS)*, pp. XT.7.1–XT.7.4, June 2014.

- [12] H. Amrouch, B. Khaleghi, A. Gerstlauerz, and J. Henkel, "Reliability-aware Design to Suppress Aging," *Design Automation Conference (DAC)*, pp. 12:1–12:6, June 2016.

- [13] R. Faraji and H. R. Naji, "Adaptive Technique for Overcoming Performance Degradation Due to Aging on 6T SRAM Cells," *IEEE Transactions on Device and Materials Reliability*, vol. 14, pp. 1031–1040, Dec. 2014.

- [14] J. Franco, B. Kaczer, G. Eneman, P. J. Roussel, T. Grasser, J. Mitard, L. A. Ragnarsson, M. Cho, L. Witters, T. Chiarella, M. Togo, W. E. Wang, A. Hikavyy, R. Loo, N. Horiguchi, and G. Groeseneken, "Superior NBTI Reliability of SiGe Channel pMOSFETs: Replacement Gate, FinFETs, and Impact of Body Bias," *IEEE International Electron Devices Meeting (IEDM)*, pp. 18.5.1–18.5.4, Dec. 2011.

- [15] J. Franco, B. Kaczer, M. Toledano-Luque, P. J. Roussel, G. Groeseneken, B. Schwarz, M. Bina, M. Waltl, P. J. Wagner, and T. Grasser, "Reduction of the BTI Time-Dependent Variability in Nanoscaled MOSFETs by Body Bias," *IEEE International Reliability Physics Symposium (IRPS)*, pp. 2D.3.1–2D.3.6, April 2013.

- [16] W. H. Choi, S. Satapathy, J. Keane, and C. H. Kim, "A Test Circuit Based on a Ring Oscillator Array for Statistical Characterization of Plasma-Induced Damage," *IEEE Custom Integrated Circuits Conference (CICC)*, Sept. 2014. p.14-3.

- [17] S. Mukhopadhyay and S. Mahapatra, "An Experimental Perspective of Trap Generation Under BTI Stress," *IEEE Transactions on Electron Devices*, vol. 62, pp. 2092–2097, July 2015.