# Radiation-Hardened Flip-Flops with Small Area and Delay Overheads Using Guard-Gates in FDSOI Processes

Kodai Yamada, Jun Furuta, Kazutoshi Kobayashi Kyoto Institute of Technology, Kyoto, Japan Phone, Fax +81-75-724-7410, E-mail kyamada@vlsi.es.kit.ac.jp

Abstract— In this paper we propose radiation-hardened flipflops (FFs) with small area and short delay overheads in a 65 nm fully depleted silicon on insulator (FDSOI) process. We designed two FFs composed of a guard-gate to eliminate SET pulses in the latch. Although the number of additional transistors is only two, one of the proposed FFs has high soft error tolerance at CLK = 1. Although the number of additional transistors is six, the other has high soft error tolerance at CLK = 0 and 1. We evaluated the radiation hardness of the newly designed structure by device simulations. Simulation results show that the stored values of the proposed FFs are not upset even though a charged particle with LET of 60 MeV-cm<sup>2</sup>/mghits.

### I. Introduction

According to process scaling, soft errors become a significant issue to threaten the reliability of a semiconductor chip since a stored value in strage elements such as flip-flops or SRAMs is flipped. When a radiated particle hits transistors, electron-hole pairs are generated in Si and collected at the drain region of transistors. The resulting perturbation in the output node voltage is called a single event transient (SET) pulse. A SET pulse will cause a soft error described as single event upset (SEU). To improve the tolerance of flipflops (FFs) against soft errors, several redundant FFs such as triple modular redundancy (TMR) [1] have been proposed for effective countermeasures. However, they have longer delay time and larger area, power consumption than conventional FFs. Fully depleted silicon on insulator (FDSOI) processes have higher tolerance for soft errors than a conventional bulk process without any performance overhead, because the buried oxide (BOX) layer prevents charge from being collected from substrate [2]. In this paper, we propose radiation-hardened FFs with small area and delay overheads in a 65 nm FDSOI process.

### II. Radiation-Hardened Flip-Flops

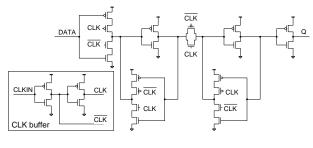

Fig. 1 shows a conventional DFF called the transmission gate FF (TGFF). It has no tolerance against soft errors.

#### A. Conventional Radiation Hardened Flip-Flop

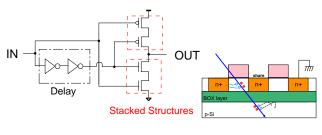

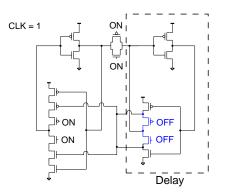

The guard-gate is an inverter with two inputs and one output as shown in Fig. 2 [3]. The signal coming to one of the inputs is delayed using two inverters. The guardgate eliminates all SET pulses which are shorter than the delay of two inverters since it has the one input delayed by two inverters. Moreover, the guard-gate has the stacked structure [4]. Stacked structure in FDSOI is isolated by the BOX layer. When a radiated particle hits on one transistor in the stacked structure, its output does not flip unless both transistors upset at the same time as shown in Fig. 3. Thus, the guard-gate has high soft-error tolerance.

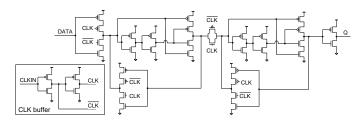

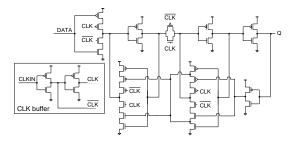

Figure 4 shows guard-gate FF (GGFF) [5]. The master latch (ML) and the slave latch (SL) contain the guard-gates. GGFF has about 100x stronger against SEU than DFF in a 16 nm bulk FinFET processes. However, it has larger area and delay overheads than conventional FFs because it has 12 more transistors than TGFF.

#### B. Proposed Radiation-Hardened Flip-Flop

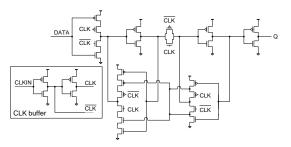

In Fig. 5, the proposed FF named the feedback recovery FF (FRFF) is shown. The guard-gate in FRFF is composed of the ML and the SL as shown in Fig. 6. Although the number of additional transistors is only two, FRFF has high soft error tolerance at CLK = 1. In Fig. 7, the proposed FF named the dual FRFF (DFRFF) is shown. DFRFF has two guard-gates. One guard-gate is implemented with the ML and the SL at CLK = 1 as like FRFF. The other is composed of the SL and the output inverter at CLK = 0. DFRFF has higher soft error tolerance than FRFF by adding two transistors.

#### **III. Simulation Results and Discussions**

## A. Soft-error Tolerance of Proposed FFs

We evaluate soft-error tolerance of DFRFF by device simulations at CLK = 1. The device simulations are carried

Fig. 1. Transmission-gate FF.

Fig. 2. Guard-Gate design. Fig. 3. Stacked structure.

Fig. 4. Guard-Gate FF.

Fig. 5. Proposed Feedback Recovery FF.

Fig. 6. Static condition of FRFF at CLK=1. Guard-gate in FRFF is composed of ML and SL.

Fig. 7. Proposed Dual Feedback Recovery FF.

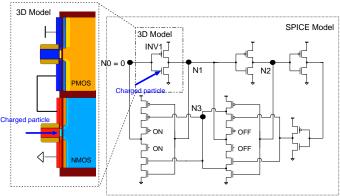

out using Sentauras from Synopsys. We constructed threedimensional structures of an inverter in a 65 nm FDSOI process with a thin BOX layer for the device simulations. Figure 8 depicts the schematic and the cross section on device simulations of DFRFF at CLK = 1.

NMOS transistors are more vulnerable to particle hits than PMOS transistors [6]. Thus, we evaluate soft-error tolerance of DFRFF when a particle hits an NMOS transistor. By setting the initial value of N0 to 0 V at CLK = 1, a particle

Fig. 8. Schematic and cross section on device simulations of ML. By setting the initial value of N0 to 0 V, a heavy ion hits at the NMOS transistor at  $V_{\rm DD}$  =1.2 V and 0.6 V.

with liner energy transfer (LET) of 60 MeV-cm<sup>2</sup>/mg hits at the NMOS transistor in INV1 as shown in Fig. 8. FFs have enough soft error tolerance in outer space if 60 MeV-cm<sup>2</sup>/mg particles do not cause any SEU. It is because particles with higher energy than 60 MeV-cm<sup>2</sup>/mg is much less than those below 60 MeV-cm<sup>2</sup>/mg in outer space [7].

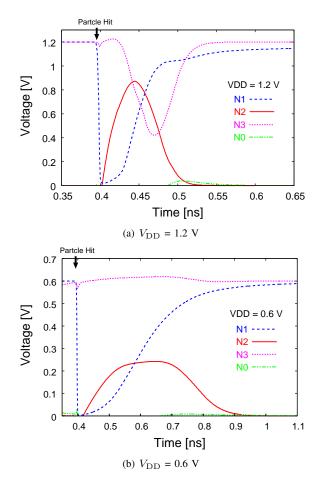

Figures 9 (a), (b) show simulation results at the supply voltage ( $V_{\rm DD}$ ) = 1.2 V and 0.6 V respectively. The stored value of DFRFF does not upset as shown in Fig. 9, even though a particle has LET of 60 MeV-cm<sup>2</sup>/mg which is 10x larger than the threshold LET of the conventional latch. N1, N2 and N3 are influenced by a charged particle hit at  $V_{\rm DD}$  = 1.2 V, but the amplitude of the SET pulse on N0 is attenuated to 0. In addition, only N1 and N2 are influenced by a charged particle at  $V_{\rm DD}$  = 0.6 V, because the delay time of two inverters at  $V_{\rm DD}$  = 0.6 V is 5.5x longer than that at  $V_{\rm DD}$  = 1.2 V.

These results prove that the proposed FFs have a high and enough resilience to soft-error to make them appropriate for highly reliable devices in outer space.

## B. Circuit Performance

We measure delay time and power consumption of FFs using SPICE simulations at  $V_{\rm DD}$ = 1.2 V. Table I indicates the simulation results of area, delay time, power at 10% data activity and the number of transistors. All values are normalized to those of TGFF. The values in parentheses are normalized to those of GGFF. The delay time and the area of GGFF are 2.2x longer and 1.4x bigger than that of TGFF, but the delay time and the area of FRFF are 52% shorter and 28% smaller than that of GGFF. FRFF also has less than 6% delay, area and power overheads than those of TGFF. The delay time and 20% smaller than those of GGFF. The power of the proposed FFs are most than 4% smaller than GGFF.

#### IV. Conclusion

We proposed two FFs which have soft-error resilience against a radiated particle with 60 MeV-cm<sup>2</sup>/mg. The proposed FRFF with high soft-error tolerance only at CLK = 1 has 52% shorter delay time and 28% smaller area than the

Fig. 9. SEU simulation results at CLK=1. N1 and N2, N3 are influenced by a particle hit in Fig. 8. Stored value of ML in DFRFF is not upset up to LET =  $60 \text{ MeV-cm}^2/\text{mg}$ .

#### TABLE I

Simulation results of area, D-Q delay, power and number of transistor of each FF at  $V_{DD}$ = 1.2 V. All values are normalized to those of TGFF. The values in parentheses are normalized to those of GGFF.

| FF    | D-Q delay | Area   | Power  | # of Tr. |

|-------|-----------|--------|--------|----------|

| TGFF  | 1         | 1      | 1      | 24       |

| GGFF  | 2.20      | 1.47   | 1.06   | 36       |

|       | (1)       | (1)    | (1)    |          |

| FRFF  | 1.06      | 1.06   | 1.03   | 26       |

|       | (0.48)    | (0.72) | (0.97) |          |

| DFRFF | 1.08      | 1.18   | 1.02   | 30       |

|       | (0.49)    | (0.80) | (0.96) |          |

GGFF. The proposed DFRFF with high soft-error tolerance at CLK = 0 and 1 has 51% shorter delay time and 20% smaller area than the GGFF.

Acknowledgment: The VLSI chip in this study has been fabricated in the chip fabrication program of VLSI Design and Education Center (VDEC) in collaboration with Renesas Electronics Corporation, Cadence Corporation, Synopsys Corporation and Mentor Graphics Corporation. This work is supported by JST-OPERA and JSPS KAKENHI Grant Number 15H02677 and JP17K14667.

REFERENCES

- D. G. Mavis and P. H. Eaton. Soft error rate mitigation techniques for modern microcircuits. In *IEEE Int. Rel. Physics Symp.*, pp. 216–225, 2002.

- [2] P. Roche, J.-L. Autran, G. Gasiot, and D. Munteanu. Technology downscaling worsening radiation effects in bulk: SOI to the rescue. In *IEEE Int. Electron Devices Meeting*, pp. 31.1.1–31.1.4, Dec. 2013.

- [3] A. Balasubramanian, B. L. Bhuva, J. D. Black, and L. W. Massengill. Rhbd techniques for mitigating effects of single-event hits using guardgates. *IEEE Trans. Nucl. Sci.*, 52(6):2531–2535, Dec. 2005.

- [4] A. Makihara, M. Midorikawa, T. Yamaguchi, Y. Iide, T. Yokose, Y. Tsuchiya, T. Arimitsu, H. Asai, H. Shindou, S. Kuboyama, and S. Matsuda. Hardness-by-design approach for 0.15 um fully depleted CMOS/SOI digital logic devices with enhanced SEU/SET immunity. *IEEE Trans. Nucl. Sci.*, 52(6):2524–2530, Dec. 2005.

- [5] H. Zhang, H. Jiang, T. R. Assis, D. R. Ball, K. Ni, J. S. Kauppila, R. D. Schrimpf, L. W. Massengill, B. L. Bhuva, B. Narasimham, S. Hatami, A. Anvar, A. Lin, and J. K. Wang. Temperature dependence of soft-error rates for ff designs in 20-nm bulk planar and 16-nm bulk finfet technologies. In 2016 IEEE International Reliability Physics Symposium (IRPS), pp. 5C–3–1–5C–3–5, Apr. 2016.

- [6] K. Yamada, H. Maruoka, J. Furuta, and K. Kobayashi. Sensitivity to soft errors of NMOS and PMOS transistors evaluated by latches with stacking structures in a 65 nm FDSOI process. In 2018 IEEE International Reliability Physics Symposium (IRPS), pp. P–SE.3–1–P– SE.3–5, Mar. 2018.

- [7] M. A. Xapsos, C. Stauffer, T. Jordan, J. L. Barth, and R. A. Mewaldt. Model for cumulative solar heavy ion energy and linear energy transfer spectra. *IEEE Trans. Nucl. Sci.*, 54(6):1985–1989, Dec. 2007.