PAPER

# Radiation-Hardened Flip-Flops in a 65 nm Bulk Process for Terrestrial Applications Coping With Radiation Hardness and Performance Overheads

Shotaro SUGITANI<sup>†a)</sup>, Ryuichi NAKAJIMA<sup>†</sup>, Keita YOSHIDA<sup>†</sup>, Student Members, Jun FURUTA<sup>†</sup>, Member, and Kazutoshi KOBAYASHI<sup>†</sup>, Senior Member

#### **SUMMARY**

Integrated circuits used in automotive or aerospace applications must have high soft error tolerance. Redundant Flip Flops (FFs) are effective to improve the soft error tolerance. However, these countermeasures have large performance overheads and can be excessive for terrestrial applications. This paper proposes two types of radiation-hardened FFs named Primary Latch Transmission gate FF (PLTGFF) and Feed-Back Gate Tri-state Inverter FF (FBTIFF) for terrestrial use. By increasing the critical charge  $(Q_{\rm crit})$  at weak nodes, soft error tolerance of them were improved with low performance overheads. PLTGFF has the 5% area, 4% delay, and 10% power overheads, while FBTIFF has the 42% area, 10% delay, and 22% power overheads. They were fabricated in a 65 nm bulk process. By  $\alpha$ -particle and spallation neutron irradiation tests, the soft error rates are reduced by 25% for PLTGFF and 50% for FBTIFF compared to a standard FF. In the terrestrial environment, the proposed FFs have better trade-offs between reliability and performance than those of multiplexed FFs such as the dual-interlocked storage cell (DICE) with larger overheads than the

**key words:** Soft error, Single Event Upset (SEU), critical charge,  $\alpha$ -particle, spallation neutron, Flip-Flop, terrestrial environment

#### 1. Introduction

Soft errors are one of the temporal failures that upset stored values in storage elements such as flip-flops (FFs) or SRAMs caused by a radiation strike. In the terrestrial environment,  $\alpha$ -particles and neutrons cause an upset of storage elements [1]. When a radiation particle hits on a chip, its ionizing effect generates electron-hole pairs in p-well and n-well. Generated electrons in the p-well are collected into the drain regions of NMOS transistors by funneling, drift, and diffusion [2]. The drain voltage is flipped by collected electrons. As the CMOS technology is down scaling, the amount of charge required to upset stored values in storage elements is gradually reduced due to the low supply voltage and small capacitance of transistors. So soft errors become more serious with technology down scaling [3]-[6]. In the terrestrial environment, high reliability is required for supercomputers, medical instruments, automotive driving technologies, and so on. Therefore, countermeasures against soft errors are necessary [7] [8]. To improve the soft error tolerance of FFs, several redundant circuits such as Triple Modular Redundancy FF (TMRFF) [9], Built-In Soft Error Resilience FF (BISERFF) [10]. Bistable Cross-coupled Dual Modular Redundancy FF (BCDMRFF) [11] and the Dual Interlocked Storage Cell FF (DICEFF) [12] [13] have been proposed. However, the number of transistors of these FFs is significantly larger than that of a standard FF (STDFF), and the performance overheads are large. Those redundant FFs may not be optimal for some applications. For example, due to higher radiation flux in outer space than in the terrestrial environment, storage-cell multiplication is an effective countermeasure in outer space. In the terrestrial environment, however, the possibility of soft errors is much lower than space. Thus multiplication is sometimes an excessive countermeasure. Therefore, it is necessary to take a countermeasure to bring a trade-off between soft error tolerance and circuit performance. In recent years, devicelevel and circuit-level soft error countermeasures have been considered as non-multiplexing countermeasures [14]–[17]. However, these countermeasures cannot be applied to conventional bulk process technologies, and it is necessary to develop countermeasures without multiplexing.

In this paper, we proposed two types of radiation-hardened FFs with low performance overheads by increasing the critical charge ( $Q_{\rm crit}$ ) [18]. We compared the soft error tolerance and the circuit performance of the proposed FFs with STDFF and DICEFF. Area, delay and power of these proposed FFs were larger than those of STDFF. However, these overheads were much smaller than DICEFF. Although the proposed FFs are weaker to soft errors than multiplexed FFs, they still have higher soft error tolerance than the STDFF to  $\alpha$ -particles and neutrons. These results revealed that the proposed FFs have better trade-offs between reliability and performance compared to STDFF and the redundant FFs for the terrestrial environment.

This paper is organized as follows. Section 2 describes soft error mechanism in a bulk process. Section 3 describes soft error suppression mechanisms and circuit performance of the proposed FFs. Section 4 describes the soft error tolerance of the proposed FFs evaluated by device simulations. Section 5 evaluates the soft error tolerance of the proposed FFs by  $\alpha$ -particle and neutron irradiation tests. Section 6 concludes this paper.

Manuscript received January 1, 2015. Manuscript revised January 1, 2015.

a) E-mail: ssugitani@vlsi.es.kit.ac.jp DOI: 10.1587/trans.E0.??.1

<sup>&</sup>lt;sup>†</sup>Graduate School of Science and Technology, Kyoto Institute of Technology, Japan

# 2. Principle of Soft Error in a Bulk Process

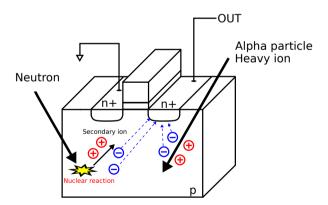

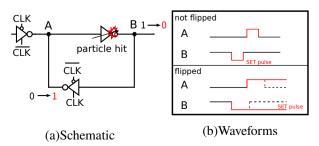

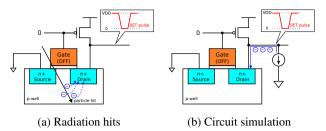

In the terrestrial environment, soft errors are caused by  $\alpha$ particles emitted from package material and neutron generated in the atmosphere by cosmic ray. When an  $\alpha$  particle penetrate into a silicon device, electron-hole pairs are generated by its ionizing effect along the particle track as show in Fig. 1. In contrast, neutrons do not directly produce electronholes pair. However, when a neutron collides with a Si atom in the substrate and cause a nuclear reaction, charged secondary particles are generated. Then the secondary particles generate electron-hole pairs. The generated minority carriers, electrons in the p-well, are collected in the drain region of the NMOS transistor by funneling, drifting, and diffusion. The drain output can be flipped by collected electrons transiently. Its radiation effect is termed as a single event effect (SEE). When radiation hits an inverter that constitutes a storage element such as a latch, charges are collected in the diffusion region and a single event transient (SET) pulse is generated at the output of the inverter (node B) as shown in Fig. 2. If a SET pulse is injected to the next gate and the output value (node A) is flipped before the output value of the inverter (node B) returns to the correct value, the stored value of the storage element is flipped. This inversion of the stored value of a storage element is called a soft error. The soft error rate of silicon devices increases with process scaling because process scaling reduces the gate capacitance of the transistor, making the output more easily to flip.

Fig. 1: Single event effect on a silicon devices.

Fig. 2: Soft error mechanism in a latch.

#### 3. Proposed Radiation Hardened FFs Design

#### 3.1 Conventional FF

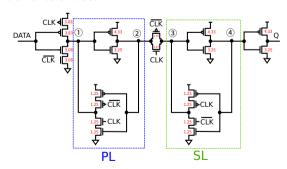

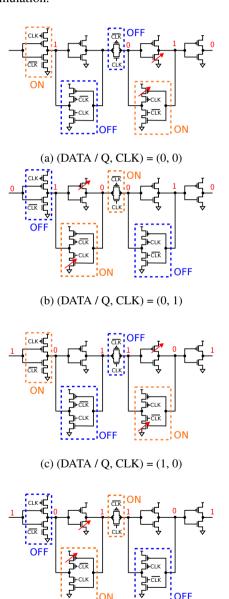

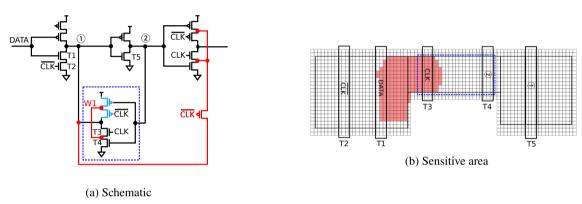

Fig. 3 shows STDFF without any radiation hardness. We focus on critical charge ( $Q_{\rm crit}$ ) calculated by circuit simulations.  $Q_{\rm crit}$  represents the minimum amount of charge at which the stored value of a latch is flipped. Fig. 4 shows the schematic to obtain  $Q_{\rm crit}$  of the NMOS and PMOS transistors. By connecting the current sources as shown in the Fig. 4, charge collection into the diffusion region can be simulated as shown in Fig. 5. Soft errors occur due to electrons in NMOS and holes in PMOS [19]. Table 1 shows the relationship between the circuit nodes and the states of DATA / Q and CLK. Fig. 6 shows the locations of soft errors in STDFF for each condition.

The current source used for the simulation is the single exponential model in Eq. (1) [20]. *T* in Eq. (1) refers to the time constant determined by a process node. *T* is set to 20 ps, corresponding to a 65 nm process [21].

$$I(t) = Q \frac{2}{T\sqrt{\pi}} \sqrt{\frac{t}{T}} \exp\left(-\frac{t}{T}\right) \tag{1}$$

Table 2 shows  $Q_{\rm crit}$  of NMOS and PMOS transistors of the evaluated FFs.  $Q_{\rm crit}$  of PMOS transistors is larger than NMOS transistors at each node. Soft errors are more likely to occur on NMOS transistors than on PMOS transistors because the mobility of electrons is larger than that of holes [21]. In [22], it has been reported that increased  $Q_{\rm crit}$  improved soft-error tolerance in a 130 nm bulk process. Therefore, we considered countermeasures to increase the  $Q_{\rm crit}$  on NMOS transistors. In STDFF, the node ① and ③ are weaker to soft errors than the other nodes because the output current of the clocked inverter is low. The proposed FFs increase  $Q_{\rm crit}$  at the vulnerable nodes to improve soft-error tolerance.

Fig. 3: Standard FF (STDFF)

Fig. 4: Schematic to obtain  $Q_{\text{crit}}$  of each transistors.

Fig. 5: Charge collection is emulated by a current source in circuit simulation.

(d) (DATA / Q, CLK) = (1, 1)Fig. 6: Locations to cause soft errors in STDFF for each condition

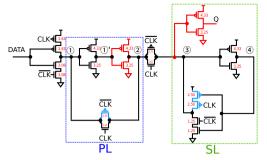

#### 3.2 PLTGFF

Fig. 7 shows one of the proposed FFs named Primary Latch

Table 1: Relationship between the measurement nodes and the input values. (a)NM(OC 4man alata m

| (a)NIVIOS transistor |       |        |        |  |  |

|----------------------|-------|--------|--------|--|--|

| (DATA / Q, CLK)      | STDFF | PLTGFF | FBTIFF |  |  |

| (0, 1)               | 1     | 1, 2   | 1      |  |  |

| (1, 1)               | 2     | 1'     | 2      |  |  |

| (0, 0)               | 4     | 3      | 3      |  |  |

| (1, 0)               | 3     | 4      | 4      |  |  |

| (b)PMOS transistor |                                  |     |   |  |

|--------------------|----------------------------------|-----|---|--|

| (DATA / Q, CLK)    | (DATA / Q, CLK)   STDFF   PLTGFF |     |   |  |

| (0, 1)             | 2                                | 1'  | 2 |  |

| (1, 1)             | 1                                | 1,2 | 1 |  |

| (0, 0)             | 3                                | 4   | 4 |  |

| (1, 0)             | 4                                | 3   | 3 |  |

Table 2:  $Q_{crit}$  of all internal nodes in the standard and proposed FFs. (a) NMOS transistor

#### FF $Q_{\text{crit}}$ [fC] STDFF 3.7 11 3.0 11 PLTGFF 5.7(+2.0)8.9 14(+3.0)8.7(-2.3)4.6(+1.6)**FBTIFF** 8.9(+5.2)

9.4(-1.8)

20(+17)

17(+6.0)

# (b) PMOS transistor

| FF     | $Q_{ m crit}$ [fC] |    |          |           |           |

|--------|--------------------|----|----------|-----------|-----------|

|        | 1                  | 1' | 2        | 3         | 4         |

| STDFF  | 4.5                | -  | 13       | 3.9       | 12        |

| PLTGFF | 5.8(+1.3)          | 11 | 16(+3.0) | 4.5(+0.6) | 11(-1.0)  |

| FBTIFF | 5.8(+1.3)          | -  | 11(+0)   | 7.4(+3.5) | 7.6(-4.4) |

Transmission gate FF (PLTGFF). In PLTGFF, the circuit topology is revised to increase  $Q_{crit}$ . The number of the passing logic gates from node 2 to Q is reduced to two and then the increment of CLK-Q delay is suppressed. The connection of the last gate inverter is moved from node 4 to node  $\Im$ , so the parasitic capacitance and  $Q_{crit}$  at node  $\Im$ is increased. In PL, the clocked inverter is replaced with the transmission gate and the inverter in red is added. These changes result in exactly the same circuit operation as STDFF without increasing the number of transistors and suppress circuit performance overheads. The gate width of the PMOS transistors in blue is doubled, which increases the number of holes that capture the electrons collected in the diffusion region [22].

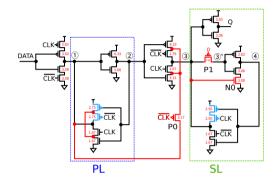

#### **FBTIFF** 3.3

Fig. 8 shows the other proposed FF named Feed-Back Tristate Inverter FF (FBTIFF). FBTIFF is also implemented to increase  $Q_{\rm crit}$  as in PLTGFF. The CLK-Q delay of FBTIFF is suppressed by revising the circuit topology as the similar manner as PLTGFF. The SET pulse generated at node 3 can be suppressed by adding the PMOS pass transistor (P1) [23]. However, it significantly increases static power because of the drain node of the normally-on PMOS pass-transistor.

Fig. 7: Primary Latch Transmission Gate FF (PLTGFF)

Fig. 8: Feed-Back Tri-state Inverter FF (FBTIFF)

Fig. 9: The suppression mechanism of static power in FBTIFF.

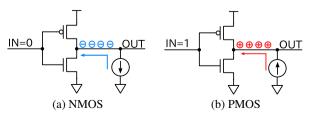

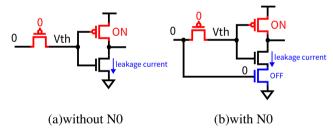

Fig. 9 shows the suppression mechanism of static power. In the PMOS pass transistor, when the drain voltage is 0, a voltage drop of Vth occurs, and then the source voltage becomes Vth as shown in Fig. 9 (a). Hence, when node 3 is 0, leakage current flows in the next-stage NMOS, and then the static power increases. Therefore, the cascaded NMOS transistor (N0) is added to the SL inverter as shown in Fig. 9 (b). When node 3 goes to 0, N0 turns off, so the leakage current does not flow and the static power is Table 3 shows static power with or without N0. These results show that static power can be reduced by more than 99% due to the cascaded NMOS transistor. Both of the clocked inverters in PL and placed between PL and SL are split into the inverter and the transmission gate. The clock signal input transistors, which are connected in series in the initial structure, are connected in parallel in revised structure by the additional wiring. The parallel connection lowers the overall resistance of these logic gates. Therefore, the amount of current flowing to the output increases and  $Q_{\rm crit}$  also increases [22]. The pass transistor (P0) is added

Table 3: Difference in static power with or without N0 (Normalized to STDFF).

| FF                  | Static power |

|---------------------|--------------|

| STDFF               | 1.00         |

| FBTIFF              | 1.55         |

| FBTIFF (without N0) | 212          |

between node (1) and the tri-state inverter between PL and SL. Connecting the tri-state inverter to node (1) increases the amount of current flowing into node (1). As a result,  $Q_{crit}$ at node (1) also increases. If an error occurs in the tri-state inverter connecting PL and SL, a SET pulse is injected to node (1) through the additional wiring, and the stored value of PL is flipped. By adding P0, the SET pulses generated by the tri-state inverter between SL and PL can be suppressed as in the case with P1. The input of P0 is set to  $\overline{\text{CLK}}$  so as to disconnect node (1) with the intermediate nodes of the tristate inverter connecting PL and SL when CLK = 0. Therefore, when the state of DATA changes, node ① can be easily flipped by an input tri-state inverter, thus reducing the increase in D-Q delay. Node ① is fully pull-downed by the clocked inverter in PL even though P0 was added. Therefore. the leak current is negligible in the inverter. The gate width of the PMOS transistors are also doubled as PLTGFF. These revisions increase the amount of current flowing into node (1) and  $Q_{\rm crit}$ .

As shown in Table 2 (a),  $Q_{crit}$  of NMOS transistors increases at most nodes in PLTGFF. However,  $Q_{crit}$  at node 4decreases because the gate capacitance of the last-stage inverter is removed. In FBTIFF, Qcrit at node @ increases despite of removing the last-gate inverter. If radiation strikes the inverter of the latch, a SET pulse is generated at node ④. In this case, the state of the input of the inverter (STDFF : node ③, FBTIFF: node ③') must be inverted before the SET pulse of node 4) returns to its correct value so as to completely flip the stored value in the latch. Therefore, the shorter the delay time from node 4 to the input of the inverter, the more likely a stored value of latch will be flipped. The delay time from node 4 to the input of the inverter is longer for FBTIFF than for STDFF due to the additional P1. Therefore,  $Q_{\text{crit}}$  also increases because the width of the SET pulse required to flip the stored value increases. However,  $Q_{\text{crit}}$  at node 2 decreases by the increased drive strength of the clocked inverter. Adding wire to the clocked inverter reduces the overall resistance of the gate. Thereby, the delay time from node 2 to node 1 is reduced. Therefore, the width of the SET pulse required to flip the stored value can be reduced, and  $Q_{crit}$  at node ② decreases. At PMOS transistors,  $Q_{\rm crit}$  at each node increase while decreasing at node 4in FBTIFF. Since the NMOS transistor (N0) is stacked, the amount of current flowing to node 4 and  $Q_{\text{crit}}$  becomes small. However, because of the much increase in  $Q_{crit}$  of the NMOS transistors, the soft-error tolerance at node 4 is expected to be improved.

Table 4: Simulation results of area, D-Q delay, CLK-Q delay, setup time, hold time and power of the conventional and proposed FFs at  $V_{DD} = 1.2$  V. (Normalized to STDFF). The number of transistors does not include clock buffers.

| FF                | # of Tr. | Area | D-Q delay | CLK-Q delay | Setup time | Hold time | Power |

|-------------------|----------|------|-----------|-------------|------------|-----------|-------|

| STDFF             | 20       | 1.00 | 1.00      | 1.00        | 1.00       | 1.00      | 1.00  |

| PLTGFF (proposed) | 20       | 1.05 | 1.04      | 0.94        | 3.18       | 0.94      | 1.10  |

| FBTIFF (proposed) | 25       | 1.42 | 1.10      | 0.98        | 3.80       | 0.96      | 1.22  |

| DICEFF            | 42       | 2.95 | 2.28      | 1.92        | 8.69       | 0.67      | 2.86  |

Table 5: Cross Section of the node (1) and (3).

|                   | Cross Section [cm <sup>2</sup> /ion] |                       |  |

|-------------------|--------------------------------------|-----------------------|--|

|                   | node ①                               | node ③                |  |

| STDFF             | $1.90 \times 10^{-9}$                | $2.02 \times 10^{-9}$ |  |

| PLTGFF (proposed) | $1.75 \times 10^{-9}$                | $1.20 \times 10^{-9}$ |  |

| FBTIFF (proposed) | $0.976 \times 10^{-9}$               | 0                     |  |

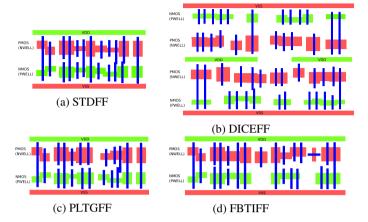

#### 3.4 Circuit performance

Fig. 10 shows the simplified layout patterns of the fabricated FFs in a 65 nm bulk process with 9 wire pitches. In all layouts, well taps are placed under the VDD and VSS straps. We calculated area, delay time and power consumption of those FFs using circuit simulations at the standard voltage (V<sub>dd</sub>) of 1.2 V. These performance of STDFF, proposed FFs, and DICEFF are shown in Table 4. Power is evaluated with the activation rate of 10% and is averaged between D = 0 and 1. The CLK frequency is 1 GHz. It is calculated as the product of the standard voltage, 1.2 V, and the average value of the current estimated by circuit-level simulations. These values are normalized to STDFF. PLTGFF has the area, D-Q delay, and power overheads by 5%, 4%, and 10% respectively. FBTIFF has the area, D-Q delay, and power overheads by 42%, 10%, and 22% respectively. According to Table 4, the setup times of the proposed FFs are longer than STDFF. Fig. 11 shows the signal path from node ① to the pass transistor between PL and SL. The number of logic gates from node ① to the pass transistor is one for STDFF and two for the proposed circuits. Therefore, the delay time is longer and the setup time of the proposed circuits increased. On the other hand, CLK-Q delay of the proposed FFs is shorter than STDFF because of the circuit topology optimizations discussed in Section 3.2. Therefore, the proposed FFs are able to suppress D-Q delay. The area of FBTIFF increases by 42% compared to STDFF due to the additional PMOS pass transistors. The proposed FFs have a smaller number of transistors than conventional radiation hardened FFs such as DICEFF and much lower performance overheads.

#### 4. Soft Error Tolerance Evaluated by Device Simulation

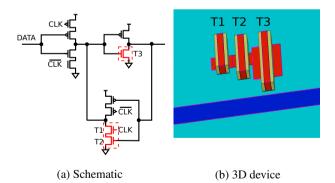

In this section, soft error rates at vulnerable nodes were estimated by TCAD simulations. 3D TCAD simulations were carried out using Synopsys Sentaurus to evaluate the radiation hardness of the proposed FFs.

# 4.1 Simulation Setup

In the simulation results of  $Q_{crit}$ , the variation of error rates

Fig. 10: Simplified layout patterns of STDFF, DICEFF and the proposed FFs. They are designed in 9 wire pitches. DICEFF is designed in the double height.

Fig. 11: The signal path from node ① to the pass transistor that connects PL and SL.

Fig. 12: Schematic and 3D device structure on TCAD.

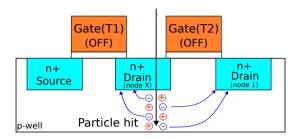

due to the increase in diffusion area was not taken into account. Therefore, to investigate the impact of diffusion area on soft errors, a 3D structure was constructed using a 65 nm bulk process for TCAD simulations. NMOS transistors in PL and SL are modeled in the device level, while the other transistors are modeled in the circuit level to reduce simulation time. The 3D device structures are shown in Fig. 12. We constructed 3D transistor models to fit static characteristics of SPICE simulation models distributed from a fabri-

Fig. 13: Shape of sensitive area in PL of STDFF by heavy ions with LET of 1.4 MeV·cm<sup>2</sup>/mg.

Fig. 14: Shape of sensitive area in PL of FBTIFF by heavy ions with LET of 1.4 MeV·cm<sup>2</sup>/mg.

cation company. Current and capacitance characteristics on TCAD simulations decreased relative errors between TCAD and SPICE simulations to less than 10.4% in the region of  $|V_{as}| > 0.6 \text{ V}$ .

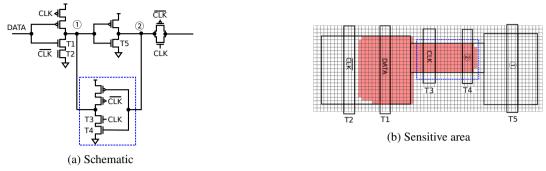

In this paper, we estimate soft error tolerance by the cross section (CS). The CS is defined as a sensitive area for soft errors. A smaller CS indicates greater resistance to soft errors [24]. In order to evaluate the CS, the 3D model transistors are split into a 20 nm square grid, and heavy ions are irradiated at the center of every grid. A Heavy ion with linear transfer (LET) of 1.4 MeV·cm²/mg, which is the maximum LET of alpha particles from packages or bonding wires [25], strikes the 3D model transistors.

### 4.2 Simulation results

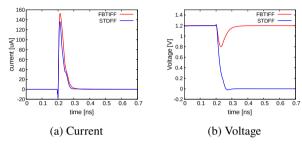

Table 5 shows CS values at the node 1 and 3, which are vulnerable to soft errors in STDFF. The proposed FFs, especially FBTIFF, can reduce the CS of vulnerable nodes. In PL, CS is reduced by increasing  $Q_{\rm crit}$  and the additional wire. Figs. 13 and 14 show the CSs in the PL of STDFF and FBTIFF. In FBTIFF, the clocked inverter in PL is split into the inverter and transmission gate to increase  $Q_{\rm crit}$ . Electrons generated by a particle strike combine with holes in the PMOS transistor through the additional wire (W1). Therefore, soft errors are less likely to occur in the diffusion between T3 and T4. CS is also reduced between T1 and T2 although STDFF and FBTIFF have the same structure of T1 and T2. This is because of the difference of  $Q_{\rm crit}$  at node 1

and the decrease in charge collection due to the distance between the drain region and the irradiation location. The diffusion region between T1 and T2 is defined as node X. As shown in Fig. 15, when a radiation particle strikes between T1 and T2, charges are generated and collected at node X and node (1). When the amount of charges collected in each diffusion area exceeds a certain amount, both of T1 and T2 are turned on and an error occurs. The farther the collision location of radiation becomes, the less charge is collected on node (1) and less likely to flip the stored value. Fig. 16 shows the current and voltage waveforms at node ① when heavy ions are irradiated at the midpoint between T1 and T2. As can be seen from Fig. 16 (a), there is no significant difference in the amount of current at node ①. Therefore, the amount of charge collected at node ① is same for the both FFs. However, because of the increased  $Q_{crit}$  at node ①, the voltage does not drop to the threshold value and the stored value is not flipped in FBTIFF as shown in Fig. 16 (b).

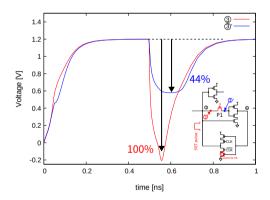

CS at the node 3 is  $0 \text{ cm}^2/\text{ion}$  in FBTIFF by the PMOS pass transistor (P1). Fig. 17 shows simulation results of voltage waveforms by a heavy-ion strike. The SET pulse is suppressed by 56% after passing through P1.

#### 5. Experimental Results

# 5.1 Setup of irradiation tests

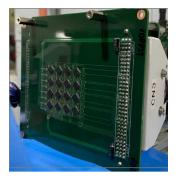

The test chips were fabricated in a 65 nm bulk process. All FFs are implemented as shift registers. FFs are initialized

Fig. 15: Charge collection in case of radiation strike between T1 and T2.

Fig. 16: The current and voltage waveforms at node 1 when heavy ions (LET = 1.4 MeV·cm<sup>2</sup>/mg) are irradiated at the midpoint between T1 and T2.

Fig. 17: TCAD simulation results. node ③ and ③' are influenced by a particle hits. P1 reduces the SET pulse by 56%.

with the same value, so DATA and Q have the same value. We evaluated soft-error tolerance by  $\alpha$ -particle and neutron irradiation tests. The irradiation tests were conducted as follows.

- 1. Initialize serially-connected FFs by all 0 or 1.

- 2. Stabilize CLK to 0 or 1.

- 3. Expose  $\alpha$ -particles or neutrons to FFs.

- 4. Read out stored data of FFs.

- 5. Count the number of upsets.

- 6. Repeat 1 5 for four (Q, CLK) conditions.

Soft-error rates (SERs) are calculated using Eq. (2).

SER [FIT/Mbit] =

$$\frac{N_{\text{error}} \times 10^9 \times 1024^2}{N_{\text{FF}} \times F_{\text{acc}} \times t}$$

(2)

$F_{\rm acc}$ : Acceleration factor

Fig. 18:  $\alpha$ -irradiation tests. An  $\alpha$  source was placed on the test chip.

Fig. 19: Terrestrial neutron spectrum and that from spallation neutron source at RCNP.

t: Measurement time [hours]

$N_{\text{error}}$ : Number of errors  $N_{\text{FF}}$ : Number of FFs

$\alpha$ -particle irradiation tests were carried out using a 3 MBq  $^{241}$ Am source, whose size is 9.5  $\times$  9.5 mm. As shown in Fig. 18, the  $\alpha$ -particle source is placed on the test chip. We exposed  $\alpha$ -particles to FFs for 30 seconds. The attenuation rate of  $\alpha$ -rays depends on the distance between  $\alpha$  source and test chip. The distance between the  $\alpha$  source and the chip is 0.9 mm.  $F_{\rm acc}$  of  $\alpha$ -particle is calculated as Eq. (3). The alpha dose emitted from the package is assumed to be 0.001 count/cm²/hour for Ultra Low Alpha grade [26].

$$F_{\rm acc} = \frac{1.5 \times 10^6 \text{ count/sec} \times 3600 \times 1/0.95^2 \text{ cm}^{-2}}{0.001 \text{ count/cm}^2/\text{hour}} \times 0.9$$

$$= 5.4 \times 10^{12} \tag{3}$$

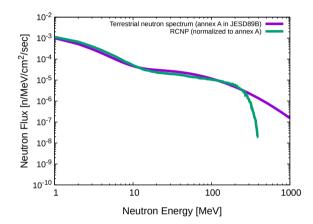

Neutron irradiation tests were conducted at the research center for nuclear physics (RCNP), Osaka University, Japan [27]. Fig. 19 shows the normalized neutron beam spectrum with the terrestrial neutron spectrum defined in JESD 89B (12.96 n/cm<sup>2</sup>·h) [28]. The average  $F_{\rm acc}$  is  $1.0 \times 10^8$ . We exposed neutrons to FFs for 1800 seconds. In order to increase the number of errors in the limited measurement time, 32 test chips were measured simultaneously as shown in Fig. 20.

Fig. 20: Simultaneous measurement of 32 test chips at the neutron irradiation test. 16 chips are mounted on the DUT board, and two DUT boards were simultaneously irradiated.

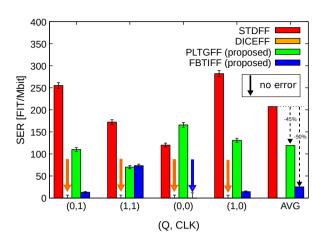

#### 5.2 $\alpha$ -particle irradiation

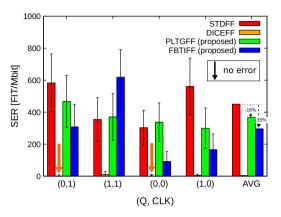

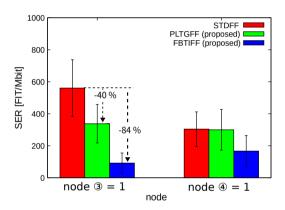

Fig. 21 shows  $\alpha$ -SER of the proposed FFs with error bars of 95% confidence at  $V_{dd}$  = 1.2 V. The  $\alpha$ -SER of DICEFF is almost zero. The proposed FFs have improved soft-error tolerance compared to STDFF. However, PLTGFF has lower soft error tolerance than STDFF when (Q, CLK)=(0, 0). As shown in Figs. 3, 7 and 8, the position of the inverter connecting to the output Q is different between the STDFF and the proposed FFs. Therefore, the relationship between the measurement node and (Q, CLK) is different between STDFF and the proposed FFs. Fig. 22 shows the  $\alpha$ -SER considering the difference of (Q, CLK) between STDFF and the proposed circuits. To facilitate comparison of the results of the STDFF and the proposed circuits, Fig. 22 shows the SER when the value of each node is 1. According to the result, the  $\alpha$ -SER of PLTGFF is 42% smaller than STDFF when node  $\Im = 1$ . The  $\alpha$ -SER of FBTIFF is 0 when node  $\Im$ = 1. Therefore, the proposed FFs have improved soft-error tolerance at the vulnerable nodes (node ① and ③) compared to STDFF because of increased  $Q_{crit}$ . The overall SERs are 45% lower for PLTGFF and 90% lower for FBTIFF than STDFF.

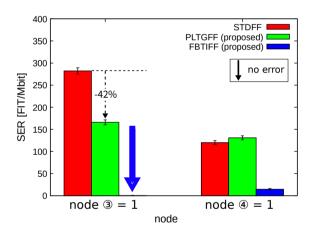

## 5.3 Neutron irradiation

Fig. 23 shows neutron-SER (n-SER) of the proposed FFs with error bars of 95% confidence at  $V_{dd} = 1.2 \text{ V}$ . The n-SER of DICEFF is almost zero, indicating that it is sufficiently resistant to terrestrial neutrons. Compared to STDFF, the soft-error tolerance of FBTIFF is improved at (Q, CLK) = (0,0), (0,1), and (1,0) while FBTIFF was weak at (Q,CLK)= (1, 1) due to insufficient  $Q_{\text{crit}}$ . The soft-error tolerance of PLTGFF is improved at (Q, CLK) = (0, 1) and (1, 0). However, PLTGFF is weak at (Q, CLK) = (0, 0) and (1, 1). From Table 1, when (O, CLK) = (1, 1), a soft error occurs in the NMOS drain region at node ② in STDFF and at node ①' in PLTGFF. From Table 2 (a),  $Q_{\rm crit}$  of PLTGFF is less than that of STDFF in (Q, CLK) = (1, 1). When CLK = 0, the relationship between the measurement node and (Q, CLK) is different between STDFF and the proposed FFs as described in Section 5.2. Fig. 24 shows the n-SER results considering

Fig. 21:  $\alpha$ -SER under four (Q, CLK) states and average  $\alpha$ -SER. Error bars are within 95% confidence. These results assume the use of the super ultra low alpha (SULA) package (0.001 cph/cm<sup>2</sup>). Note that DICEFF has no error at all conditions.

Fig. 22:  $\alpha$ -SER results considering the difference in (Q, CLK) between STDFF and the proposed circuits. To facilitate comparison of the results of the STDFF and the proposed circuit, it shows the error rate for each node when the value of each node is 1.

the difference in (Q, CLK) between STDFF and the proposed circuits. According to the result, the n-SER are 42% lower for PLTGFF and 84% lower for FBTIFF than STDFF when node  $\mathfrak{J}=1$ . The overall SERs are 18% lower for PLTGFF and 35% lower for FBTIFF than STDFF.

# 5.4 Discussions

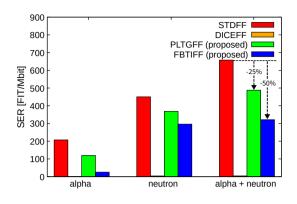

Fig. 25 shows the sum of  $\alpha$ - and n-SERs of STDFF, DICEFF, and the proposed FFs. Each SER is the average of all four (Q, CLK) conditions. For all FFs, n-SER is larger than  $\alpha$ -SER. Thus, the error rate due to neutrons is higher than due to  $\alpha$  particles in the terrestrial environment. In [29], it was reported that  $\alpha$  particles have a higher rate of change in SER

Fig. 23: n-SER under four (Q, CLK) states and average. Error bars are within 95% confidence.

Fig. 24: n-SER results considering the difference in (Q, CLK) between STDFF and the proposed circuits. To facilitate comparison of the results of the STDFF and the proposed circuit, it shows the error rate for each node when the value of each node is 1.

with respect to  $Q_{\rm crit}$  than neutrons due to the difference of the LET of the particles. Therefore, the tolerance to  $\alpha$  particle irradiation of the proposed FFs is better than that to neutron irradiation. Both  $\alpha$ - and n-SERs of DICEFF are almost zero, ensuring sufficient soft-error tolerance. The proposed FFs are not as soft-error tolerant as DICEFF. However, the SERs in the terrestrial environment are reduced by 25% for PLTGFF and 50% for FBTIFF compared to STDFF.

Fig. 26 shows the 2-dimensional charts of plotting performance overheads and soft-error tolerance of those FFs. The value of SER is the sum of  $\alpha$ - and n-SER. The SER and performances are normalized to the STDFF value. The numerical values in the graph indicate the distance from the origin. The smaller they are, the better the trade-off between performances and reliability becomes. The figure shows that DICEFF has the highest soft-error tolerance with relatively large performance overhead. In the terrestrial environment, the proposed FFs have better trade-offs between reliability and performance compared to DICEFF and STDFF. In par-

Fig. 25: Sum of  $\alpha$ - and n- SER. Each SER is the average of all four (O, CLK) conditions.

Fig. 26: 2 dimensional charts of soft error tolerance and each performance (Area, D-Q delay, Power). SER is the sum of  $\alpha$ -SER and n-SER. SER and each performance are normalized by the STDFF value.

ticular, PLTGFF is better in terms of area, and FBTIFF is better in terms of delay in the terrestrial environment.

These circuit structures could be applied to other softerror countermeasure methods. For example, a countermeasure was proposed to improve soft error tolerance by modifying the latch structure in the multiplexing circuit [30]. TMRFF triples the STDFF. By using the proposed circuit instead of STDFF, further improvement of soft-error tolerance in outer space is expected. Furthermore, in the FDSOI process, the carrier collection efficiency is less than the bulk process [31]. Thus the proposed countermeasures are especially effective to the FDSOI process. Adapting the proposed circuit to these countermeasures is expected to improve softerror tolerance further not only in the terrestrial environment but also in outer space.

#### 6. Conclusion

Redundant flip flops are strong against soft errors with large performance overheads. We proposed radiation-hardened FFs for terrestrial applications balancing performance overheads and radiation hardness.  $Q_{crit}$  at the vulnerable nodes are increased by changing circuit topologies with additional transistors and wires. These proposed FFs have fewer transistors and have lower performance overhead than conventional multiplexed circuits. The proposed FFs can suppress the D-Q delay increase less than 10%. The performance overheads of the proposed FFs are smaller than DICEFF. We fabricated the proposed FFs in a 65 nm bulk process. By  $\alpha$ and neutron irradiation tests, PLTGFF and FBTIFF reduce soft error rates by 25% and 50%, respectively. Although the proposed FFs are weaker for soft errors than DICEFF, they have better trade-offs between reliability and performance than DICEFF and STDFF.

#### Acknowledgement

The authors would like to thank to Prof. M. Fukuda of RCNP and all the other RCNP members for our neutron-beam experiments. EDA tools used for simulations and layout design were provided by Cadence Design Japan Ltd, Synopsys Japan Ltd, and Siemens EDA Japan Ltd through d.lab-VDEC of the University of Tokyo. This work is partly supported by JST Moonshot R&D Grant Number JPMJMS226A.

# Appendix: Netlists

The netlists of the three circuits used for circuit simulation are shown below. UW is the value of the normalized gate width.

#### **STDFF**

.SUBCKT STDFF CP D Q VDD VSS MM22 net21 net49 VSS VSS nch l=60n UW=1.50 MM20 net49 CP VSS VSS nch l=60n UW=1.62 MM19 net018 net21 net28 VSS nch l=60n UW=1.66 MM28 Q net33 VSS VSS nch 1=60n UW=3.25 MM14 net33 net28 VSS VSS nch l=60n UW=3.25 MM27 net43 net33 VSS VSS nch l=60n UW=1.25 MM24 net28 net49 net43 VSS nch l=60n UW=1.25 MM9 net45 net018 VSS VSS nch l=60n UW=1.25 MM6 net013 net21 net45 VSS nch l=60n UW=1.25 MM4 net018 net013 VSS VSS nch l=60n UW=3.25 MM3 net47 net49 VSS VSS nch l=60n UW=3.08 MMO net013 D net47 VSS nch l=60n UW=3.08 MM23 net21 net49 VDD VDD pch l=60n UW=2.16 MM21 net49 CP VDD VDD pch l=60n UW=2.16 MM18 net018 net49 net28 VDD pch l=60n UW=1.79 MM29 Q net33 VDD VDD pch l=60n UW=4.33 MM15 net33 net28 VDD VDD pch l=60n UW=4.33 MM26 net28 net21 net44 VDD pch l=60n UW=1.25 MM25 net44 net33 VDD VDD pch l=60n UW=1.25 MM8 net013 net49 net46 VDD pch l=60n UW=1.25 MM7 net46 net018 VDD VDD pch l=60n UW=1.25 MM5 net018 net013 VDD VDD pch l=60n UW=4.33 MM2 net013 D net48 VDD pch l=60n UW=3.83 MM1 net48 net21 VDD VDD pch l=60n UW=3.83 .ENDS

#### **PLTGFF**

.SUBCKT PLTGFF CP D Q VDD VSS MM22 net21 net49 VSS VSS nch l=60n UW=1.50 MM20 net49 CP VSS VSS nch l=60n UW=1.62 MM19 net026 net21 net28 VSS nch l=60n UW=1.66 MM28 O net28 VSS VSS nch 1=60n UW=3.25 MM14 net33 net28 VSS VSS nch l=60n UW=3.25 MM27 net43 net33 VSS VSS nch l=60n UW=1.25 MM24 net28 net49 net43 VSS nch l=60n UW=1.25 MM32 net026 net25 VSS VSS nch 1=60n UW=3.25 MM31 net16 net21 net026 VSS nch l=60n UW=1.25 MM4 net25 net16 VSS VSS nch l=60n UW=3.25 MM3 net47 net49 VSS VSS nch l=60n UW=3.08 MMO net16 D net47 VSS nch l=60n UW=3.08 MM23 net21 net49 VDD VDD pch l=60n UW=2.16 MM21 net49 CP VDD VDD pch l=60n UW=2.16 MM18 net026 net49 net28 VDD pch l=60n UW=1.70 MM29 Q net28 VDD VDD pch l=60n UW=4.33 MM15 net33 net28 VDD VDD pch l=60n UW=4.33 MM26 net28 net21 net44 VDD pch l=60n UW=2.50 MM25 net44 net33 VDD VDD pch l=60n UW=2.50 MM30 net16 net49 net026 VDD pch l=60n UW=2.50 MM33 net026 net25 VDD VDD pch 1=60n UW=4.33 MM5 net25 net16 VDD VDD pch l=60n UW=4.33 MM2 net16 D net48 VDD pch l=60n UW=3.83 MM1 net48 net21 VDD VDD pch l=60n UW=3.83 .ENDS

## **FBTIFF**

.SUBCKT FBTIFF CLK D Q VDD VSS node1

node1n

MM43 node4 net52 net046 VSS nch 1=60n UW=3.08

MM9 net046 node3 VSS VSS nch 1=60n UW=3.08

MM7 net042 node4 VSS VSS nch 1=60n UW=1.66

MM65 net048 node1n VSS VSS nch 1=60n UW=1.66

MM0 node1 D net125 VSS nch 1=60n UW=3.08

MM3 net125 cn VSS VSS nch 1=60n UW=3.08

MM4 node1n node1 VSS VSS nch 1=60n UW=3.08

MM42 node2 node1n VSS VSS nch 1=60n UW=3.08

MM24 node3 cn net042 VSS nch 1=60n UW=1.66

MM66 node1 cp net048 VSS nch 1=60n UW=1.66

MM68 Q node3 VSS VSS nch 1=60n UW=1.66

MM28 Q node3 VSS VSS nch 1=60n UW=3.08

MM19 node2 cp node3 VSS nch 1=60n UW=1.66

MM20 cn CLK VSS VSS nch l=60n UW=1.62 MM22 cp cn VSS VSS nch 1=60n UW=1.50 MM40 node3 VSS net52 VDD pch l=60n UW=1.00 MM8 node4 net52 VDD VDD pch 1=60n UW=3.83 MM6 net127 node4 VDD VDD pch l=60n UW=2.50 MM1 net124 cp VDD VDD pch l=60n UW=3.83 MM2 node1 D net124 VDD pch l=60n UW=3.83 MM5 node1n node1 VDD VDD pch 1=60n UW=4.33 MM33 node2 node1n VDD VDD pch 1=60n UW=4.33 MM46 node1 cn node2 VDD pch l=60n UW=3.16 MM72 net048 node1n VDD VDD pch l=60n UW=2.75 MM26 node3 cp net127 VDD pch l=60n UW=2.50 MM29 Q node3 VDD VDD pch 1=60n UW=3.83 MM18 node2 cn node3 VDD pch l=60n UW=1.79 MM21 cn CLK VDD VDD pch 1=60n UW=2.16 MM23 cp cn VDD VDD pch l=60n UW=2.16 MM71 node1 cn net048 VDD pch l=60n UW=2.75 .ENDS

#### References

- [1] M. Hashimoto, K. Kobayashi, J. Furuta, S.I. Abe, and Y. Watanabe, "Characterizing sram and ff soft error rates with measurement and simulation," Integration, vol.69, pp.161–179, 2019.

- [2] J.C. Pickel, "Effect of cmos miniaturization on cosmic-ray-induced error rate," IEEE Transactions on Nuclear Science, vol.29, no.6, pp.2049–2054, 1982.

- [3] R. Baumann, "The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction," Digest. International Electron Devices Meeting,, pp.329–332, 2002.

- [4] V. Chandra and R. Aitken, "Impact of technology and voltage scaling on the soft error susceptibility in nanoscale cmos," 2008 IEEE International Symposium on Defect and Fault Tolerance of VLSI Systems, pp.114–122, 2008.

- [5] V. Ferlet-Cavrois, L.W. Massengill, and P. Gouker, "Single event transients in digital cmos—a review," IEEE Transactions on Nuclear Science, vol.60, no.3, pp.1767–1790, 2013.

- [6] I. Chatterjee, B. Narasimham, N.N. Mahatme, B.L. Bhuva, R.A. Reed, R.D. Schrimpf, J.K. Wang, N. Vedula, B. Bartz, and C. Monzel, "Impact of technology scaling on sram soft error rates," IEEE Transactions on Nuclear Science, vol.61, no.6, pp.3512–3518, 2014.

- [7] H. Ando, R. Kan, Y. Tosaka, K. Takahisa, and K. Hatanaka, "Validation of hardware error recovery mechanisms for the sparc64 v microprocessor," 2008 IEEE International Conference on Dependable Systems and Networks With FTCS and DCC (DSN), pp.62–69, 2008.

- [8] J. Wilkinson and S. Hareland, "A cautionary tale of soft errors induced by sram packaging materials," IEEE Transactions on Device and Materials Reliability, vol.5, no.3, pp.428–433, 2005.

- [9] D. Mavis and P. Eaton, "Soft error rate mitigation techniques for modern microcircuits," 2002 IEEE International Reliability Physics Symposium. Proceedings. 40th Annual (Cat. No.02CH37320), pp.216– 225, 2002.

- [10] S. Mitra, M. Zhang, S. Waqas, N. Seifert, B. Gill, and K.S. Kim, "Combinational logic soft error correction," 2006 IEEE International Test Conference, pp.1–9, 2006.

- [11] R. Yamamoto, C. Hamanaka, J. Furuta, K. Kobayashi, and H. Onodera, "An area-efficient 65 nm radiation-hard dual-modular flip-flop to avoid multiple cell upsets," IEEE Transactions on Nuclear Science, vol.58, no.6, pp.3053–3059, 2011.

- [12] T. Calin, M. Nicolaidis, and R. Velazco, "Upset hardened memory design for submicron cmos technology," IEEE Transactions on Nuclear Science, vol.43, no.6, pp.2874–2878, 1996.

- [13] F. Mori, M. Ebara, Y. Tsukita, J. Furuta, and K. Kobayashi, "Intrinsic vulnerability to soft errors and a mitigation technique by layout optimization on dice flip flops in a 65-nm bulk process," IEEE Transactions on Nuclear Science, vol.68, no.8, pp.1727–1735, 2021.

- [14] P. Roche, J.L. Autran, G. Gasiot, and D. Munteanu, "Technology downscaling worsening radiation effects in bulk: Soi to the rescue," 2013 IEEE International Electron Devices Meeting, pp.31.1.1– 31.1.4, 2013.

- [15] A. Makihara, T. Yamaguchi, H. Asai, Y. Tsuchiya, Y. Amano, M. Midorikawa, H. Shindou, S. Onoda, T. Hirao, Y. Nakajima, T. Takahashi, K. Ohnishi, and S. Kuboyama, "Optimization for seu/set immunity on 0.15 μm fully depleted cmos/soi digital logic devices," IEEE Transactions on Nuclear Science, vol.53, no.6, pp.3422–3427, 2006.

- [16] K. Yamada, H. Maruoka, J. Furuta, and K. Kobayashi, "Radiation-hardened flip-flops with low-delay overhead using pmos pass-transistors to suppress set pulses in a 65-nm fdsoi process," IEEE Transactions on Nuclear Science, vol.65, no.8, pp.1814–1822, 2018.

- [17] M. Ebara, K. Yamada, K. Kojima, Y. Tsukita, J. Furuta, and K. Kobayashi, "Evaluation of soft-error tolerance by neutrons and heavy ions on flip flops with guard gates in a 65-nm thin box fdsoi process," IEEE Transactions on Nuclear Science, vol.67, no.7, pp.1470–1477, 2020.

- [18] S. Sugitani, R. Nakajima, K. Yoshida, J. Furuta, and K. Kobayashi, "Radiation hardened flip-flops with low area, delay and power overheads in a 65 nm bulk process," 2023 IEEE International Reliability Physics Symposium (IRPS), pp.1–5, 2023.

- [19] K. Yamada, H. Maruoka, J. Furuta, and K. Kobayashi, "Sensitivity to soft errors of nmos and pmos transistors evaluated by latches with stacking structures in a 65 nm fdsoi process," 2018 IEEE International Reliability Physics Symposium (IRPS), pp.P–SE.3–1–P–SE.3–5, 2018.

- [20] P. Shivakumar, M. Kistler, S. Keckler, D. Burger, and L. Alvisi, "Modeling the effect of technology trends on the soft error rate of combinational logic," Proceedings International Conference on Dependable Systems and Networks, pp.389–398, 2002.

- [21] P. Hazucha and C. Svensson, "Impact of cmos technology scaling on the atmospheric neutron soft error rate," IEEE Transactions on Nuclear Science, vol.47, no.6, pp.2586–2594, 2000.

- [22] R. Nakajima, K. Ioki, J. Furuta, and K. Kobayashi, "Radiation hardened flip-flops minimizing area, power, and delay overheads with 1/100 lower  $\alpha$ -ser in a 130 nm bulk process," 2022 IEEE 28th International Symposium on On-Line Testing and Robust System Design (IOLTS), pp.1–5, 2022.

- [23] K. Yamada, H. Maruoka, J. Furuta, and K. Kobayashi, "Radiation-hardened flip-flops with low-delay overhead using pmos pass-transistors to suppress set pulses in a 65-nm fdsoi process," IEEE Transactions on Nuclear Science, vol.65, no.8, pp.1814–1822, 2018.

- [24] J.S. Kauppila, T.D. Loveless, R.C. Quinn, J.A. Maharrey, M.L. Alles, M.W. McCurdy, R.A. Reed, B.L. Bhuva, L.W. Massengill, and K. Lilja, "Utilizing device stacking for area efficient hardened soi flip-flop designs," 2014 IEEE International Reliability Physics Symposium, pp.SE.4.1–SE.4.7, 2014.

- [25] S.A. Khan, S.J. Wen, and S. Baeg, "Assessing alpha-particle-induced seu sensitivity of flip-chip bonded sram using high energy irradiation," IEICE Electronics Express, vol.13, no.17, pp.20160627– 20160627, 2016.

- [26] H. Kobayashi, N. Kawamoto, J. Kase, and K. Shiraish, "Alpha particle and neutron-induced soft error rates and scaling trends in sram," 2009 IEEE International Reliability Physics Symposium, pp.206–211, 2009.

- [27] C.W. Slayman, "Theoretical correlation of broad spectrum neutron sources for accelerated soft error testing," IEEE Transactions on Nuclear Science, vol.57, no.6, pp.3163–3168, 2010.

- [28] "Measurement and reporting of alpha particles and terrestrial cosmic ray-induced soft errors in semiconductor devices: Jesd89a," JEDEC STANDARD, JEDEC Sold State Technology Association, vol.89,

- pp.1-85, 2006.

- [29] T. Uemura, B. Chung, S. Chung, S. Lee, Y. Hwang, and S. Pae, "Impact of design and process on alpha-induced ser in 4 nm bulk-finfet sram," 2023 IEEE International Reliability Physics Symposium (IRPS), pp.1–8, 2023.

- [30] T. Ito, R. Nakajima, J. Furuta, and K. Kobayashi, "Evaluation of soft error tolerance on flip-flops restoring from a single node upset by celements," 2022 IEEE International Meeting for Future of Electron Devices, Kansai (IMFEDK), pp.1–2, 2022.

- [31] P. Dodd, A. Shaneyfelt, K. Horn, D. Walsh, G. Hash, T. Hill, B. Draper, J. Schwank, F. Sexton, and P. Winokur, "Seu-sensitive volumes in bulk and soi srams from first-principles calculations and experiments," IEEE Transactions on Nuclear Science, vol.48, no.6, pp.1893–1903, 2001.

Shotaro Sugitani was born in Kyoto, Japan in 1998. He received the B.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2022. He is currently a master course student at Kyoto Institute of Technology. He is a student member of IEEE, IPSJ and IEICE.

Ryuichi Nakajima was born in Hiroshima, Japan in 1997. He received the B.E. and the M.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2021 and 2023, respectively. He is currently a doctoral course student at Kyoto Institute of Technology. He is a student member of IEEE, IPSJ and IEICE.

**Keita Yoshida** was born in Osaka, Japan in 2000. He received the B.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2023. He is currently a master course student at Kyoto Institute of Technology. He is a student member of IEEE and IEICE.

**Jun Furuta** was born in Gifu, Japan, in 1986. He received the B.E., M.E. and Ph.D. degrees in electrical and electronic engineering in informatics from Kyoto University, Kyoto, Japan, in 2009, 2011, and 2014, respectively. In 2014, he joined the Kyoto Institute of Technology as a specially appointed Assistant Professor, where he was then promoted to an Assistant Professor in 2017.

Kazutoshi Kobayashi received his B.E., M.E. and Ph. D. in Electronic Engineering from Kyoto University, Japan in 1991, 1993, 1999, respectively. Starting as an Assistant Professor in 1993, he was promoted to an Associate Professor in the Graduate School of Informatics, Kyoto University in 2001, and stayed in that position until 2009. For two years during this time, he acted as an Associate Professor of VLSI Design and Education Center (VDEC) at the University of Tokyo. Since 2009, he has been a Professor

at Kyoto Institute of Technology. While in the past he focused on reconfigurable architectures utilizing device variations, his current research interest is in improving the reliability (Soft Errors, Bias Temperature Instability and Plasma Induced Damage) of current and future VLSIs. He started a research project related to gate drivers for GaN and SiC transistors since 2013. In 2022, he was nominated for one of the project managers of Moonshot Goal 6 "Realization of a fault-tolerant universal quantum computer that will revolutionize economy, industry, and security by 2050" and organized his project team named "Development of Scalable Highly Integrated Quantum Bit Error Correction System" abbreviated as QUBECS. He was the recipient of the IEICE best paper award in 2009, the IRPS best poster award in 2013, the ICICDT best paper award in 2019 and the IEICE Electronics Society award in 2021.