INVITED PAPER Special Section on Analog Circuits and Their Applications

# An Energy Efficient 2-Read/Write 8T Dual-Port SRAM with Disturbance Aware Self-Adjustable Replica Tracking Circuit

Koji NII<sup>†a)</sup>, Member and Kazutoshi KOBAYASHI<sup>†</sup>, Senior Member

SUMMARY An energy-efficient 2-read/write (2RW) dual-port (DP) SRAM with a new disturbance aware replica scheme has been demonstrated. This scheme aims to generate internal critical timing signals for sense-enable (SE) triggers and wordline (WL) negating paths during the readout operation. By placing individual replica circuits for each port, appropriate internal delays are generated self-adjustably, whether accessing same-row or different-row. Even when the two clock inputs have different phases and frequencies, the proposed replica circuit effectively generates internal timings by minicking the discharge speeds of each bitline (BL) using replica 8T DP bitcells. A prototype of a 256-kbit DP SRAM macro has been implemented in 90 nm logic CMOS technology. Measurement results show that the dynamic power consumption in the cell array is reduced by 16.6% compared to the conventional replica scheme at a typical supply voltage of 1.2 V and room temperature.

**key words:** dual-port SRAM, low power consumption, tracking, replica circuit, dummy memory cell, optimization of sense enable signal

#### 1. Introduction

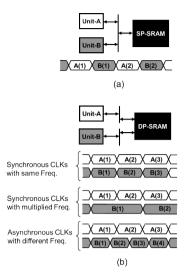

Embedded SRAMs have become increasingly key components in advanced CMOS logic technologies for high-performance and energy efficient computing systems. There are several types of SRAMs as shown in Fig. 1. High-density or high-speed single-port (SP) SRAMs are frequently used in the system-on-chip (SoC) as cache memory operations. Usually the push-ruled dense 6T SRAM bitcells support requirements of total memory capacity increase [1]–[22].

Besides multi-port SRAMs, which can improve memory access throughputs, are also significantly demanded for achieving multi-processing operations in the imaging, graphics, AI and ML applications. In such parallel computing systems, 1-read/1-write (1R1W) 2-port (2P) SRAMs are one of the solutions to meet the requirements of both high-performance and energy efficient [23]–[30]. An 8T-2P bitcell is adopted, being consist of eight transistors including decoupled 2 NMOSs for read port.

In multi-CPUs and many-core architectures [31]–[34], 2-read/write (2RW) dual-port (DP) SRAMs with 8T-DP bitcell are also used as data caches or shared cache memories [35]–[51]. The 2RW DP-SRAM allows simultaneous access for both reading and writing operations from two different ports. This design enables two independent data paths, making it ideal for applications that require high-speed data

Manuscript received December 20, 2024.

Manuscript revised April 14, 2025.

Manuscript publicized June 12, 2025.

<sup>†</sup>Kyoto Institute of Technology, Kyoto-shi, 606–8585 Japan.

a) E-mail: koji.nii@vlsi.es.kit.ac.jp DOI: 10.1587/transele.2024CTI0003

| # Clock          | 1          | 1 (common)             |                       | 1 (common) or 2 (individual) |                    |

|------------------|------------|------------------------|-----------------------|------------------------------|--------------------|

| # Port           | 1          | 2                      | 2                     | 2                            | 2                  |

| Port config.     | SP         | pseudo<br>2P<br>(1R1W) | pseudo<br>DP<br>(2RW) | 2P<br>(1R1W)                 | DP<br>(2RW)        |

|                  | 6T-SP      |                        |                       | 8T-2P                        | 8T-DP              |

| Bitcell          | WL —       |                        |                       | WWL RBL RBL                  | BLA T /BLA BLB WLB |

| Disturbance free | Yes        |                        |                       | No                           | No                 |

| Bit density      | High       |                        |                       | Middle                       | Low                |

| Throughput       | Low/Middle |                        | lle                   | High                         | High               |

Fig. 1 Several types of embedded SRAMs which are single-port (SP), 1-read/1-write (1R1W) 2-port (2P) and 2-read/write (2RW) dual-port (DP).

processing and efficient multitasking. DP SRAMs also function as block RAMs in FPGAs [52] or buffer memories for reconfigurable processors [53], [54].

As listed in Fig. 1, there is capability to support 1R1W 2P-SRAM or 2RW DP SRAM by using 6T-SP bitcell with double pumping operation [56]–[61]. These pseudo macros are able to achieve high-density than 8T-2P or 8T-DP solutions, but there are some challenges to improve the maximum operating frequency ( $F_{\rm max}$ ) because the operations are sequentially executed twice within 1 clock cycle period. In addition, it is infeasible that more flexible access with independent clock domain for each port, which is required by reconfigurable systems, FPGAs and network processors for the data buffering.

Figure 2 shows the simple system diagrams and operating timing charts in the case of SP SRAM and true 2RW DP SRAM with 8T-DP bitcell [37]. For 2RW DP SRAM, each port can operate independently, meaning one can read/write data between Unit-A while the other read/write data through Unit-B at the same time even when the two clock inputs have different phases or frequencies.

However, the 2RW DP SRAM with 8T-DP bitcell has inherent disturbances when both ports access simultaneously. There are several reports to solve the disturbances by preventing the access conflict [35], [47]. However, those are limited to use a common clock input, meaning a synchronous clock with same or multiplied frequency for both ports. For supporting individual clock input for each port, meaning asynchronous clock inputs, test screening method or improving operating margins by considering disturbances have been reported [36], [37], [41].

**Fig. 2** Memory access diagrams and timing charts: (a) sequential memory access of SP SRAM, (b) parallel memory access of 2RW DP SRAM [37].

Besides, several works have been undertaken for reducing the standby power of 2RW DP SRAM [37], [42], [45], but few studies have particularly addressed dynamic power reduction of 2RW DP SRAMs [47], [50]. To achieve an energy-efficient parallel computing system, dynamic power reduction of 2RW DP SRAM is important along with leakage power reduction. The disturbance aware power reduction scheme for 2RW DP-SRAM with 8T-DP bitcell has been also reported [47] but it is limited for common clock input. In this work, we propose a disturbance aware self-adjustable tracking circuit to improve the energy-efficiency for 2RW 8T DP SRAM macros allowing asynchronous individual clock inputs.

This paper is organized as follows. In Sect. 2, the function of 2RW DP SRAM and its inherent disturbances are described. Then, the motivation of dynamic power reduction is raised. To improve the energy-efficiency, proposed disturbance aware new tracking circuit is presented in Sect. 3. The test chip fabricated in 90 nm CMOS technology and silicon measured data are discussed in Sect. 4, followed by summarizing in Sect. 5.

#### 2. Disturbance in 2RW DP SRAM

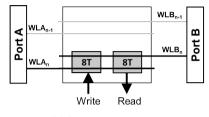

# 2.1 2-Read/Write (2RW) DP SRAM Macro

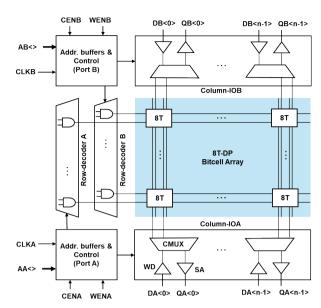

A 2-read/write dual-port SRAM is a type of memory that allows simultaneous access for both reading and writing operations from two different ports. This design enables two independent data paths, making it ideal for applications that require high-speed data processing and efficient multitasking. Figure 3 depicts a simple block diagram of 2RW DP SRAM macro. There are address buffer and control, row decoder, column-IO block for each port and an 8T-DP bitcell array. Each column-IO block has sense-amplifier (SA) and write-driver (WD) with column multiplexor (CMUX)

Fig. 3 Block diagram of 2RW DP SRAM macro with individual clock inputs and 8T-DP bitcell array.

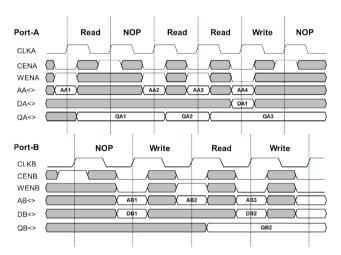

Fig. 4 Timing chart of 2RW DP SRAM macro with asynchronous individual clock input for each port.

for each data bit  $(0, 1, 2, \ldots, n-1)$ . The AA (AB) and DA/QA (DB/QB), respectively denote address inputs and data inputs/outputs for port A (port B). The CENA (CENB) and WENA (WENB) respectively stand for chip enable and write enable signals. The CLKA (CLKB) stands for the individual clock input for port A (B).

The timing chart is presented in Fig. 4. Both ports are allowed to operate individually with different clock phase and frequency. The reading and writing functions for port A are triggered by rising CLKA edge while those operations for port B are triggered by CLKB. The control signals of the chip enable and write enable are independent for each port. If the CENA (CENB) is "1", the port works as no operation (NOP). If the CENA (CENB) is "0" and the WENA (WENB) is "1", the port works as read operation, otherwise it works as write operation when the WENA (WENB) is "0". Each

(a) Different row access mode

(b) Same row access mode

Fig. 5 Two kinds of access modes of DP SRAM: (a) diff.-row access, (b) same-row access [37].

port has its own address inputs, data inputs/outputs, enabling to operate NOP, read or write operation independently.

#### 2.2 Disturbance in 2RW DP SRAM

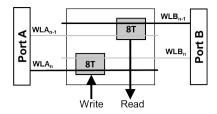

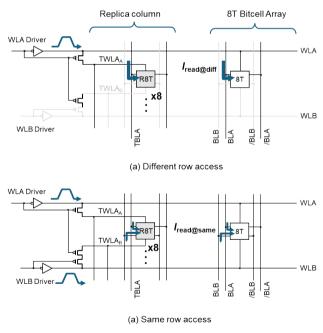

The memory accesses for 2RW 8T DP-SRAM are mainly classified to modes: one is a different-row (diff.-row) access, the other is a same-row access as illustrated in Fig. 5 [37]. When the same-row access, both WLA and WLB to be accessed 8T-DP bitcell are activated simultaneously, then the disturbance happens. There are two kind of disturbance modes: read-disturbance and write-disturbance. The read-disturbance happens in the read operation at port-A (B) from another port-B (A) when the same-row is selected. The write-disturbance similarly happens in the write operation in port-A (B) from another port-B (A) when the same-row is selected. Note that the access from another port is either read or write operation for both disturbance modes [47].

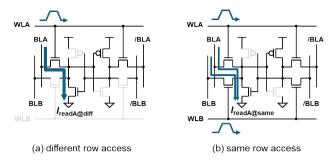

In this work, we focus on the dynamic read power reduction by self-adjustable tracking circuit which is aware of the read disturbance in 2RW 8T DP SRAM. Figure 6 presents the read disturbance at the same-row address access when both WLA and WLB are activated. In the diff.-row access, the read operation is executed as a single-port 6T SRAM because either WLA or WLB is only activated. Then any disturbance from the other port never happens. In the same-row access, the cell current flows into the pull-down (PD) NMOS from both BLA and BLB in the accessed bitcell. In that case, the read current ( $I_{\rm read}$ ) of the target BLA through the pass-gate (PG) and PD NMOSs decreases by additional cell current from another BLB. As a result, the discharge speed of BLA decreases.

The read current ( $I_{\text{read}}$ ) on BLA at diff.-row access mode ( $I_{\text{readA@diff}}$ ) is delivered analytically by Eq.(1) reported by [47]. The read current at same-row access mode ( $I_{\text{readA@same}}$ ) is delivered by Eq.(2) as well.

**Fig. 6** Read access modes in 8T-DP bitcell: (a) diff.-row access, (b) same-row access.

**Fig. 7** Monte Carlo simulation results of read currents for 2RW 8T-DP bitcell at diff.-row access and same-row access.

$$I_{\text{readA@diff}} = \frac{1}{2}\beta_{\text{G}} \left( 1 - \frac{1}{1 + \frac{\beta_{\text{D}}}{\beta_{\text{G}}}} \right) (V_{\text{DD}} - V_{\text{tn}})^2$$

(1)

$$I_{\text{readA@same}} = \frac{1}{2} \beta_{\text{G}} \left( 1 - \frac{1}{1 + 2 \frac{\beta_{\text{D}}}{\beta_{\text{G}}}} \right) (V_{\text{DD}} - V_{\text{tn}})^2$$

(2)

Here, each  $\beta_G$  and  $\beta_D$  is the gain factor of PG NMOS and PD NMOS respectively, and  $V_{tn}$  is assumed as the same threshold voltage of PG and PD NMOSs. By the Eqs. (1) and (2), the following Eq. (3) is concluded.

$$I_{\text{readA@diff}} > I_{\text{readA@same}}$$

(3)

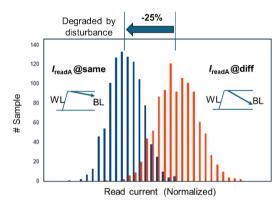

Using 90 nm CMOS technology, the Monte Carlo simulation for the 2RW 8T-DP bitcell is carried out with 1000 iterations to deliver the distributions of  $I_{\rm readA@diff}$  and  $I_{\rm readA@same}$  with considering random variations. Figure 7 shows the histogram of  $I_{\rm readA@diff}$  and  $I_{\rm readA@same}$  distributions respectively at process-TT, 1.2 V typical supply voltage and 25°C conditions. It is obtained that the difference of mean values of read currents between both access modes is around 25%. The degradation of  $I_{\rm readA@same}$  is due to the disturbance at same-row access.

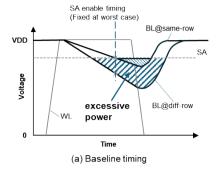

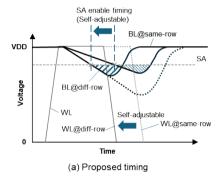

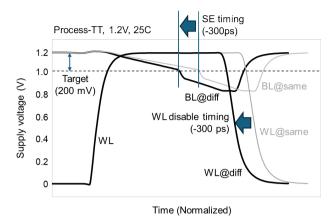

Figure 8 shows the concept waveforms of read power reduction by self-adjustable tracking. As delivered in Eq. (3),  $I_{\text{readA@same}}$  is smaller than  $I_{\text{readA@diff}}$ , BL swing speed at diff.-row access is faster than that of same-row access. If SE timing and WL disable timing are fixed to the worst condition, these timing have excessive margins at the diff.-row

**Fig. 8** Basic concept of read power reduction by self-adjustable tracking: (a) baseline timing, (b) proposed timing.

access. In that case, unexpected excessive BL discharging power is consumed as shown in Fig. 8 (a). If the SE timing and WL disable timing can be controlled by detecting whether diff-row or same-row is accessed, the excessive discharging power can be reduced at the diff-row access mode as shown in Fig. 8 (b). By introducing new replica tracking scheme, the disturbance can be detected automatically and the optimum internal critical timing for SE and WL disable are generated self-adjustably. In the next Section, proposed replica tracking circuit is explained in detail.

## 3. Disturbance Aware Self-Adjustable Tracking Circuit

## 3.1 Tracking Scheme Using Replica Bitcell

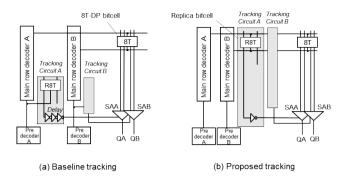

Figure 9(a) shows a baseline tracking scheme for readout operation of 2RW DP SRAM with 8T-DP bitcell (8T) array using a replica 8T-DP bitcell (R8T). It is simply extended to 2RW 8T DP SRAM design from 6T-SP SRAM designs [62], [63]. The port A (B) has own tracking circuit A (B) without any relationship between both ports. As discussed in Sect. 2, the read current at same-row access is smaller than that of diff.-row access due to the disturbance. However, there is no way to detect whether the accesses from both ports are in the same-row or not. As a result, the sense enable (SE) timing that activates each sense amplifier (SAA/SAB) should be designed as the worst condition under the same-row access even though the diff.-row access can pull-in the SE timing. In addition, the input of baseline tracking circuit is triggered by the pre-decode signal as shown in Fig. 9 (a). In this case, there is undesirable timing mismatch between the main WL

**Fig. 9** Tracking scheme for 2RW DP SRAM with 8T-DP bitcell (8T) array using a replica 8T-DP bitcell (R8T).

and tracking circuit activation timings. Then the buffer chain is required in the tracking output signal (equal to SE timing) to match the delay of the main row decoder.

The delay of buffer chain implemented by logic inverters induces the timing mismatch over the process-volage-temperature (PVT) variations because the MOS characteristics are different between logic CMOSs and pull-up (PU)/PD/PG transistors of the 8T-DP bitcell. It is important to match the 8T-DP bitcell characteristics for generating the critical internal timing. That is why the tracking replica circuits are utilized in resent SRAM designs.

Figure 9 (b) shows the concept of proposed tracking circuit for 2RW DP SRAM. The input of tracking circuit is the same timing of the WL activation. It uses the same replica R8T bitcells but enables to track whether the accesses from both ports are in the same-row or not. In addition, there is no undesirable timing mismatch between the main WL and tracking circuit activation timings. The additional buffer chain is not required.

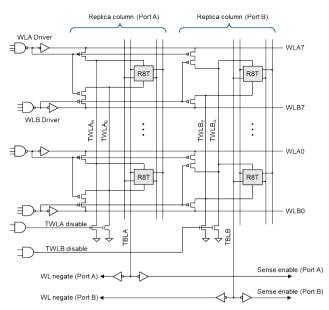

Figure 10 shows the schematic of the proposed selfadjustable disturbance aware tracking circuit [64]. There are two replica columns which are same layout structures of 8T-DP bitcells. One is tracking for port A and another is tracking for port B. Eight replica R8T bitcells in each column are connected to own tracking wordline (TWLA, TWLB). In each column, two BL pairs run vertical, but only one of the BL (TBLA, TBLB) is used to generate the SE signal. The bitcell structure of replica R8T bitcell is same as that of the 8T bitcell, so that the interconnect capacitance and resistance are identical. To discharge the TBLA (TBLB) every time, however, the data in the replica R8T bitcell is fixed to "L" by modifying slight metal/via layout changes. TBLA (TBLB) reflects the discharge speed of the BLA (BLB) voltage. It makes use of both WLA and WLB pulses in the selected row to generate the SE signal. This indicates that all replica R8T bitcells in replica column are utilized to generate the SE signal. On the other hand, the baseline scheme as shown in Fig. 9(a) made use of only some localized replica R8T bitcells with dummy 8T (D8T) bitcells (not shown in the figure) in the replica column.

Two tracking-WLs (TWLA<sub>A</sub>, TWLA<sub>B</sub>) are controlled by selected WLA and WLB through 1-stacked and 2-stacked PMOS transiters. TWLA<sub>A</sub>, TWLA<sub>B</sub> are expected to mimic

Fig. 10 Proposed self-adjustable disturbance aware tracking circuit.

the same-row access or diff.-row access in the replica column. To generate the optimum timing, the timing delay of TBL should be faster than that of BL in the 8T bitcell array. To enable it, the multiple replica R8T bitcells are activated in parallel. The multiple R8T bitcells also help to reduce the impact of local-Vt variation. Estimated optimum number of multiplications is in the range of 8–16 for  $512 \times 512$  array in 90nm CMOS technology. Then the TWL is commonly connected to eight replica R8T bitcells arranged in the same column direction in our design discussed here after. Of course, the different number can be applied for the proposed tracking circuit if needed.

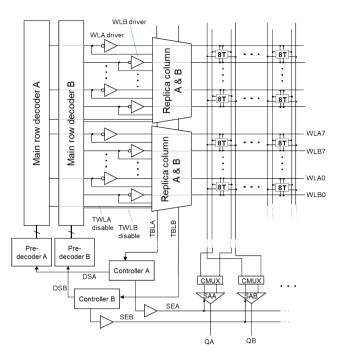

Figure 11 shows the block diagram of proposed tracking scheme [64]. The replica column for port A and port B are composed every 8 rows between 8T bitcell array and main row decoders with WL drivers. The main row decoder A (B) activates the WLA (WLB) corresponding to the input row address, then the data stored in the accessed 8T bitcell is transferred through the BLA pair (BLB pair). On the same time, a signal from the activated 8 replica bitcells (R8Ts) in the replica column is transferred through the tracking BL labeled as TBLA (TBLB) in Fig. 10. The signal is fed to the Controller A (B) to generate the SEA (SEB) signal for sense amplifier SAA (SAB) and DSA (DSB) signal for WLA (WLB) inactivation. The differential voltage of BLA pair (BLB pair) is latched by SAA (SAB) adequately through column multiplexer (CMUX) and then data is readout to QA (QB). Note that the TBLA and TBLB run vertically and connected to all R8Ts in the replica column. The TWLA (TWLB) disenable signal is to inactivate the tacking WL when the replica column block is not selected or after readout operation done.

Fig. 11 Block diagram of proposed disturbance aware self-adjustable tracking scheme for 2RW DP SRAM macro [64].

**Fig. 12** Self-adjustable tracking operation for port A: (a) diff.-row access mode, (b) same-row access mode.

## 3.2 Functionality of Proposed Tracking Circuit

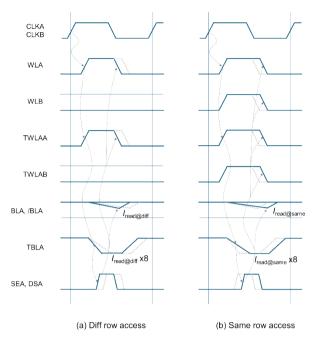

Figure 12 represents the self-adjustable tracking operation for port A at the diff./same-row access modes. In the diff.row access, WLA and TWLA<sub>A</sub> are activated at the same timing by turning on the 1-stacked PMOS. The WLB in the same-row is inactivated (selected the other diff.-row),

Fig. 13 Timing waveforms of proposed self-adjustable tracking circuit.

TWLA<sub>B</sub> is also inactivated because one of the 2-stacked PMOS is still turning off. Then  $8x\ I_{\rm readA@diff}$  flows in the TBLA because the eight R-8Ts are connected to TWLA<sub>A</sub> commonly in the replica column A. Consequently, the discharging speed of TBLA is 8x faster than that of each BLA, making an appropriate SEA timing and DSA timing for WLA inactivation under the diff.-row access mode. In the samerow access, WLA and TWLA<sub>B</sub> are activated almost same timing and WLB and TWLA<sub>B</sub> are similarly activated same timing. As a result,  $8x\ I_{\rm readA@same}$  flows through the TBLA as the same-row access mode. The timing waveforms are shown in Fig. 13. The port A tracking operation is described here, the equivalent tracking operation for port B is executed by the other replica column B.

# 3.3 SPICE Simulation Result

Figure 14 shows the SPICE simulation waveforms of the BLs and WLs at diff./same-row access modes. Different timings of SE signals are generated in accordance with the discharge speed of the BLs. Here the target differential voltage of SA is set to 200 mV at 1.2 V and 25°C. The simulation result show that the WL pulse width at diff.-row access is shorter than that of same-row access. This indicates that SE timing is self-adjustably generated by the tracking circuit. If the timing is not aware the row access mode, the excessive BL swing appears due to the same timing at worst condition which is equal to same-row-access mode. By proposed disturbance aware self-adjustable tracking circuit, it can be cut off by pulling-in the WL inactivating timing. Therefore, dynamic power in read operation at diff.-row access mode is effectively reduced.

The proposed tracking circuit is effective for individ-

Fig. 14 SPICE simulation waveform for read operation.

Fig. 15 SPICE simulation result of the read current variation depending on CLKA and CLKB input phases.

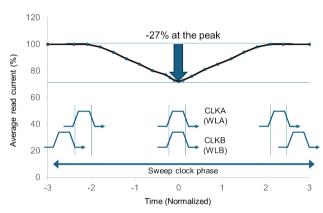

ual clock inputs with different phase or frequency. Figure 15 shows the SPICE simulation result of the average read current variation by sweeping the CLKA and CLKB input phases. Both read currents flowing BLA in the cell array and TBLA in the replica column are varied with the same percentages along with the overlap period of both WLA and WLB activations. The simulation result shows the average read currents in both 8TDP bitcell and replica R8T bitcells degrade by 27% at the peak when the WLA and WLB are exactly activated simultaneously. By pulling-in the WL inactivation timing with the proposed self-adjustable circuit, the excessive read dynamic power can be reduced as discussed in Sect. 2.

## 4. Test-chip Design and Fabrication

# 4.1 Implementation of 2RW DP SRAM Macro

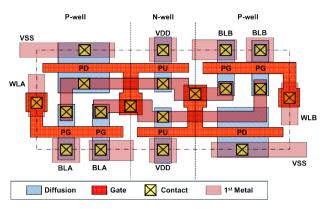

We designed and fabricated a test chip using 90 nm CMOS technology with 5-Cu metals. Figure 16 illustrate the layout of the logic-ruled 8T-DP bitcell up to the first metal layer. The cell size is 2.94 um<sup>2</sup> with balanced symmetrical layout. It is 1.44x larger than the dense push-ruled 8T-DP bitcell and 2.35x larger than the dense push-ruled 6T-SP bitcell [50]. The BLs run vertically in the 2<sup>nd</sup> metal layer while WLs run horizontally with 3<sup>rd</sup> metal layer. The BL

Fig. 16 Layout plot of logic-rule based 8T-DP bitcell.

Fig. 17 Photograph of the implemented 256-kbit DP SRAM macro.

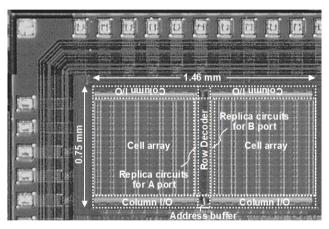

Table 1Test chip features.

| Technology       | 90-nm logic CMOS               |  |  |

|------------------|--------------------------------|--|--|

| SRAM type        | 2-Read/Write 8T Dual-port SRAM |  |  |

| Bitcell size     | 2.58 um x 1.14 um (2.94 um²)   |  |  |

| Bit-word config. | 16-bit x 16-kword              |  |  |

| Array size       | 512-row x 512-column           |  |  |

| Column MUX       | 32                             |  |  |

| Macro capacity   | 256-kbit                       |  |  |

| Macro size       | 1.46 x 0.75 mm <sup>2</sup>    |  |  |

| Density          | 234-kbit/mm <sup>2</sup>       |  |  |

coupling noise between each port is isolated by VDD shield in the center location. Figure 17 portrays a photograph of the implemented 256-kbit DP SRAM macro. 512-row by 512-column size is divided into two cell arrays by center placed row decoders. Note that the proposed tracking circuits are physically placed on both sides next to the center row decoders. The area overhead of the tracking circuits is less than 2% of the macro. Table 1 summarizes the features of implemented 256-kbit 2RW DP SRAM macros in 90-nm CMOS logic technology.

### 4.2 Silicon Measurements

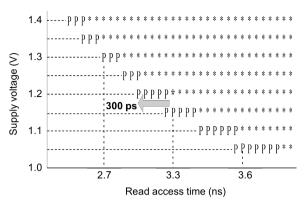

Figure 18 shows the measured typical shmoo plot of read access time over supply voltage at 25°C. The area marked

Fig. 18 Measured shmoo plot for read access time vs supply voltage at room temperature.

Fig. 19  $\,$  Relationship between access time and dynamic read power in the  $512\times512$  cell array.

with (\*) shows passes at both same-row access and diff.-row access. The area marked with (p) shows the additional passes at diff.-row access mode. The read access time of diff.-row access is 300 ps faster than that of same-row access. This result shows that the proposed tracking circuit can self-adjustably generate the appropriate SE and WL negating timings being aware of the diff./same-row access modes.

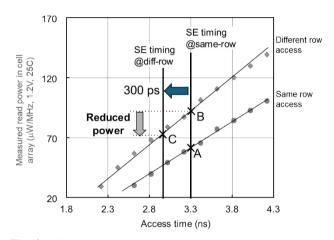

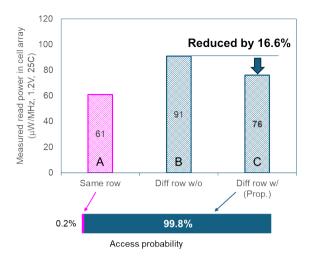

In the prototype macro design, the SE signal can be arbitrarily controlled by an external test signal under the testing mode. We measured dynamic read power consumption by sweeping the SE timing. Figure 19 shows the relationship between the read access time and the power consumption of the BL discharge. The horizontal axis represents the read access time, which is equivalent to that in Fig. 18. The vertical axis represents the dynamic power consumption of the BL discharge. Considering that the BL discharge decreases linearly, the power dissipation increases linearly as the SE timing increases. Point A represents the power consumed in the same-row access. Point B indicates the power dissipation in diff.-row access if the baseline tracking scheme is applied. The faster SE signal is obtained for the diff.-row access, so that the power consumed in our scheme is represented by C. By comparing C with B, we achieved a 16.6% power

Fig. 20 Measured dynamic read power in the  $512 \times 512$  cell array.

reduction in the BL discharge.

The read dynamic power comparison is summarized in Fig. 20. If the row address is accessed randomly, the probability of occurrence of the same-row access is 1/row. It is only 0.2% in the 512-row array. Although a small probability of the same-row access exists, the same-row access should be regarded as a worst condition for maintaining the design margin. By introducing proposed tracking circuit, 99.8% read operation can be reduced excessive read power consumption by 16.6% with keeping the worst same-row access timing margin.

## 5. Conclusions

A disturbance aware self-adjustable replica tracing circuit is proposed for the embedded 2RW dual-port SRAM. It is to generate internal critical timings by each replica circuit which generates appropriate internal delays self-adjustably in accordance with the same-row or different-row accesses. The proposed replica circuit effectively generates the internal timings by being mimic each BL discharge speed with replica 8T DP bitcells. As a result, it is applicable even if the two clock inputs for port-A and port-B are different phases and frequencies individually. A prototype 256-kbit DP SRAM macro is implemented in 90 nm logic CMOS technology. The measurement silicon data shows that the dynamic read power consumption in the cell-array is reduced by 16.6% compared to the conventional baseline tracking scheme at 1.2 V typical supply voltage and 25°C.

#### References

- [1] M. Yabuuchi, M. Morimoto, Y. Tsukamoto, S. Tanaka, K. Tanaka, M. Tanaka, and K. Nii, "16 nm FinFET High-k/Metal-gate 256-kbit 6T SRAM macros with wordline overdriven assist," IEEE Int. Electron Devices Meeting (IEDM), pp.3.3.1–3.3.3, Dec. 2014.

- [2] Y.-H. Chen, W.-M. Chan, W.-C. Wu, H.-J. Liao, K.-H. Pan, J.-J. Liaw, T.-H. Chung, Q. Li, C.-Y. Lin, M.-C. Chiang, S.-Y. Wu, and J. Chang, "A 16 nm 128 Mb SRAM in High- κ Metal-Gate FinFET Technology with Write-Assist Circuitry for Low-VMIN Applications," IEEE J. of Solid-State Circuits, vol.50, pp.170–177, 2015.

- [3] E. Karl, Z. Guo, J.W. Conary, J.L. Miller, Y.-G. Ng, S. Nalam, D. Kim, J. Keane, U. Bhattacharya, and K. Zhang, "17.1 A 0.6V 1.5GHz 84Mb SRAM design in 14nm FinFET CMOS technology," IEEE ISSCC Dig. Tech. Papers, pp.1–3, Feb. 2015.

- [4] T. Song, W. Rim, S. Park, Y. Kim, J. Jung, G. Yang, S. Baek, J. Choi, B. Kwon, Y. Lee, S. Kim, G. Kim, H.-S. Won, J.-H. Ku, S.S. Paak, E.S. Jung, S.S. Park, and K. Kim, "17.1 10nm FinFET 128Mb SRAM with assist adjustment system for power, performance, and area optimization," IEEE ISSCC Dig. Tech. Papers, pp.306–307, Feb. 2016.

- [5] J. Chang, Y.-H. Chen, W.-M. Chan, S.P. Singh, H. Cheng, H. Fujiwara, J.-Y. Lin, K.-C. Lin, J. Hung, R. Lee, H.-J. Liao, J.-J. Liaw, Q. Li, C.-Y. Lin, M.-C. Chiang, and S.-Y. Wu, "12.1 A 7nm 256Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-VMIN applications," IEEE ISSCC Dig. Tech. Papers, pp.206–207, Feb. 2017.

- [6] M. Clinton, H. Cheng, H.J. Liao, R. Lee, C.-W. Wu, J. Yang, H.-T. Hsieh, F. Wu, J.-P. Yang, A. Katoch, A. Achyuthan, D. Mikan, B. Sheffield, and J. Chang, "12.3 A low-power and high-performance 10nm SRAM architecture for mobile applications," IEEE ISSCC Dig. Tech. Papers, pp.210–211, Feb. 2017.

- [7] Z. Guo, D. Kim, S. Nalam, J. Wiedemer, X. Wang, and E. Karl, "A 23.6Mb/mm<sup>2</sup> SRAM in 10nm FinFET Technology with Pulsed PMOS TVC and Stepped-WL for Low-Voltage Application," IEEE ISSCC Dig. Tech. Papers, pp.196–198, Feb. 2017.

- [8] T. Song, et al., "12.2 A 7nm FinFET SRAM macro using EUV lithography for peripheral repair analysis," IEEE ISSCC Dig. Tech. Papers, pp.208–209, Feb. 2017.

- [9] M. Clinton, R. Singh, M. Tsai, S. Zhang, B. Sheffield, and J. Chang, "A 5GHz 7nm L1 cache memory compiler for high-speed computing and mobile applications," IEEE ISSCC Dig. Tech. Papers, pp.200– 201, Feb. 2018.

- [10] T. Song, J. Jung, W. Rim, H. Kim, Y. Kim, C. Park, J. Do, S. Park, S. Cho, H. Jung, B. Kwon, H.-S. Choi, J.S. Choi, and J.S. Yoon, "A 7nm FinFET SRAM using EUV lithography with dual write-driver-assist circuitry for low-voltage applications," IEEE ISSCC Dig. Tech. Papers, pp.198–200, Feb. 2018.

- [11] Y. Yokoyama, M. Tanaka, K. Tanaka, M. Morimoto, M. Yabuuchi, Y. Ishii, and S. Tanaka, "A 29.2 Mb/mm<sup>2</sup> Ultra High Density SRAM Macro using 7nm FinFET Technology with Dual-Edge Driven Wordline/Bitline and Write/Read-Assist Circuit," VLSI Cir. Symp. Dig., pp.1–2, June 2020.

- [12] T.-Y.J. Chang, Y.-H. Chen, W.-M. Chan, H. Cheng, P.-S. Wang, Y. Lin, H. Fujiwara, R. Lee, H.-J. Liao, P.-W. Wang, G. Yeap, and Q. Li, "A 5-nm 135-Mb SRAM in EUV and High-Mobility Channel FinFET Technology With Metal Coupling and Charge-Sharing Write-Assist Circuitry Schemes for High-Density and Low-V<sub>MIN</sub> Applications," IEEE J. of Solid-State Circuits, vol.56, no.1, pp.179–187, 2020.

- [13] S. Baeck, I. Lee, H. Tang, D. Seo, J. Choi, T. Song, and J. Kye, "5nm Low Power SRAM Featuring Dual-Rail Architecture with Voltage-Tracking Assist Circuit for 5G mobile application," VLSI Cir. Symp. Dig., pp.1–2, June 2021.

- [14] T. Song, W. Rim, H. Kim, K.H. Cho, T. Kim, T.J. Lee, G. Bae, D.-W. Kim, S.D. Kwon, S. Baek, J. Jung, J. Kye, H. Jung, H. Kim, S.-M. Jung, and J. Park, "24.3 A 3nm Gate-All-Around SRAM Featuring an Adaptive Dual-BL and an Adaptive Cell-Power Assist Circuit," IEEE ISSCC Dig. Tech. Papers, pp.338–340, Feb. 2022.

- [15] I. Lee, D. Seo, Y. Li, M. Kim, and S. Baeck, "4nm Voltage Auto-Tracking SRAM Pulse Generator with Fully RC Optimized Row Auto-Tracking Write Assist Circuits," VLSI Cir. Symp. Dig., pp.218–219. June 2022.

- [16] J. Chang, Y.-H. Chen, G. Chan, K.-C. Lin, P.-S. Wang, Y. Lin, S. Chen, P. Lin, C.-W. Wu, C.-Y. Lin, Y.-H. Nien, H. Fujiwara, A. Katoch, R. Lee, H.-J. Liao, J.-J. Liaw, S.-Y.M. Wu, and Q. Li, "A 3nm 256Mb SRAM in FinFET Technology with New Array Banking Architecture and Write-Assist Circuitry Scheme for High-Density

- and Low-VMIN Applications," VLSI Cir. Symp. Dig., pp.1–2, June 2023

- [17] Y. Osada, T. Nakazato, K. Nii, J.-J. Liaw, S.-Y.M. Wu, Q. Li, H. Fujiwara, H.-J. Liao, and T.-Y.J. Chang, "3.7-GHz Multi-Bank High-Current Single-Port Cache SRAM with 0.5V-1.4V Wide Voltage Range Operation in 3nm FinFET for HPC Applications," VLSI Cir. Symp. Dig., pp.1–2, June 2023.

- [18] Y. Aoyagi, M. Yabuuchi, T. Tanaka, Y. Ishii, Y. Osada, T. Nakazato, K. Nii, I. Wang, Y.-H. Hsu, H.-C. Cheng, H.-J. Liao, and T.-Y.J. Chang, "A 3-nm 27.6-Mbit/mm2 Self-timed SRAM Enabling 0.48 1.2V Wide Operating Range with Far-end Pre-charge and Weak-Bit Tracking," VLSI Cir. Symp. Dig., pp.1–2, June 2023.

- [19] N. Jungmann, R. Joshi, E. Kachir, K. Shimanovich, B. He, T. Cohen, T. Miller, D. Leu, D. Kannambadi, I. Wagner, K. Reyer, H. Konen, M. Suleiman, V. Sindhe, and Y. Freiman, "A 1.9GHz 0.57V Vmin 576Kb embedded product-ready L2 cache in 5nm FinFET technology," VLSI Cir. Symp. Dig., pp.1–2, June 2023.

- [20] T.-Y.J. Chang, Y.-H. Chen, K.V. Reddy, N. Puri, T. Masina, K.-C. Lin, P.-S. Wang, Y. Lin, C.-Y. Lin, Y.-H. Nien, H. Fujiwara, K.-F. Lin, M.-H. Chang, C.W. Wu, R. Lee, Y. Wang, H.-J. Liao, Q. Li, P.W. Wang, and G. Yeap, "A 38.1Mb/mm<sup>2</sup> SRAM in a 2nm-CMOS-Nanosheet Technology for High-Density and Energy-Efficient Compute," IEEE ISSCC Dig. Tech. Papers, pp.492–494, Feb. 2025.

- [21] H. Pilo, J. Barth, K.D. Dwivedi, P. Lee, V. Kumar, P. Nalawar, Y. Patel, S. Sharad, and S. Singh, "A 38Mb/mm<sup>2</sup> 380/540mV Dual-Rail SRAM in 3nm-FinFET Technology," IEEE ISSCC Dig. Tech. Papers, pp.498–500, Feb. 2025.

- [22] X. Wang, Y. Kim, G.H. Baek, K.G. Bannore, K. Dave, A. Joushaghani, N. Kang, M. Ko, A.M. Pillai, H.C. Prakash Movva, G. Park, M. Rahman, S. Subramaniam, V. Vashishtha, T. Yang, Z. Guo, and E.A. Karl, "29.2 A 0.021µm² High-Density SRAM in Intel-18A-RibbonFET Technology with PowerVia-Backside Power Delivery," IEEE ISSCC Dig. Tech. Papers, pp.494–496, Feb. 2025.

- [23] Y. Morita, H. Fujiwara, H. Noguchi, K. Kawakami, J. Miyakoshi, S. Mikami, K. Nii, H. Kawaguchi, and M. Yoshimoto, "A Vth-Variation-Tolerant SRAM with 0.3-V Minimum Operation Voltage for Memory-Rich SoC Under DVS Environment," VLSI Cir. Symp. Dig., pp.13–14, June 2006.

- [24] H. Fujiwara, K. Nii, J. Miyakoshi, Y. Murachi, Y. Morita, H. Kawaguchi, and M. Yoshimoto, "A Two-Port SRAM for Real-Time Video Processor Saving 53% of Bitline Power with Majority Logic and Data-Bit Reordering," Proc. Int. Symp. Low Power Electronics and Devices (ISLPED), pp.61–66, Oct. 2006.

- [25] L. Chang, Y. Nakamura, R.K. Montoye, J. Sawada, A.K. Martin, K. Kinoshita, F.H. Gebara, K.B. Agarwal, D.J. Acharyya, W. Haensch, K. Hosokawa, and D. Jamsek, "A 5.3GHz 8T-SRAM with Operation Down to 0.41 V in 65nm CMOS," VLSI Cir. Symp. Dig., pp.252–253, June 2007.

- [26] M. Yabuuchi, Y. Tsukamoto, H. Fujiwara, M. Tanaka, S. Shinji, and K. Nii, "A 28-nm 1R1W 2-port 8T SRAM Macro with Screening Circuitry against Read Disturbance and Wordline Coupling Noise Failures," IEEE Trans. on VLSI Systems (IEEE Trans. Very Large Scale Integr. (VLSI) Syst.), vol.26, no.11, pp.2335–2344, 2018.

- [27] J. Kulkarni, B. Geuskens, T. Karnik, M. Khellah, J. Tschanz, and V. De, "Capacitive-coupling wordline boosting with self-induced VCC collapse for write VMIN reduction in 22-nm 8T SRAM," IEEE ISSCC Dig. Tech. Papers, pp.234–236, Feb. 2012.

- [28] J. Keane, J. Kulkarni, K.-H. Koo, S. Nalam, Z. Guo, E. Karl, and K. Zhang, "17.2 5.6Mb/mm2 1R1W 8T SRAM arrays operating down to 560mV utilizing small-signal sensing with charge-shared bitline and asymmetric sense amplifier in 14nm FinFET CMOS technology," IEEE ISSCC Dig. Tech. Papers, pp.308–309, Feb. 2016.

- [29] J.P. Kulkarni, A. Malavasi, C. Augustine, C. Tokunaga, J. Tschanz, M.M. Khellah, and V. De, "Low Swing and Column Multiplexed Bitline Techniques for Low-Vmin, Noise-Tolerant, High-Density, 1R1W 8T-Bitcell SRAM in 10nm FinFET CMOS," VLSI Cir. Symp. Dig., pp.1–2, June 2020.

- [30] A. Fritsch, R. Joshi, S. Chakraborty, H. Wetter, U. Srinivasan, M. Hyde, O. Torreiter, M. Kugel, D. Radko, H. Kim, and D. Friedman, "24.1 A 6.2 GHz Single Ended Current Sense Amplifier (CSA) Based Compileable 8T SRAM in 7nm FinFET Technology," IEEE ISSCC Dig. Tech. Papers, pp.334–336, Feb. 2021.

- [31] H. Okano, A. Suga, T. Shiota, Y. Takebe, Y. Nakamura, N. Higaki, H. Kimura, H. Miyake, T. Satoh, K. Kawasaki, R. Sasagawa, W. Shibamoto, M. Sasaki, N. Ando, T. Yamana, I. Fukushi, S. Tago, F. Hayakawa, T. Kamigata, S. Imai, A. Satoh, Y. Hatta, N. Nishimura, Y. Asada, T. Sukemura, S. Ando, and H. Takahashi, "An 8-Way VLIW Embedded Multimedia Processor Built in 7-Layer Metal 0.11 /spl mu/m CMOS Technology," IEEE ISSCC Dig. Tech. Papers, vol.1, pp.374–375, Feb. 2002.

- [32] T. Shiota, K. Kawasaki, Y. Kawabe, W. Shibamoto, A. Sato, T. Hashimoto, F. Hayakawa, S. Tago, H. Okano, Y. Nakamura, H. Miyake, A. Suga, and H. Takahashi, "A 51.2 GOPS 1.0 GB/s-DMA Single-Chip Multi-Processor Integrating Quadruple 8-Way VLIW Processors," IEEE ISSCC Dig. Tech. Papers, pp.194–195, 593, Feb. 2005.

- [33] M. Nakajima, T. Yamamoto, M. Yamasaki, K. Kaneko, and T. Hosoki, "Homogeneous Dual-Processor core with Shared L1 Cache for Mobile Multimedia SoC," VLSI Cir. Symp. Dig., pp.216–217, June 2007.

- [34] I. Loi, L. Benini, "A multi banked Multi-ported Non-blocking shared L2 cache for MPSoC platforms," Design, Automation & Test in Europe Conference & Exhibition (DATE), pp.1–6, March 2014.

- [35] K. Nii, Y. Tsukamoto, M. Yabuuchi, Y. Masuda, S. Imaoka, K. Usui, S. Ohbayashi, H. Makino, and H. Shinohara, "Synchronous Ultra-High-Density 2RW Dual-Port 8T-SRAM With Circumvention of Simultaneous Common-Row-Access," IEEE J. of Solid-State Circuits, vol.44, no.3, pp.977–986, March 2009.

- [36] Y. Ishii, H. Fujiwara, K. Nii, H. Chigasaki, O. Kuromiya, T. Saiki, A. Miyanishi, and Y. Kihara, "A 28-nm dual-port SRAM macro with active bitline equalizing circuitry against write disturb issue," VLSI Cir. Symp. Dig., pp.99–100, June 2010.

- [37] Y. Ishii, H. Fujiwara, S. Tanaka, Y. Tsukamoto, K. Nii, Y. Kihara, and K. Yanagisawa, "A 28 nm dual-port SRAM macro with screening circuitry against write-read disturb failure issues," IEEE J. of Solid-State Circuits, vol.46, no.11, pp.2535–2544, Nov. 2011.

- [38] J.-J. Wu, M.-F. Chang, S.-W. Lu, R. Lo, and Q. Li, "A 45-nm Dual-Port SRAM Utilizing Write-Assist Cells Against Simultaneous Access Disturbances," IEEE Trans. on Circuits and Systems II, vol.59, no.11, pp.790–794, Nov. 2012.

- [39] N.-C. Lien, C.-T. Chuang, and W.-R. Wu, "Method for resolving simultaneous same-row access in Dual-Port 8T SRAM with asynchronous dual-clock operation," Proc. IEEE Int. System-on-Chip Conf. (SOCC), pp.105–109, Sept. 2013.

- [40] S. Tanaka, Y. Ishii, M. Yabuuchi, T. Sano, K. Tanaka, Y. Tsukamoto, K. Nii, and H. Sato, "A 512-kb 1-GHz 28-nm Partially Write-Assisted Dual-Port SRAM with Self-Adjustable Negative Bias Bitline," VLSI Cir. Symp. Dig., pp.113–114, June 2014.

- [41] Y. Yokoyama, Y. Ishii, K. Tanaka, T. Fukuda, Y. Tsujihashi, A. Miyanishi, S. Asayama, K. Maekawa, K. Shiba, and K. Nii, "40 nm Dual-port and two-port SRAMs for automotive MCU applications under the wide temperature range of -40 to 170°C with test screening against write disturb issues," Proc. A-SSCC, pp.25–28, Nov. 2014.

- [42] K. Nii, M. Yabuuchi, Y. Yokoyama, Y. Ishii, T. Okagaki, M. Morimoto, Y. Tsukamoto, K. Tanaka, M. Tanaka, and S. Tanaka, "2RW dual-port SRAM design challenges in advanced technology nodes," IEEE Int. Electron Devices Meeting (IEDM), pp.11.1.1–11.1.4, Dec. 2015.

- [43] Y.-H. Chen, K.-C. Lin, C.-W. Wu, W.-M. Chan, J.-J. Liaw, H.-J. Liao, and J. Chang, "A 16 nm Dual-Port SRAM with Partial Suppressed Word-line, Dummy Read Recovery and Negative Bit-line Circuitries for Low VMIN Applications," VLSI Cir. Symp. Dig., June 2016.

- [44] T.Y. Lu, C.H. Huang, S.S. Chen, Y.T. Kuo, C.C. Lung, O. Cheng, Y. Ishii, M. Tanaka, M. Yabuuchi, Y. Sawada, S. Tanaka, and K. Nii,

- "A 28nm High-k/Metal-gate Symmetric 10T 2RW Dual-port SRAM bitcell design," International Conference on Solid State Devices and Materials (SSDM) Dig. Tech. Papers, pp.337–338, Sept. 2017.

- [45] Y. Yamamoto, T. Hasegawa, M. Yabuuchi, K. Nii, Y. Sawada, S. Tanaka, Y. Shinozaki, K. Ito, H. Shinkawata, and S. Kamohara, "An implementation of 2RW dual-port SRAM using 65 nm Silicon-on-Thin-Box (SOTB) for smart IoT," IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conf., pp.1–2, Oct. 2017.

- [46] H. Fujiwara, C.-Y. Lin, H.-Y. Pan, C.-H. Lin, P.-Y. Huang, K.-C. Lin, J.-J. Liaw, Y.-H. Chen, H.-J. Liao, and J. Chang, "24.2 A 7 nm 2.1 GHz Dual-Port SRAM with WL-RC Optimization and Dummy-Read-Recovery Circuitry to Mitigate Read- Disturb-Write Issue," IEEE ISSCC Dig. Tech. Papers, pp.390–392, Feb. 2019.

- [47] Y. Yokoyama, K. Nii, Y. Ishii, S. Tanaka, and K. Kobayashi, "Disturbance Aware Dynamic Power Reduction in Synchronous 2RW Dual-Port 8T SRAM by Self-Adjusting Wordline Pulse Timing," IEEE J. of Solid-State Circuits, vol.58, no.7, pp.2098–2108, July 2023.

- [48] H. Fujiwara, W.-C. Zhao, K. Khare, Y.-H. Nien, C.-Y. Lin, C.-H. Lin, S.-R. Liao, K. Torigoe, S. Xia, Y. Ishii, Y.-Y. Lin, J.-J. Liaw, Y.-H. Chen, H.-J. Liao, and T.-Y.J. Chang, "29.5 A 3nm 3.6GHz Dual-Port SRAM with Backend-RC Optimization and a Far-End Write-Assist Scheme," IEEE ISSCC Dig. Tech. Papers, pp.500–502, Feb. 2025.

- [49] S. Jain, L. Lin, and M. Alioto, "±CIM SRAM for Signed In-Memory Broad-Purpose Computing From DSP to Neural Processing," IEEE J. of Solid-State Circuits, vol.56, no.10, pp.2981–2992, Oct. 2021.

- [50] K. Nii, Y. Tsukamoto, T. Yoshizawa, S. Imaolka, and H. Makino, "A 90 nm dual-port SRAM with 2.04 um<sup>2</sup> 8T-thin cell using dynamically-controlled column bias scheme," IEEE ISSCC Dig. Tech. Papers, pp.508–509, 543, Feb. 2004.

- [51] N. Shibata, M. Watanabe, and Y. Tanabe, "A Current-Sensed High-Speed and Low-Power First-In-First-Out Memory Using a Wordline/Bitline-Swapped Dual-Port SRAM cell," IEEE J. of Solid-State Circuits, vol.37, no.6, pp.735–750, 2002.

- [52] https://www.xilinx.com/support/documentation/data\_sheets/ ds099.pdf

- [53] https://www.xilinx.com/support/documentation/user\_guides/ ug473\_7Series\_Memory\_Resources.pdf

- [54] T. Toi, N. Nakamura, Y. Kato, T. Awashima, and K. Wakabayashi, "High-level Synthesis Challenges for Mapping a Complete Program on a Dynamically Reconfigurable Processor," IPSJ Trans. on System LSI Design Methodology, vol.3, pp.91–104, Feb. 2010.

- [55] T. Toi, N. Nakamura, T. Fujii, T. Kitaoka, K. Togawa, K. Furuta, and T. Awashima, "Optimizing Time and Space Multiplexed Computation in a Dynamically Reconfigurable Processor," Proc. Int. Conf. on Field Programmable Tech. (ICFPT), pp.106–111, Dec. 2013.

- [56] M. Yabuuchi, Y. Sawada, T. Sano, Y. Ishii, S. Tanaka, M. Tanaka, and K. Nii, "A 6.05-Mb/mm<sup>2</sup> 16-nm FinFET double pumping 1W1R 2-port SRAM with 313 ps read access time," VLSI Cir. Symp. Dig., pp.1–2, June 2016.

- [57] Y. Ishii, M. Yabuuchi, Y. Sawada, M. Morimoto, Y. Tsukamoto, Y. Yoshida, K. Shibata, T. Sano, S. Tanaka, and K. Nii, "A 5.92-Mb/mm<sup>2</sup> 28-nm pseudo 2-read/write dual-port SRAM using double pumping circuitry," Proc. A-SSCC, pp.17–20, Nov. 2016.

- [58] C.-W. Wu, M.-H. Chang, C.-C. Chen, R. Lee, H.-J. Liao, and J. Chang, "A configurable 2-in-1 SRAM compiler with constantnegative-level write driver for Vmin in 16nm Fin-FET CMOS," Proc. A-SSCC, pp.145–148, 2014.

- [59] N. Zhang, Y.S. Kim, P. Hsu, S. Kim, D. Tao, H.-J. Liao, P.W. Wang, G. Yeap, Q. Li, and T.-Y.J. Chang, "A 4.24GHz 128X256 SRAM Operating Double Pump Read Write Same Cycle in 5nm Technology," VLSI Cir. Symp. Dig., pp.1–2, June 2023.

- [60] M. Haraguchi, Y. Fujino, Y. Yokoyama, M.-H. Chang, Y.-H. Hsu, H.-C. Cheng, K. Nii, Y. Wang, and T.-Y.J. Chang, "15.3 A 3nm Fin-FET 4.3GHz 21.1Mb/mm2 Double-Pumping 1-Read and 1-Write Pseudo-2-Port SRAM with Folded-Bitline Multi-Bank Architecture," IEEE ISSCC Dig. Tech. Papers, pp.280–282, Feb. 2024.

- [61] T. Tanaka, Y. Ishii, M. Yabuuchi, Y. Aoyagi, M. Hamada, K. Mizutani, K. Nii, H. Fujiwara, I. Wang, H.-C. Cheng, H.-J. Liao, and T.-Y.J. Chang, "A 3nm Fin-FET 19.87-Mbit/mm<sup>2</sup> 2RW Pseudo Dual-Port 6T SRAM with High-R Wire Tracking and Sequential Access Aware Dynamic Power Reduction," VLSI Cir. Symp. Dig., pp.1–2, June 2024.

- [62] B.S. Amrutur and M.A. Horowitz, "A Replica Technique for Wordline and Sense Control in Low-Power SRAM's," IEEE J. of Solid-State Circuits, vol.33, no.8, pp.1208–1219, 1998.

- [63] K. Osada, M. Khan, K. Wang, K. Shoji, K. Kuroda, S. Ikeda, and K. Ishibashi, "Universal-Vdd 0.65-2.0V 32kB Cache using Voltage-Adapted Timing-Generation Scheme and a Lithographical-Symmetric Cell," IEEE ISSCC Dig. Tech. Papers, pp.168–169, Feb. 2001.

- [64] Y. Yoshizawa, K. Nii, and S. Imaoka, "Semiconductor memory device internally generating internal data read timing," Patent US6804153B2, Oct. 2004.

Koji Nii received B.E. and M.E. degrees in electrical engineering from Tokushima University, Tokushima, Japan, in 1988 and 1990, respectively, and a Ph.D. degree in informatics and electronics engineering from Kobe University, Hyogo, Japan, in 2008. In 1990, he joined the ASIC Design Engineering Center, Mitsubishi Electric Corporation, Itami, Japan, where he has been working on designing 0.8um to 130 nm embedded SRAMs and CAMs for CMOS ASICs and researching on SOI SRAM development. In

2003, he was transferred to Renesas Technology Corporation, Itami, Japan, which is a joint company of Mitsubishi Electric Corp. and Hitachi Ltd. in the semiconductor field. He has worked on designing 45 nm to 90 nm embedded low-power and high-speed SRAMs and researching on SRAM assist circuits techniques to enhance the functional margin against variations. He transferred his work location to Kodaira, Tokyo on April 2009, where he has worked on the research and development of embedded SRAM/TCAM/ROM and low-power design techniques with power gating in 28 nm High-k/Metalgate, advanced 7-16 nm Fin-FETs, and FD-SOI SRAM macros. He moved to Floadia Corporation, which is an embedded Flash IP company in Kodaira, Tokyo, Japan, in 2018. He is now with TSMC Design Technology Japan, Inc., Yokohama, Japan, in charge of a head of memory design team for developing advanced Fin-FET/Gate-All-Around (GAA) SRAM compilers, and custom cache SRAMs, Register files, CAMs and computing-in-memory (CiM) IPs. His current responsibility is Director, Japan Memory Design Program, Memory Solution Division. Dr. Nii holds over 100 US patents and published 45 IEEE/IEICE papers and over 100 talks at major international conferences. He received the Best Paper Awards at IEEE International Conference on Microelectronic Test Structures (ICMTS) in 2007 and IEEE International Symposium on Quality Electronic Design (ISQED) in 2013. He also received the LSI IP Design Awards in 2007 and 2008, Japan. He is a Technical Program Committee of the IEEE VLSI Symposium (2023-) and was the IEEE CICC (2010-2016) and IEEE IEDM (2015-2016). He is an Associated Editor of the IEEE Trans. on VLSI Systems (2015-). He is a senior member of the IEEE Solid-State Circuits Society, IEEE Computer Society and the IEEE Electron Devices Society. He is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan. He was also a Visiting Professor of Graduate School of Natural Science and Technology, Kanazawa University, Ishikawa, Japan (2012–2018) and now is a Senior Fellow of Green Innovation Lab., Kyoto Institute of Technology, Kyoto, Japan (2019-).

**Kazutoshi Kobayashi** received his B.E., M.E. and Ph.D. in Electronic Engineering from Kyoto University, Japan in 1991, 1993, 1999, respectively. Starting as an Assistant Professor in 1993, he was promoted to associate professor in the Graduate School of Informatics, Kyoto University, and stayed in that position until 2009. For two years during this time, he acted as associate professor of VLSI Design and Education Center (VDEC) at the University of Tokyo. Since 2009, he has been a professor at Kyoto Institute

of Technology. While in the past he focused on reconfigurable architectures utilizing device variations, his current research interest is in improving the reliability (Soft Errors, Bias Temperature Instability and Plasma Induced Damage) of current and future VLSIs. He started research related to gate drivers for power transistors since 2013. In 2022, he was nominated for one of the project managers of Moonshot Goal 6 "Realization of a fault-tolerant universal quantum computer that will revolutionize economy, industry, and security by 2050" and organized his project team named "Development of Scalable Highly Integrated Quantum Bit Error Correction System" abbreviated as QUBECS. He was the recipient of the IEICE best paper award in 2009, the IRPS best poster award in 2013, the ICICDT best paper award in 2019 and the IEICE Electronics Society award in 2021.