# 宇宙機用集積回路に適した薄膜 BOX FDSOI プロセスで試作した リングオシレータのトータルドーズ効果の実測評価

吉田 高士 古田 潤 小林 和淑

†京都工芸繊維大学 〒606-8585 京都市左京区松ヶ崎橋上町

E-mail: †tyoshida@vlsi.es.kit.ac.jp, ††{furuta,kazutoshi.kobayashi}@kit.ac.jp

あらまし 宇宙で用いられる機器には半導体を用いた集積回路が必要不可欠であるが、宇宙空間で長期運用が求められる半導体デバイスでは宇宙放射線によるトータルドーズ効果 (TID) が問題となる。FDSOI プロセスは放射線による一時的な故障であるソフトエラーに強い一方、BOX 層を有するために TID に対して脆弱になる。本稿では $\gamma$ 線の照射 実験を行い、リングオシレータ (RO) の発振周波数の変化を調べることで 65 nm 薄膜 FDSOI プロセスの TID 耐性を評価した。 $\gamma$ 線照射の代替として、簡易的に行える  $\alpha$ 線照射による TID の評価手法について提案する。

キーワード 宇宙機, トータルドーズ効果, FDSOI, リングオシレータ,  $\gamma$ 線,  $\alpha$ 線

# Measurement Results of Total Ionizing Dose Effect on Ring Oscillators Fabricated by a Thin-BOX FDSOI Process for Outer-space Mission

Takashi YOSHIDA<sup>†</sup>, Jun FURUTA<sup>†</sup>, and Kazutoshi KOBAYASHI<sup>†</sup>

† Kyoto Institute of Technology, Kyoto, Japan

E-mail: †tyoshida@vlsi.es.kit.ac.jp, ††{furuta,kazutoshi.kobayashi}@kit.ac.jp

**Abstract** The Total Ionizing Dose (TID) effect is one of the major concerns for semiconductor devices in outer space, where high and low energy particles penetrate to space crafts. The Fully-Depleted Silicon On Insulator (FDSOI) process has brought a significant improvement of electronic devices resilient to soft errors that are major reliability concerns for semiconductor devices in outer space. However, due to the buried oxide (BOX) layer, it becomes more sensitive to TID than a conventional planer bulk process. In this paper, we evaluate TID tolerance of 65 nm thin BOX FDSOI process by measuring Ring Ocillator (RO) frequecy. By comparing the irradiation of  $\alpha$  ray and  $\gamma$  ray, it was shown that  $\alpha$  ray irradiation that can be done in a laboratory can be used instead of  $\gamma$  ray irradiation that must be done under a secured measurement facility.

Key words Space Craft, Total Ionizing Dose Effect, FDSOI, Ring Oscillator, Gamma-ray, Alpha-ray,

## 1. 序 論

NASA は 2019 年,火星到達を視野に入れた月面着陸計画であるアルテミス計画を発表したが,日本でも JAXA が月面で 1万 km 以上走行が可能となる有人与圧ローバーについて研究を進めるなど,国内外間わず宇宙開発が加速している [1], [2]. 宇宙開発のためのロケットや宇宙船,基地などにも集積回路は必要不可欠である。宇宙機は一度宇宙空間にでると修理やメンテナンスが困難であり,一つの誤動作や故障がシステム全体に影響を与え重大な事故につながるため,高い信頼性が求められる。しかし,集積回路を主とする半導体は宇宙放射線に曝されることが知られている。そのため宇宙機に用いられる集積回路は放射線耐性を十分に保障する必要がある。

放射線が半導体に与える主な影響として、電離作用が挙げられる。電離作用とは、放射線が物質中を通過・衝突する際に放射線が持つエネルギーにより原子が持つ軌道電子がはじき出されることで電子正孔対が発生する作用である。この電子正孔対が集積回路に及ぼす影響はシングルイベント効果 (SEE: Single Event Effect) とトータルドーズ効果 (TID: Total Ionizing Dose effect) に分類される。SEE は 1 つの放射線粒子が集積回路に突入することにより発生する故障のことを指しており、ラッチの保持値が反転するソフトエラーや、放射線起因の大電流によるラッチアップなどが含まれる [3], [4].

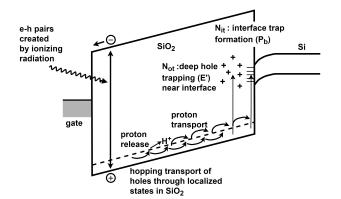

一方で TID は集積回路が長期間にわたって継続的に放射線を受けることにより発生する蓄積的な劣化現象である。図 1 に MOS トランジスタにおける TID の発生機構を示す [5]. 放射線による電離作用でトランジスタの酸化膜内に発生した電子正孔

図1 TID の発生機構[5]

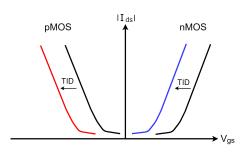

図2 TID によるしきい値シフト[6]

対のうち、正孔がデバイスの酸化膜内の欠陥や界面準位にトラップされ、その正孔によりリーク電流の増加やしきい値変動が生じる。図2に示すようにTIDではnMOSのしきい値は減少、pMOSのしきい値は増加する[6]. 再起動により回復が可能なソフトエラーとは異なり、TIDは蓄積的な劣化であるため、長期運用が想定される宇宙機ではこの効果に対する耐性が求められる。デバイスのプロセスによりTIDの耐性も変化するため、それぞれのプロセスにおける耐性の評価が必要である.

本稿では、集積回路に放射線を照射し、搭載されたリングオシレータ (RO) の発振周波数の変化を調べることで TID によるしきい値変動を評価する。異なる構成の RO の発振周波数の比較から薄膜 FDSOI プロセスの TID 耐性を調べる。  $\alpha$  線を用いた TID の簡易的な評価手法についても提案する。

本稿の構成を述べる。第2節では bulk プロセスと薄膜 FDSOI の比較を行う。第3節では nMOS と pMOS の影響を分離した RO を用いた評価結果を示し,さらに放射線照射時のバイアス 印加の影響についても実測結果から述べる。第4節では NAND型,NOR型,INV型の3種類のROのTID 耐性を実測結果から比較する。第5節では $\alpha$ 線を用いたTIDの評価手法の有用性と既存手法である $\gamma$ 線照射との違いを説明する。第6節でまと める。

#### 2. bulk 構造と FDSOI 構造における TID

本章では bulk 構造と SOI 構造における TID の違いについて述べ、RO を用いた実測結果を示す.

# 2.1 bulk 構造

bulk 構造とは標準的な CMOS トランジスタ構造である. この bulk 構造において, 100 nm 以上のプロセスでは TID の主な

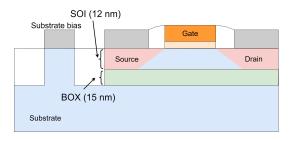

図3 薄膜 FDSOI 構造の断面図

原因はゲート酸化膜に蓄積する正孔である。しかし,スケーリングによりプロセスノードが小さくなるにつれてゲート酸化膜が薄膜化し,ゲート酸化膜内の正孔の影響は無視できるほど小さくなった。一方で素子分離 (STI: Shallow Trench Isolation) の  $SiO_2$  における正孔の蓄積の影響が顕在化している [7], [8].

#### 2.2 SOI 構造

bulk 構造に対して、シリコン基板とトランジスタの間に絶縁層として埋め込み酸化層 (BOX 層)を挿入した構造を SOI (Silicon On Insulator) 構造と呼ぶ。SOI 構造は BOX 層を挿入することでトランジスタの寄生容量を小さくすることができ、高速動作、低電圧での動作が可能であり、BOX 層の電子正孔対の遮蔽効果によりソフトエラー耐性が大幅に向上することが知られている [9]. しかし、BOX 層はゲート酸化膜よりもはるかに厚く、そこに蓄積する正孔の影響が大きくなるため、SOI 構造は bulk 構造に比べて TID 耐性が低くなる [10]~[12]. 本稿では SOI 構造の中でも図 3 に示すような完全空乏型である 65 nm 薄膜 FDSOI (Fully Depleted SOI) 構造を用いて実測を行う。BOX 層の厚さが 15 nm と従来の FDSOI プロセスに比べて非常に薄く BOX 層を通じて基板バイアスを制御することができる.

#### 2.3 実測による比較

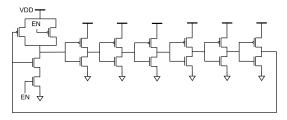

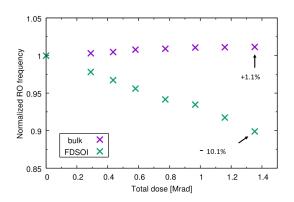

上記 2 つの構造の TID 耐性を放射線照射実験による実測結果から比較する. bulk, FDSOI ともに 65 nm のプロセスノードで、回路構造も全く同じチップに対し、 $^{60}$ Co を線源とする  $\gamma$ 線 (線量率:129 rad/s) の照射を行い、チップに搭載されている RO の発振周波数の変化を測定する. RO は図 4 に示すように CMOS 構造のインバータ 6 つ、イネーブル信号入力用に CMOS 構造の NAND が 1 つが連なった 7 段 RO となっている.

図 5 に RO の発振周波数の変化の実測結果を示す. 横軸は吸収線量,縦軸は発振周波数を表しており,照射前の発振周波数で正規化している. 吸収線量 1.4 Mrad の時点で bulk チップの RO は発振周波数が 1.1% 増加, 薄膜 FDSOI チップの RO は10.1% 減少した. この結果から,BOX 層が薄くても,FDSOI 構造は bulk 構造に比べて TID に対して脆弱であることが分かる. 図 2 で示した通り,TID により nMOS はしきい値が減少,pMOS はしきい値が増加するが,RO の場合,しきい値の減少は発振周波数を増加させ,しきい値の増加は発振周波数を減少させる. bulk 構造では発振周波数が増加したが,これは nMOS のしきい減少の影響が pMOS のしきい値増加の影響よりも大きかったことが原因として考えられる.

図4 CMOS インバータによる7段ROの回路図

図 5 bulk 構造と FDSOI における TID による RO の発振周波数の変化

# 3. nMOS と pMOS の影響を分離した RO による 比較

前節で述べたように、TID による nMOS のしきい値減少は発振周波数は減少させ、pMOS のしきい値増加は発振周波数を増加させる。図 4 のような CMOS インバータを用いた RO では nMOS と pMOS の両者の影響が混在するため、それぞれのしきい値変化量を調べることができない。

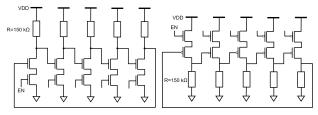

TID により nMOS と pMOS のしきい値がそれぞれどの程度 変動するかを調べるため,図 6 に示すような nMOS と pMOS の影響を分離した RO を用いる.図 6 の (a) は nMOS と抵抗のみ、(b) は pMOS と抵抗のみで構成されている.以降は (a) を nMOS RO, (b) を pMOS RO と呼ぶ.この RO が搭載されたチップ (第 2 節と同様に 65 nm 薄膜 FDSOI プロセスで試作) に  $^{60}$ Co を線源とする線量率 129 rad/s の  $\gamma$  線を照射する.さらに電源電圧の TID への影響を調べるため,照射時に RO の発振時以外は電源電圧 (VDD) を 0V する場合と,VDD に常に 1.2 V のバイアスを加え続ける場合の 2 条件で測定を行う.

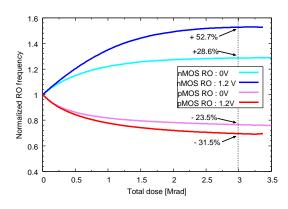

測定結果を図 7 に示す. RO の発振時以外 0 V とした場合, 吸収線量 3 Mrad の時点で nMOS RO は発振周波数が 28.6% 増加, pMOS RO は 23.5% 減少した. 常に 1.2 V とした場合, 吸収線量 3 Mrad の時点で nMOS RO は 52.7% 増加, pMOS RO は 31.5% 減少した.

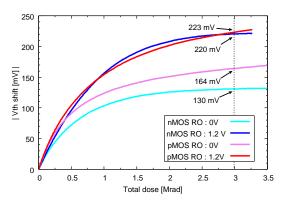

この結果から TID によるしきい値変動を求める. SPICE シミュレーションでしきい値をパラメータスイープした時の発振周波数の変化を調べ、そのデータから実測でのしきい値変動を算出する. 算出したしきい値変動の絶対値を図 8 に示す. VDD を 0 V とした条件では吸収線量 3 Mrad の時点で、nMOS は 130 mV、pMOS は 164 mV しきい値が変動している. VDD を 1.2 V とした条件ではnMOS は 220 mV、pMOS は 223 mV

(a) nMOS と抵抗のみを用いた RO (l

(b) pMOS と抵抗のみを用いた RO

図 6 nMOS と pMOS の影響を分離した RO の回路図

図7 nMOS RO と pMOS RO の発振周波数の変化の比較

図 8 実測結果と SPICE シミュレーションから算出した TID によるしきい値シフト

シフトしている.いずれの場合も変化は飽和していく傾向がある.nMOS,pMOSともに照射中に電圧バイアスを加え続けているとしきい値変動が大きくなることがわかる.この原因について考える.図1で示したように放射線の電離作用により電子正孔対が発生する.発生した電子正孔対のうち,電子は有効質量が小さいために正孔よりも比較的速く酸化膜内から排出される.その際電子の一部は正孔と再結合して消滅する.再結合せず残った正孔が欠陥や界面準位にトラップされる.再結合をず残った正孔が欠陥や界面準位にトラップされる.論理ゲートに電圧を印加した場合,バンド構造の傾きが大きくなるため,発生した電子がより速く排出されるため,正孔との再結合率が下がる.結果としてトラップされる正孔が増え,TIDによるしきい値変動が大きくなると考えられる.

### 4. NAND型, NOR型, INV型ROの比較

前節では nMOS や pMOS がそれぞれどのようなしきい値変化

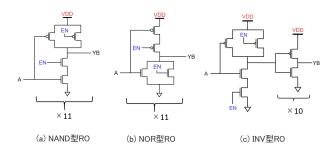

図9 3種類のROの回路図

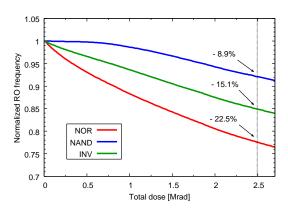

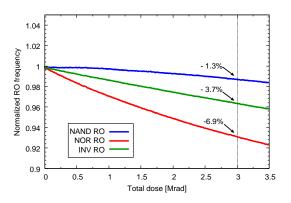

図 10 3 種類の RO の発振周波数の変化

をするかを示したが、集積回路では nMOS や pMOS は CMOS 構造で用いられ、NAND、NOR、インバータといった論理ゲートを構成する. こうした論理ゲートに対し TID がどのような影響を及ぼすかを図 9 に示すような (a)NAND 型 RO、(b)NOR 型 RO、(c)INV 型 RO を用いることで実測評価した. 放射線の照射は前節までと同様に  $^{60}$ Co を線源とする  $\gamma$  線を用い、線量率は 129 rad/s とした.

測定結果を図 10 に示す。 2.5 Mrad の時点で NAND 型 RO の発振周波数は 8.9% 減少,NOR 型 RO は 22.5% 減少,INV 型 RO は 15.1% 減少した。第 2 節でも示した結果と同様,65 nm 薄膜 FDSOI プロセスにおいて,CMOS インバータを用いた RO は TID により発振周波数が減少した。発振周波数が減少しているということは,インバータ型 RO において pMOS のしきい値増加が nMOS のしきい値減少よりも発振周波数により大きい影響を与えることが分かる。

一方 NAND 型 RO はインバータ型 RO に比べて発振周波数の減少量が少ない。 しきい値の変動はトランジスタのオン抵抗の変化と考えることができ,これが発振周波数を左右している。 NAND では nMOS 2 つが直列になっているため nMOS 1 つの場合に比べてしきい値減少によるオン抵抗の減少が倍になる。 一方 pMOS は並列となっているため,しきい値増加によるオン抵抗の増加は pMOS 1 つの場合と変わらない。そのため nMOS が発振周波数を増加させる効果がインバータ型 RO に比べて大きくなり,結果として発振周波数の減少が小さくなると考えられる。 NOR 型 RO についても同様である。 NOR 型では pMOS が直列,nMOS が並列となるため pMOS のしきい値増加によるオン抵抗の増加が倍となることでインバータ型 RO よりも発振周波数の減少が大きくなる。

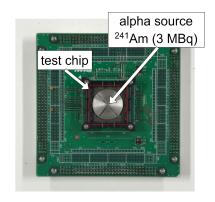

図 11  $\alpha$ 線源を用いた LSI への  $\alpha$  線照射

### 5. α線照射とγ線照射の比較

宇宙空間一般においては太陽からの陽子線による TID が支配的である. 地球の磁場が及ぶ範囲であるヴァンアレン帯においては電子線が多量に存在するためこれも TID に寄与する. 電子線が IC 等のシールドに入射した際の制動 X 線も TID に寄与する. そのため TID の実測評価には陽子線や電子線の評価が適していると考えられるが,加速器が必要のため照射コストの観点から  $\gamma$  線,もしくは X 線が一般的に用いられる [13], [14]. しかし,比較的コストが低いとはいえ  $\gamma$  線や X 線の照射には照射施設が必要であり,照射室内での照射に限られ,時間的な制約も伴う.測定器も TID の影響を受けてしまうため大型の LSI テスタ等を用いて動作を行いながらの照射も困難である.そこで本章では  $\alpha$  線を用いた簡易的な TID の測定手法を提案する.

$\alpha$ 線は図 11 に示すよう形で LSI への照射が行える.  $\alpha$ 線は 宇宙空間において TID に寄与する可能性が低い点や,線源から の距離依存性が高く,線量率に誤差が出やすいという点がデメリットとして挙げられるが,一方で照射施設を必要としないた め,LSI テスタを用いて動作させながらの照射が可能あり,時間的制約もない. そのため大まかな TID への耐性や変化の特性を調べる際の簡易的な照射実験として有効であると考える.  $^{241}$ Am を線源とした 3 MBq(線量率:12 rad/s) の  $\alpha$ 線源を用いた 照射を行い, $\gamma$ 線と比較することで  $\alpha$ 線の有用性を調べた.

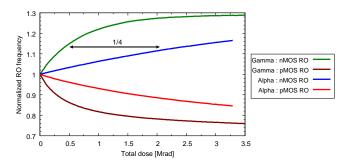

図 12 に第 3 節でも使用した nMOS RO と pMOS RO の  $\gamma$  線と  $\alpha$  線の照射による発振周波数の変化の実測結果を示す。 nMOS RO の発振周波数が増加,pMOS RO の発振周波数が減少する傾向は  $\gamma$  線と  $\alpha$  線ともに同様だが,吸収線量に対する変化の割合は  $\alpha$  線が  $\gamma$  線の 1/4 程度小さくなることが分かる。第 4 節で用いた 3 種類の RO に対しても同様の  $\alpha$  線の照射を行った。 結果は図 13 のようになり,変化の傾向は  $\gamma$  線を照射した場合と一致したが,吸収線量当たりの変化量に違いは生じた.

吸収線量当たりの変化量に違いが生じた原因は、 $\gamma$ 線と $\alpha$ 線の LET(Linear Energy Transfer)の違いだと考えられる。LET とは放射線が単位長さあたりに平均して失うエネルギーのことを指す。 $\gamma$ 線は低 LET 線、 $\alpha$ 線は高 LET 線に分類される。LET が高いと、電離作用により発生する電子正孔対の密度が高くなる。発生密度が高くなると、再結合率が高くなるとトラップされる正孔が減少するため、TID による

図 12 γ線照射とα線照射による TID の差異の実測結果

図 13  $\alpha$ 線によるインバータ型 RO, NAND 型 RO, NOR 型 RO の発振周波数の変化

変化が小さくなる[6]. このため, α線を TID の測定のための 照射に用いる場合は吸収線量に対する変化量の違いを考慮して 校正する必要がある. しかし,変化のおおまかな傾向は調べる ことができるため,簡易的な手法としては有用であると考えられる.

### 6. 結 論

放射線照射による RO の発振周波数の変化の実測結果から 65 nm 薄膜 FDSOI プロセスの TID 耐性を評価した. bulk と薄膜 FDSOI プロセスの比較から、薄膜 FDSOI プロセスの TID に対 する脆弱性を明らかにした. nMOS と pMOS の影響を分離した RO を用いた実測結果からは、3 Mrad のγ線照射により nMOS は 130 mV しきい値が減少, pMOS は 164 mV しきい値が増加す ることが分かった. 照射中に電源電圧 1.2V を加え続けた場合, OV とした場合よりもしきい値の変化量が大きくなり、nMOS は 220 mV 増加, pMOS は 223 mV 減少した. これは電離作用に より発生した電子正孔対の再結合率が電圧バイアスにより低く なることで、トラップされる正孔が増えることが原因と考えら れる. 3 種類の RO を用いた評価では、2.5 Mrad の  $\gamma$  線の照射 により発振周波数が NAND 型 RO では 7.4% 減少, NOR 型 RO では 21.8% 減少, インバータ型 RO では 14.5% 減少した. こ の違いは nMOS と pMOS がそれぞれ直列になっているか並列 になっているかに起因している. γ線照射とα線照射の比較か ら,吸収線量当たりの変化の大きさには違いがあるが,変化の 傾向は一致することが分かった. 簡易的な手法として  $\alpha$  線照射 が TID 耐性の評価に有用であることを示した.

#### 文 献

- NASA, "Nasa publishes artemis plan to land first woman, next man on moon in 2024," Sept. 22, 2020. https://www.nasa.gov/pressrelease/nasa-publishes-artemis-plan-to-land-first-woman-next-man-onmoon-in-2024/.

- [2] JAXA, "Jaxa とトヨタ、国際宇宙探査ミッションへの挑戦に合意-将来の月面でのモビリティ実現を目指して-," Mar. 12, 2019. https://www.jaxa.jp/press/2019/03/20190312a\_j.html.

- [3] 戸坂義春, "知っておきたいソフト・エラーの実態," 日経エレクトロニクス, 2005 年 7 月 24 日号, pp.145-156, 2005.

- [4] M. Jiang, G. Fu, B. Wan, M. Jia, and Y. Qiu, "Research on single event latch-up effect of cmos based on tcad," 2017 Second International Conference on Reliability Systems Engineering (ICRSE), pp.1–5, 2017.

- [5] F.B. McLean and T.R. Oldham, "Basic mechanisms of radiation effects in electronic materials and devicesd," Harry Diamond Lab. Tech. Rep., vol.HDL-TR, p.2129, Sept. 1987.

- [6] H.J. Barnaby, "Total-ionizing-dose effects in modern cmos technologies," IEEE Transactions on Nuclear Science, vol.53, no.6, pp.3103–3121, Dec. 2006.

- [7] R.M. Chen, Z.J. Diggins, N.N. Mahatme, L. Wang, E.X. Zhang, Y.P. Chen, Y.N. Liu, B. Narasimham, A.F. Witulski, B.L. Bhuva, and D.M. Fleetwood, "Effects of total-ionizing-dose irradiation on seu- and set-induced soft errors in bulk 40-nm sequential circuits," IEEE Transactions on Nuclear Science, vol.64, no.1, pp.471–476, Jan. 2017.

- [8] F. Faccio and G. Cervelli, "Radiation-induced edge effects in deep submicron cmos transistors," IEEE Transactions on Nuclear Science, vol.52, no.6, pp.2413–2420, Dec. 2005.

- [9] P. Roche, J. Autran, G. Gasiot, and D. Munteanu, "Technology downscaling worsening radiation effects in bulk: Soi to the rescue," 2013 IEEE International Electron Devices Meeting, pp.31.1.1–31.1.4, 2013.

- [10] L. Ding, S. Gerardin, M. Bagatin, S. Mattiazzo, D. Bisello, and A. Paccagnella, "Drain current collapse in 65 nm pmos transistors after exposure to grad dose," IEEE Transactions on Nuclear Science, vol.62, no.6, pp.2899–2905, Dec. 2015.

- [11] J. Prinzie, J. Christiansen, P. Moreira, M. Steyaert, and P. Leroux, "Comparison of a 65 nm cmos ring- and lc-oscillator based pll in terms of tid and seu sensitivity," IEEE Transactions on Nuclear Science, vol.64, no.1, pp.245–252, Jan. 2017.

- [12] T. Yoshida, J. Furuta, and K. Kobayashi, "Total ionizing dose effects by alpha irradiation on circuit performance and seu tolerance in thin box fdsoi process," IEEE International Symposium on On-Line Testing and Robust System Design), pp.236–238, June. 2019.

- [13] D. Yun, M. Park, C. Lim, and S. Baeg, "Study of tid effects on one row hammering using gamma in ddr4 sdrams," 2018 IEEE International Reliability Physics Symposium (IRPS), pp.P–SE.2–1–P–SE.2– 5, March 2018.

- [14] L.N. Kessarinskiy, D.V. Boychenko, A.G. Petrov, P.V. Nekrasov, A.V. Sogoyan, V.S. Anashin, and P.A. Chubunov, "Compendium of tid comparative results under x-ray, gamma and linac irradiation," 2014 IEEE Radiation Effects Data Workshop (REDW), pp.1–3, July 2014.