# 65nm バルクと Thin BOX FD-SOI プロセスにおける 冗長化フリップフロップのソフトエラー耐性の実測と評価

曽根崎詠二 $^{\dagger}$  久保田勘人 $^{\dagger}$  増田 政基 $^{\dagger}$  神田 翔平 $^{\dagger}$  古田 潤 $^{\dagger}$  小林 和淑 $^{\dagger}$

†京都工芸繊維大学大学院 工芸科学研究科 電子システム工学専攻 〒606-8585 京都市左京区松ヶ崎

あらまし 集積回路の微細化に伴って、ソフトエラーにより信頼性の低下が顕在化している。ソフトエラーの対策技術として TMRFF のような冗長化回路が多数提案されているが、冗長化回路は面積・消費電力が増大する。面積を削減するのは困難であるが、消費電力は低消費電力技術を用いることで削減できる。そこで、我々の研究グループでは高信頼性回路である BCDMR 構造と DICE 構造に低消費電力技術を組み合わせた BCDMRACFF と DICEACFF を提案した。本稿では、65nm バルクと Thin BOX FD-SOI プロセスでテストチップを試作し、BCDMRACFF と DICEACFF のソフトエラー耐性を評価した。バルクプロセスでは BCDMRACFF と DICEACFF のソフトエラー耐性を評価した。バルクプロセスでは BCDMRACFF と DICEACFF のソフトエラー耐性であった。Thin BOX FD-SOI では両回路合わせてソフトエラーが一つしか発生せず、非常に高いソフトエラー耐性であることを示した。

キーワード ソフトエラー、BCDMR、冗長化、重イオン、低消費電力

# Evaluation of Soft Error Tolerance of Redundant Flip-Flop in 65nm Bulk and FD-SOI Processes

Eiji SONEZAKI $^\dagger$ , Kanto KUBOTA $^\dagger$ , Masaki MASUDA $^\dagger$ , Shohei KANDA $^\dagger$ , Jun FURUTA $^\dagger$ , and Kazutoshi KOBAYASHI $^\dagger$

† Kyoto Institute of Teshnology Graduate School of Science and Technology

Abstract According to process down scaling, LSI becomes less reliable for soft errors. To increase the tolerance of FFs for soft errors, several redundant FF structures are proposed such as the TMR FF. However, the redundant FF has large area and power consumption overhead. Although it is very hard to reduce the area overhead, the power consumption overhead can be reduced to adapt low power consumption techniques. We proposed a low power consumption redundant FFs (BCDMRACFF, DICEACFF) by combining conventional redundant FFs (BCDMRFF, DICEFF) and low power consumption techniques. We evaluated tolerance for soft error of proposed FFs in 65nm Bulk and Thin BOX FD-SOI. In Bulk, tolerance of BCDMRACFF and DICEACFF have 20 and 17 times higher than TGFF, respectively. In Thin BOX FD-SOI, number of error in proposed FFs is only one. Thin BOX FD-SOI + BCDMR or DICE have very high tolerance for soft error.

Key words soft error, BCDMR, redundant FF, heavy Ion, low power consumption

#### 1. 序 論

近年、集積回路に集積されるトランジスタの微細化に伴って、信頼性の低下が顕在化してきた [1]。信頼性を低下させる要因の一つにソフトエラーがある。ソフトエラーとは、 $\alpha$  粒子や中性子、重イオンがデバイス内に突入してきたことで発生する一時的な故障のことである [2]。再起動や命令の再実行により修復可

能であるが、航空機や自動車、医療機器など高い信頼性が求められる製品では一度の故障でも重大な事故を引き起こしかねないため、ソフトエラー対策は必須である [3]。ソフトエラーの対策には MOSFET のソース・ドレインの直下に絶縁層を埋め込むことでボディと基板を分離したデバイスである SOI (Sillicon On insulator) プロセスなどがデバイスレベルの対策として用いられている。バルクプロセスに比べてデバイスの製造工程が増

えるためコストが高いため、FF を多重化するなど回路レベルの対策が主流であり、現在までに TMR (Triple Modular Redundancy) [4], DICE (Dual Interlocked strage CEll) [5]、BISER (Built In Soft Error Resilience) [6] など多様な耐ソフトエラーFF が提案されている。耐ソフトエラーFF は冗長化により高い信頼性を有するが、面積および消費電力のオーバーヘッドとトレードオフの関係にある。トランジスタを追加するために面積オーバーヘッドを減らすのは非常に難しいが、電力オーバーヘッドは低消費電力技術により削減可能である。我々の研究グループでは低消費電力回路である ACFF に DICE 構造またはBISER を改良した BCDMR 構造を組み合わせることで高性能かつ高信頼性冗長化 FF を提案する。

本稿の構成は以下の通りである。2節で提案回路を含む冗長 化FFの回路構造について述べる。3節では設計したテストチップの概要について述べる。4節では重イオン照射試験の実験方法と実験結果について述べる。5節では結論を述べる。

#### 2. 低消費電力冗長化 FF

本章では非冗長化 FF や冗長化 FF について述べた後に提案する低消費電力冗長化 FF について述べる。

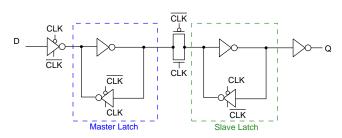

#### 2.1 TGFF

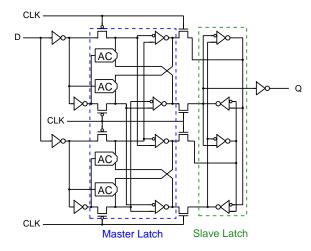

現在一般的に用いられている D 型 FF である TGFF (Transimission Gate Flip-Flop) の回路図を図 1 に示す。非冗長化 FF であり、耐ソフトエラー回路や低消費電力回路ではない。様々な FF の評価を行う際、TGFF を基準として用いる。マスターラッチとスレーブラッチの 2 つのラッチの組み合わせによって構成されており、2 つのラッチの間はトランスミッションゲートで接続している。CLK=1 だとマスターラッチが保持し、CLK=0 だとスレーブラッチが値を保持する。CLK 信号の立ち上がりもしくは立ち下がりで値を切り替える。

図 1 TGFF

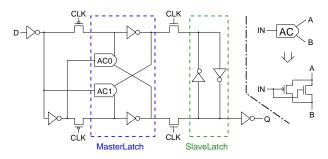

# 2.2 ACFF

ACFF (Adaptive Coupling Flip-Flop) の回路図を図 2 に示す [7]。ACFF も TGFF と同様に非冗長化 FF であり、耐ソフトエラー回路ではないが、AC 素子を用いた低消費電力回路である。ACFF は TGFF と異なり、ラッチの切り替えにパストランジスタを用いているためクロックの逆相の信号が不必要となるため、クロックバッファを排除できる。低活性化率領域ではクロックバッファでの消費電力が支配的になるため、クロックバッファのない ACFF は低消費電力を実現できる。

図 2 ACFF

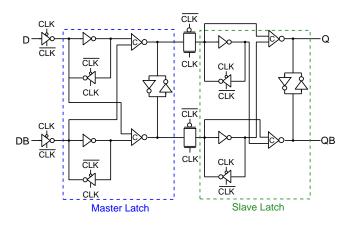

#### 2.3 BCDMR FF

BCDMRFF (Bistable Cross-coupled Dual Modular Redundancy Flip-Flop) の回路図を図 3 に示す [8]。TGFF を二重化し、マスターラッチとスレーブラッチの後段に "2C + K" を挿入した冗長化 FF である。"2C + K" は 2 つの Muller's C-element と一つの Keeper でできている。もし、2 つのラッチのうち一方でソフトエラーが発生しても C-element がハイインピーダンスになり、Keeper が元の信号を保持する。BCDM-RFF でソフトエラーが起こるには 2 つのラッチと Keeper のうち 2 つが反転する必要があるために高い信頼性を有する。BCDMRFF は C-element を二重化することにより BISER の欠点を改良した回路である。C-element を二重化することで、C-element で発生したノイズパルスである SET (Single Event Transient) によるエラーも防ぐことができる [8]。

図 3 BCDMRFF

#### 2.4 BCDMR ACFF

BCDMR ACFF の回路図を図4に示す。ACFFにBCDMR構造を適用した冗長化FFである。BCDMRFFと同様にKeeperと2つのC-elementがそれぞれのラッチに挿入されている。C-elementで発生するSETによるエラーにも強い。C-elementとKeeperを挿入する都合により、スレーブラッチにはインバータが挿入されている。ACFFを基にした冗長化回路であるため低活性化率領域では低消費電力を実現できる。

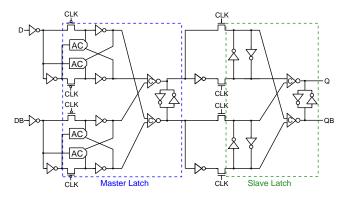

#### 2.5 DICE ACFF

DICE (Dual Interlocked CEll) ACFF の回路図を図 5 に示

図 4 BCDMRACFF

す。ACFFに DICE 構造を適用した冗長化 FF である。DICE 構造とはラッチが二重化された構造である。通常のラッチのループ構造はインバータ二段で構成されるが、DICE のループ構造は Half-C-element (HCE) と呼ばれるインバータ 4 段で構成される。4 段のループ構造によって1つの HCE の出力が反転しても他の3つの HCE によって値が補償される。ACFFを基にした冗長化回路であるため低活性化率領域では低消費電力を実現できる。

**図** 5 DICEACFF

# 3. テストチップ

本節では提案した低消費電力冗長化 FF と非冗長化 FF の ソフトエラー耐性を評価するために設計した 65nm バルクと Thin BOX FD-SOI プロセスのチップ概要と各 FF の性能比較 結果について述べる。

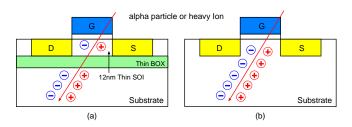

### 3.1 SOTB

完全空乏型 SOI (Fully Depleted Sillicon on Insulator) プロセスの一種である SOTB (Sillicon On Thin BOX) を図 6 に示す。通常の SOI の絶縁膜厚はおおよそ 100nm であるのに対し、SOTB はシリコン基板上に 10nm 程度の極薄の BOX 層と12nm のシリコン薄膜 (SOI 層) が形成されたトランジスタである。SOTB はバルクプロセスに比べて高いソフトエラー耐性を有するトランジスタである [10]。その理由はソフトエラーが発生する要因である誘起電荷収集を抑制できるからである。誘起

電荷収集とは、粒子線により基板で発生したキャリアがドレイン領域に収集されることである。この現象により論理ゲートの出力にノイズが発生する。SOTBではBOX層により基板で発生したキャリアが収集されずに発生するノイズが小さくなる、もしくは発生しなくなるため高いソフトエラー耐性を実現できる[11]。

図 6 (a) SOTB / (b) バルクのトランジスタ構造

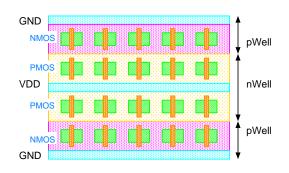

#### 3.2 Double Height Cell 構造

冗長化 FF を設計する際に使用した DHC (Double Height Cell) 構造を図 7 に示す。通常使用されるのは SHC (Single Height Cell) 構造であるが、冗長化 FF のように多くのトランジスタを SHC で配置するとラッチ間の配線を行うことが困難になるためにセル内に占めるトランジスタ配置領域を効率良く拡張できる方法としてよく用いられる DHC 構造を適用した。DHC 構造にすることで配線の簡略化するだけでなく、pWellを分離した構造を取ることで、MCU の発生率を下げることができる。正孔の移動度より電子の移動度の方が高いため拡散距離が長く、拡散領域に取り込まれやすいからである。

図7 ダブルハイトセル構造

# 3.3 単一粒子による多ビットエラーを考慮したレイアウト 構造

冗長化 FF において最も考慮すべき問題が MCU (Multiple Cell Upset) である。MCU とは単一の粒子により複数のセルが反転するエラーのことである。MCU の発生原理として、寄生バイポーラ効果と電荷共有、連続衝突が挙げられるが、これらの現象は同時に反転するとソフトエラーを引き起こすラッチやノードの距離を空けることで解消できる。本研究でも全ての冗長化 FF に対して MCU を考慮したレイアウト構造を用いている。例として BCDMRFF のレイアウト構造を図 8 に示す。BCDMRFF は 2 つのラッチと Keeper で値を保持しているため、面積が変わらない範囲でできるだけ離れるような構造にした。

| Slave  | Master | CLK | 2C-element   |

|--------|--------|-----|--------------|

| Latch0 | Latch0 |     | +Keeper (SL) |

| Master | Slave  | CLK | 2C-element   |

| Latch1 | Latch1 |     | +Keeper (ML) |

図 8 レイアウト構造を工夫した BCDMRFF。 "0" が上部のラッチ。 "1" が下部のラッチ。

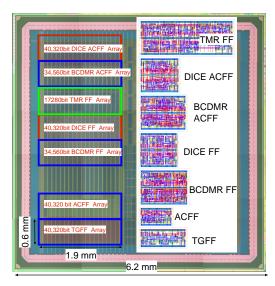

#### 3.4 テストチップの概要

本研究に用いたテストチップとレイアウトパターンを図9に示す。テストチップは65nm SOTBとバルクプロセスで設計を行った。バルクとSOTBによるFFのソフトエラー耐性を実測・評価できるように、同様のレイアウトで同じ回路を有するテストチップをそれぞれ作成した。利用したプロセスでは、BOX層を追加する層を排除することでバルクチップの製造を委託した。

テストチップには TGFF, ACFF, TMRFF, BCDMRFF, BCDMRACFF, DICEFF, DICEACFF の 7 種類の FF アレイを搭載した。各 FF の搭載ビット数は図 9 に示す。TMRFFと BCDMR 構造は面積の都合上他の回路より少ない 17,280bit と 34,560bit であり、それ以外は全て 40,320bit 搭載している。

図 9 テストチップの構造

#### 3.5 非冗長化 FF および冗長化 FF の性能比較

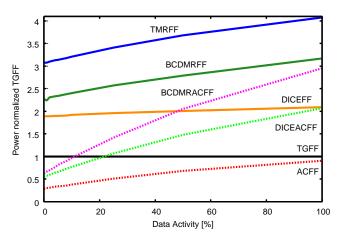

$65 \mathrm{nm}$  プロセスで設計した各 FF のトランジスタ数、面積、遅延時間、消費電力について TGFF を基準として比較した結果を表 1 に示す。活性化率  $\alpha=0\%$  - 100%までの消費電力の比較は図 10 に示す。電源電圧は  $1.2\mathrm{V}$  として Spice シミュレーションを行った。

冗長化 FF はトランジスタ数を追加する必要があるため、面積オーバーヘッドが非常に大きい。特に本研究で設計した TMRFF は Voter も三重化したために TGFF の 5.2 倍もの面積 を有する。それに比べて BCMDR 構造では 2.4-2.5 倍、DICE 構造では2.0-2.1 倍と小面積で設計することができる。

消費電力に関してはローカルクロックバッファを排除した ACFF、BCDMRACFF、DICEACFF は低活性化率領域において TGFF を下回った。活性化率は一般的に 5-15% なので、 $\alpha$ =10%で比較すると、BCDMRACFF の消費電力は従来の BCDMRFF の 40%程度に抑えることができる。DICEACFF の消費電力は従来の DICEFF の 40%程度に抑えることができる。

この結果より ACFF を基にした冗長化 FF は従来の冗長化 FF とほぼ同じ面積で、遅延時間、消費電力において高性能であることを示した。

表 1 各 FF の面積・遅延時間・消費電力. (TGFF で規格化)

|           |         |      |      | 消費電力          |                |

|-----------|---------|------|------|---------------|----------------|

| FF        | トランジスタ数 | 面積   | 遅延   | $\alpha$ =10% | $\alpha$ =100% |

| TGFF      | 28      | 1.00 | 1.00 | 1.00          | 1.00           |

| ACFF      | 24      | 0.85 | 0.49 | 0.38          | 0.91           |

| TMRFF     | 126     | 5.20 | 1.52 | 3.21          | 4.08           |

| BCDMRFF   | 72      | 2.50 | 1.75 | 2.40          | 3.17           |

| BCDMRACFF | 72      | 2.40 | 1.15 | 0.97          | 2.95           |

| DICEFF    | 56      | 2.00 | 1.29 | 1.92          | 2.09           |

| DICEACFF  | 48      | 2.10 | 0.86 | 0.77          | 2.07           |

図 10 各 FF の活性化率 vs 消費電力 (TGFF で規格化)

# 4. 重イオン照射試験の実験方法と実測結果

本節では提案した冗長化 FF のソフトエラー耐性を評価する ために行った重イオン照射試験の実験方法と実験結果について 述べる。

# 4.1 実験方法

本研究では、JAEA 高崎量子研究所 (TIARA:Takasaki Ion accelerators for Advanced Radiation Application) で重イオン照射試験を行った。重イオンのエネルギーは空気により大きく減衰するので、実験は真空で行う必要がある。そのためチャンバー内にテストチップを固定し、真空状態にして重イオン照射を行った。TIARA では表 2 に示すように 5 種類のイオンが使用可能であるが、使用するイオンを交換するときに時間が

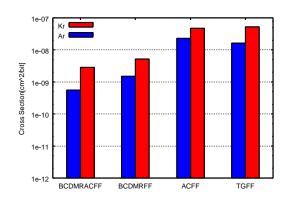

図 11 バルクプロセスにおける BCDMR 構造と非冗長化 FF の Cross-Section

かかるため、本研究では 2 種類 (Kr, Ar) のイオンのみを使用した。

測定条件について示す。テストチップに対して直角方向からのみ重イオンを照射し、電源電圧を標準電圧である  $1.2\mathrm{V}$  とした。入力するデータ及びクロックは  $(\mathrm{Data},\,\mathrm{CLK})=(0,0),$   $(0,1),\,(1,0),\,(1,1)$  の条件について測定した。測定回数は各条件につき 1 回ずつである。

重イオン照射試験においてソフトエラー率の比較を行う場合は衝突断面積 (CS (Cross Section)) と呼ばれる単位を用いる。衝突断面積とは粒子が通過するとソフトエラーを引き起こす面積のことであり、式 (1) で表される。Cross Section に単位面積当たりの照射粒子数とビット数をかけることでエラー数となる。 $N_{\rm error}$  が重イオン照射により発生したエラー数、 $N_{\rm ion}$  が単位面積にあたりに照射されるイオン総数、 $N_{\rm FF}$  が FF のビット数である。

$$CS[cm^{2}/bit] = \frac{N_{error}}{N_{ion} \times N_{FF}}$$

(1)

表 2 TIARA にて照射可能な重イオン粒子. 本研究で用いた粒子はAr, Kr のみである.

| 重イオン | Energy[MeV] | $ m LET[MeV/(cm^2/mg)]$ | Range[um] |

|------|-------------|-------------------------|-----------|

| N    | 56          | 3.4                     | 49.2      |

| Ne   | 75          | 6.6                     | 39.0      |

| Ar   | 150         | 15.8                    | 36.1      |

| Kr   | 322         | 40.3                    | 37.3      |

| Xe   | 454         | 64.0                    | 34.6      |

#### 4.2 実測結果

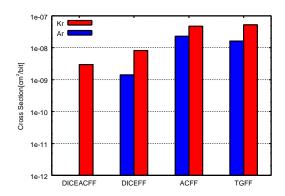

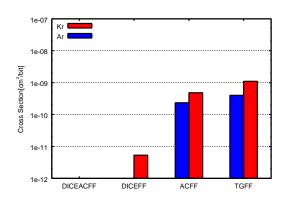

バルクプロセスにおいて BCDMR 構造および DICE 構造と非冗長化 FF を比較した結果をそれぞれ図 11 と図 12 に示す。各 FF の Cross Section は測定した 4 つの条件の平均値である。BCDMR 構造や DICE 構造を適用した冗長化 FF は非冗長化 FF よりも Cross Section が減少し、ソフトエラー耐性が向上した。LET = 40 MeV/(cm²/mg) の Kr を照射した場合では BCDMR 構造のソフトエラー耐性は TGFF の 10-20 倍程度向上し、DICE 構造のソフトエラー耐性は TGFF の 7-17 倍程度向上した。どちらの構造も ACFF に冗長化を施した回路

図 12 バルクプロセスにおける DICE 構造と非冗長化 FF の Cross-Section

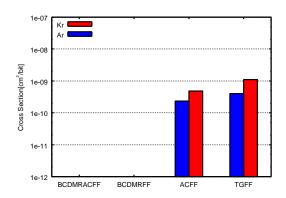

図 13 SOTB における BCDMR 構造と非冗長化 FF の Cross-Section

図 14 SOTB における BCDMR 構造と非冗長化 FF の Cross-Section

(BCDMRACFF, DICEACFF) のほうが高いソフトエラー耐性を示したが、バルクプロセスかつ高 LET の重イオン照射ではレイアウト構造を工夫しても MCU の影響が大きく、BCDMR構造や DICE 構造でも多くのソフトエラーが観測された。

SOTB において BCDMR 構造および DICE 構造と非冗長化 FF を比較した結果をそれぞれ図 13 と図 14 に示す。各 FF の Cross Section は測定した 4 つの条件の平均値である。Kr を照 射した時の TGFF の Cross-Section は  $1.11 \times 10^{-9}$  cm²/bit であったため、バルクプロセスの BCDMR 構造および DICE 構造よりも高いソフトエラー耐性を示した。SOTB は SOI 層と基板が BOX 層で分離されているために基板電位変動や電荷共有の影響を受けないからである。同様の理由で、高信頼性の BCDMR 構造や DICE 構造と SOTB を組み合わせることで 高 LET の重イオンである Kr でもソフトエラーがほとんど起こ

らない冗長化 FF を実現することができた。

#### 5. 結 論

本稿では高信頼性回路である BCDMR 構造および DICE 構造に低消費電力フリップフロップである ACFF を組み合わせた BCDMRACFF と DICEACFF を含む計 6 種類の非冗長化 FF および冗長化 FF の設計・評価を行った。

BCDMRACFF および DICEACFF は従来の BCDMR 構造 や DICE 構造と同程度の面積を保ちつつ、低活性化率  $\alpha$ =10%では従来の BCDMRFF や DICEFF の 40%程度に抑えるなど遅延時間・消費電力において高い性能を実現した。

65nm バルクと SOTB プロセスにてテストチップを試作し、重イオン照射試験を行った。バルクプロセスでは BCDMRACFF のソフトエラー耐性は非冗長化 FF である TGFF の約 20 倍かつ従来の BCDMRFF の約 2 倍であった。また、DICEACFF のソフトエラー耐性は TGFF の約 17 倍かつ従来の DICEFF の約 2.5 倍であった。しかし、レイアウト構造を工夫しても高 LET 環境では、MCU の影響が大きく、冗長化を施しても多くのエラーが観測された。SOTB では BCDMR 構造も DICE 構造もソフトエラーが一つしか発生せず、高 LET である Kr でも非常に高いソフトエラー耐性を示した。これにより宇宙空間などの高 LET 環境において高信頼性を実現するには SOTB とBCDMR 構造または DICE 構造を組み合わせるべきである。

今後は、宇宙空間での仕様なども視野に入れて直角照射のみならず重イオンの角度依存性等々を測定していく予定である。

#### 謝 辞

本研究は JSPS 科研費 15H02677, 26889037, STARC 共同 研究の助成を受けて実施したものである。また、東京大学大規 模集積システム設計教育研究センターを通し、シノプシス株式 会社,日本ケイデンス株式会社,メンター株式会社の協力で行われたものである。

#### 文 献

- N. Seifert, P. Slankard, M. Kirsch, B. Narasimham, V. Zia,

C. Brookreson, A. Vo, S. Mitra, B. Gill, and J. Maiz,

"Radiation-Induced Soft Error Rates of Advanced CMOS

Bulk Devices", Proc. Int. Rel. Phys. Symp., (2006), pp. 217–225.

- [2] "戸坂義春", ""知っておきたいソフト・エラーの実態"", "日経エレクトロニクス", 2005 年 7 月 24 日号, (2005).

- [3] J. Wilkinson and S. Hareland, "A cautionary tale of soft errors induced by SRAM pack-aging materials", *IEEE Transaction on Device and Materials Reliability*, Vol. 5, (2005), pp. 428–433.

- [4] DG Mavis and PH Eaton, "Soft error rate mitigation techniques for modern microcircuits", Proc. Int. Rel. Phys. Symp., (2002), pp. 216–225.

- [5] D. Krueger, E. Francom, and J. Langsdorf, "Circuit design for voltage scaling and SER immunity on a quad-core Itanium processor", ISSCC, (2008), pp. 94–95.

- [6] M. Zhang, S. Mitra, T. M. Mak, N. Seifert, N. J. Wang, Q. Shi, K. S. Kim, N. R. Shanbhag, and S. J. Patel, "Sequential Element Design with Built-In Soft Error Resilience", IEEE Trans. VLSI Sys., Vol. 14, No. 12, pp. 1368–1378, (2006).

- [7]~ K. T. Chen, T. Fujita, H. Hara, and M. Hamada, "A 77%

- energy-saving 22-transistor single-phase-clocking D-flip-flop with adaptive-coupling configuration in 40nm CMOS", *ISSCC*, (2011), pp. 338–340.

- [8] J. Furuta, C. Hamanaka, K. Kobayashi, and H. Onodera, "A 65nm Bistable Cross-coupled Dual Modular Redundancy Flip-FlopCapable of Protecting Soft Errors on the C-element", ISSCC, (2010), pp. 123–124.

- [9] C. Hamanaka, R. Yamamoto, J. Furuta, K. Kobayashi, and H. Onodera, "Variation-Tolerance of a 65-nm Error-Hardened Dual-Modular-Redundancy Flip-Flop Measured by Shift-Register-Based Monitor Structures", *IEICE Trans.*, (2011), pp. 2669–2675.

- [10] J. Furuta, E. Sonezaki, and K. Kobayashi, "Radiation hardness evaluations of 65nm fully depleted silicon on insulator and bulk processes by measuring single event transient pulse widths and single event upset rates", JJAP, (2015), pp. 04DC15-1-6.

- [11] D. Kobayashi, K. Hirose, H. Ikeda, and H. Saito, "Radiation-induced pulse noise in SOI CMOS logic", Int'l Symposium on Advanced Semiconductor-on-insulator Technology and Related Physics (in 219th ECS Meeting), (2011).