# $\alpha$ 線照射による 65 nm バルクプロセスにおける PMOS 及び NMOS トランジスタの SEU 感度

吉田 圭汰<sup>†</sup> 中島 隆一<sup>†</sup> 杉谷昇太郎<sup>†</sup> 伊藤 貴史<sup>†</sup> 古田 潤<sup>†</sup> 小林 和淑<sup>†</sup>

†京都工芸繊維大学

**あらまし** 本稿では、PMOS 及び NMOS トランジスタを独立させた Single Event Upsets (SEU) 感度の測定手法を検討した。65 nm バルクプロセスで設計した測定回路を用いて  $\alpha$  線照射実験を行ったところ、PMOS トランジスタの SEU 感度は NMOS トランジスタの約 1/50 であった.拡散層の面積とエラー率は単純な比例関係ではないことがわかった.拡散層と shallow trench isolation (STI) の距離が近いほど,放射線により発生する電荷の収集が妨げられることをデバイスシミュレーションを用いて確認した.

キーワード ソフトエラー, Single Event Upsets, 信頼性, デバイスシミュレーション

## Evaluation of SEU Sensitivity by Alpha-Particle on PMOS and NMOS Transistors in a 65 nm Bulk Process

Keita YOSHIDA $^\dagger$ , Ryuichi NAKAJIMA $^\dagger$ , Shotaro SUGITANI $^\dagger$ , Takafumi ITO $^\dagger$ , Jun FURUTA $^\dagger$ , and Kazutoshi KOBAYASHI $^\dagger$

† Kyoto Institute of Technology

**Abstract** We investigate a method to measure the Single Event Upsets (SEU) sensitivity individually for PMOS and NMOS transistors. We performed  $\alpha$ -particle irradiation to a circuit fabricated in a 65 nm bulk process, . The SEU sensitivity of PMOS transistors is approximately 1/50 of that of NMOS transistors. Additionally, we investigated SEU rates by the drain area. The relationship between the area and SEU rates does not follow a linear function. We consider this phenomenon due to the proximity of the drain area to shallow trench isolation (STI), which prevents charge collection by a radiation strike.

**Key words** Soft error, Single Event Upsets, Reliability, Device simulation,

## 1. まえがき

放射線に起因するソフトエラーなどの信頼性の問題は、技術の微細化によってより深刻になっている。ソフトエラーとは、放射線の衝突により、フリップフロップや SRAM などの記憶素子の保持値が反転するという一時的な故障のことである。

ソフトエラーの対策手法として回路の冗長化があり、dual interlocked storage cell (DICE) [2] [3] のような冗長回路が多数提案されている。しかし、これらの冗長回路は標準の回路に比べてトランジスタ数が大幅に増加し、性能のオーバーヘッドが大きくなる。そのため、冗長化に依らない対策が必要となる。

SEU 感度は拡散領域の面積によって左右される [4]. ソフトエラーに脆弱なノードの臨界電荷量 ( $Q_{crit}$ ) を増加させることで、ソフトエラー耐性を向上させる手法も提案されている [5] [6]. これら 2 つの要素とソフトエラー耐性の関係を調査すること

が、冗長化に依らない耐ソフトエラー回路の設計において重要 となる.

本稿では、PMOS 及び NMOS トランジスタを独立させた SEU 感度の測定手法を検討した.測定回路を  $65~\mathrm{nm}$  バルクプロセスで設計し、 $\alpha$  線照射実験により PMOS 及び NMOS トランジスタの SEU 感度を評価した.脆弱箇所の拡散領域の面積を変更した回路と、 $Q_{\mathrm{crit}}$  を変更した回路を設計し、これら 2 つの要素と SEU 感度の関係を調査した.

## 2. ソフトエラー

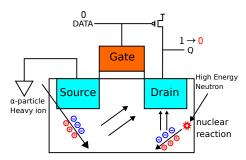

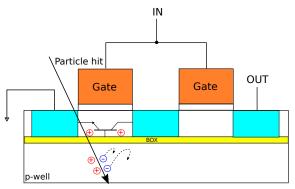

ソフトエラーは放射線起因の一時的故障である.集積回路の微細化により動作電圧が低くなり保持できる電荷量が減少し,ソフトエラーが顕在化している.ソフトエラーの発生原理を図1に示す.放射線が集積回路に突入すると電子正孔対が生じる.発生した電荷が拡散層に収集されることで,出力電圧

図 1: ソフトエラー発生原理. 放射線の突入により発生した電荷が拡散層に収集され、出力が反転するとソフトエラーとなる.

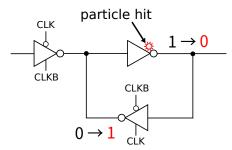

図 2: SEU 発生原理.

が一時的に変動し回路の保持値が反転する。この現象をソフトエラーと呼ぶ [8]. 電子の移動度は正孔に比べて大きいため、NMOS の方がソフトエラーを引き起こしやすい [7]. 地上では  $\alpha$  粒子,中性子,宇宙では重イオンなどが主な原因となっている [9] [10] [11]. ソフトエラーは放射線が当たる場所によって 2 種類に分類できる。組み合わせ回路内で発生する Single Event Transients (SET) と,記憶素子内で発生する Single Event Upsets (SEU) である。本稿では主に SEU について取り扱う.

#### 2.1 SEU (Single Event Upset)

SEU の発生機構を図 2 に示す. ラッチを構成するインバータに荷電粒子が衝突して電子正孔対が生じると, 出力が反転してから元の値に戻るまでの時間幅を持ったパルス (SET パルス)が発生する. 反転が元に戻るまでに次段のトライステートインバータに取り込まれると保持地が完全に反転する.

## 2.2 臨界電荷量 $Q_{\rm crit}$

保持値の反転に必要な最小の電荷量を臨界電荷量 ( $Q_{\rm crit}$ ) と呼ぶ、微細化が進むにつれて電源電圧,トランジスタのゲート容量が減少しているため  $Q_{\rm crit}$  は減少している.

### 3. 測定用回路

#### 3.1 先行研究の測定手法

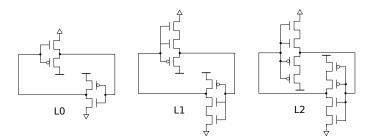

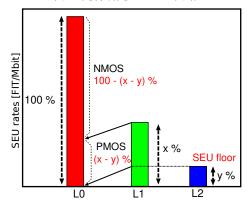

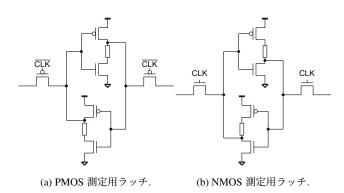

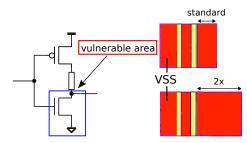

先行研究では,スタック構造を用いた SEU 感度の測定手法が提案されている [7]. これは図 3 に示す 3 種類のラッチを用い,図 4 のように発生するエラーの差を取ることで PMOS 及び NMOS トランジスタの SEU 感度を比較するという手法である.しかしこれらのラッチ回路は負荷容量が異なり, $Q_{\rm crit}$  も異なる.この手法はスタック構造を用いることができる FDSOIプロセス (図 5) においてのみ有効であり,バルクプロセスでは用いることができない.

図 3: 先行研究のラッチ回路

図 4: 先行研究における SEU 感度測定手法

図 5: FDSOI プロセスにおけるスタック構造. 片方のトランジスタが導通しても出力は反転しない.

## 3.2 提案手法

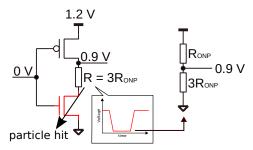

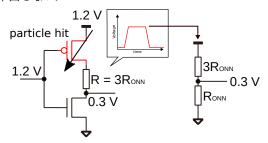

本研究ではトランジスタ間に抵抗を組み込んだインバータを用いる。図 6,7 に PMOS 及び NMOS トランジスタの SEU 感度測定用の構造をそれぞれ示す。抵抗値は測定したいトランジスタのオン抵抗の 3 倍に設定した。3 倍にすることで,分離させたいトランジスタでパルスが発生した場合でも,分圧により出力が中間電位  $(0.6\,\mathrm{V})$  を超えないため,エラーとならない.これにより,PMOS および NMOS トランジスタの SEU 感度を個別に測定することができる.このインバータを用いて,図 8 のようなラッチ回路を構成した.それぞれの出力部には,測定したいタイプのトランジスタのみが接続されている.

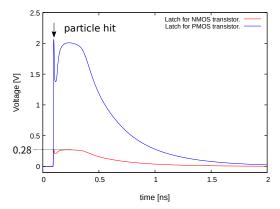

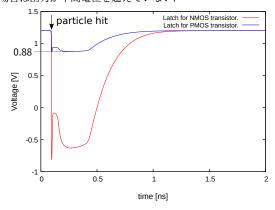

トランジスタを独立させることでソフトエラーが分離できることを、TCAD を用いたデバイスシミュレーションで確認した。衝突する放射線のエネルギーに関わらずエラーが分離できることを示すため、Linear Energy Transfer (LET) =  $60 \text{ MeV-cm}^2/\text{mg}$ を持つ重イオンを照射した。LET とは、荷電粒子が単位距離を通過する際に物質に与えるエネルギーのことである。つまり、

図 6: PMOSトランジスタの SEU 感度測定用の回路構造. NMOSトランジスタでパルスが発生した場合でも,出力電位は中間電位を下回らない.

図 7: NMOSトランジスタの SEU 感度測定用の回路構造. PMOSトランジスタでパルスが発生した場合でも,出力電位は中間電位を超えない.

図8:考案した測定用ラッチ.

荷電粒子が通過時に生成する電荷量と比例関係にあり、LET の高い粒子はソフトエラーを引き起こしやすい. 重イオンを当てた際の出力波形を図9に示す. 独立させたトランジスタから発生するパルスは抵抗により分圧され、出力は反転していない.

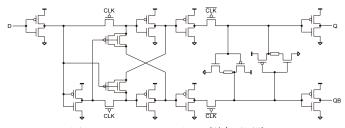

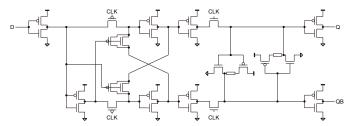

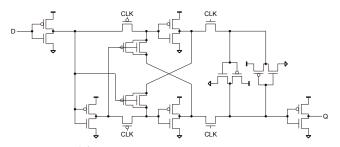

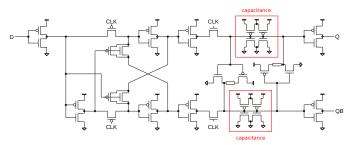

設計したフリップフロップを図 10,、11 に示す.元となるフリップフロップは図 12 に示す Adaptive Coupling FF (ACFF) [12] であり,この回路のセカンダリラッチを測定用ラッチに置き換えた.ACFF は,低電力動作を目的とした回路であり,放射線耐性は無い.ACFF の回路構造を選んだのは,脆弱箇所に接続される MOSFET を測定したい型のみにできるためである.測定回路のラッチ間には値の書き換えをしやすくするためにインバータを追加している.出力 QB を追加することで負荷容量のバランスをとり,ラッチを対称化している.そのため今回は(Q、CLK)= (0,0) 条件でのみ SEU 感度を評価した.それぞれの測定用回路において,図 13 に示すように脆弱箇所の拡散領域面積を変更した回路(標準,2 倍,4 倍)と,図 14 のように容量を追加することで  $Q_{crit}$  を変更した回路 (8,11,14fC) を設計した.

(a) それぞれのラッチ回路における PMOS トランジスタでパルスが発生した際の出力電位. NMOS トランジスタ測定用ラッチでパルスが発生した場合は出力が中間電位を超えていない.

(b) それぞれのラッチ回路における NMOS トランジスタでパルスが発生した際の出力電位. PMOS トランジスタ測定用ラッチでパルスが発生した場合は出力が中間電位を下回っていない.

図 9: デバイスシミュレーションの結果

図 10: PMOS トランジスタ測定用回路

回路シミュレーションにおいて  $Q_{\text{crit}}$  の評価に使用した電流源は,式 (1) [13] に示す単一指数モデルである.式 (1) の T はプロセスにより決まる時定数であり,本稿では 65 nm に対応する 20 ps とした [4].

$$I(t) = Q \frac{2}{T\sqrt{\pi}} \sqrt{\frac{t}{T}} \exp\left(-\frac{t}{T}\right). \tag{1}$$

#### 4. 測定結果

#### 4.1 $\alpha$ 線照射試験

設計したすべての FF をシフトレジスタとしてチップ内に実装した。各測定用回路での SEU 発生率を  $\alpha$  線照射試験で評価した。照射試験は以下の実験手順で行った。

図 11: NMOS トランジスタ測定用回路

図 12: ACFF (Adaptive Coupling FF)

図 13: 脆弱となる拡散領域の面積拡大.

図 14: 容量の追加により  $Q_{\rm crit}$  を増加させた測定用回路. 拡散層の面積は標準と同様.

- (1) α線源を設置.

- (2) FF に値を書き込む.

- (3) CLK 信号を 0 に固定..

- (4) 時間経過後、保持値を読み出す.

- (5) 保持値が変化した数をエラー数としてカウントする.

- (6) α線源を除去.

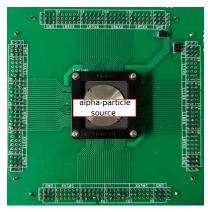

試験は図 15 のように  $\alpha$  線源をチップに置いて行う.  $\alpha$  線照 射試験は以下の条件で行った.

- (1) 使用線源: 放射能 3 MBq の <sup>241</sup>Am.

- (2) 電源電圧: 標準電圧 1.2 V.

- (3) 測定時間: 120 時間.

#### 4.2 測定結果

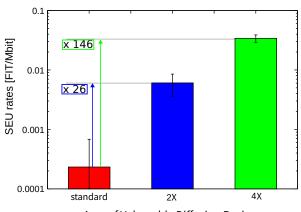

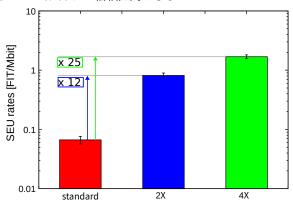

図 16, 17 に PMOS および NMOS トランジスタで発生した

図 15: α 線照射試験

エラー数を示す. 比較的エラーバーの小さい面積 4 倍の結果を比較すると、PMOS トランジスタの SEU 発生率は NMOS トランジスタの約 1/50 となった.

NMOSトランジスタにおいては、面積を2倍するとSEU発生率は12倍に、面積を4倍すると25倍に増加した.一方PMOSトランジスタは面積を2倍するとSEU発生率は26倍に、面積を4倍すると146倍に増加した.拡散領域の面積増加に伴うSEU発生率の増加率はPMOS、NMOSトランジスタで異なることがわかった.面積とSEU発生率の関係は単純な比例関係ではないことがわかった.

$Q_{\rm crit}$  を 11, 14 fC に増加させた回路では、PMOS, NMOSトランジスタ共に  $\alpha$  線によるエラーは発生しなかった.

### 4.3 考 察

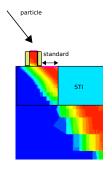

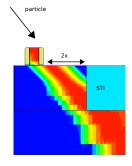

$\alpha$  線照射試験の結果より、PMOS と NMOS 共に拡散領域の面 積と SER の関係は単なる比例関係でないことがわかった. この 理由をデバイスシミュレーションを用いて解析した. 図 12 は 斜めに粒子を衝突させた際のトランジスタの断面図である. 図 中の赤い箇所に、放射線の突入により発生した電荷が分布して いる. 放射線が持つ LET 値が大きいほど, 発生する電荷量も増 加する. ソフトエラーを引き起こす放射線のエネルギーの最小 値(臨界 LET 値) は標準回路で 3.8 MeV-cm<sup>2</sup>/mg, 面積 2 倍の回 路で  $0.6 \text{ MeV-cm}^2/\text{mg}$  となった. このように、粒子により発生 した電荷はゲート-STI 間の距離が短いほど、電荷の収集が STI に妨げられやすくなる.  $\alpha$  線源から照射される  $\alpha$  粒子は、チッ プに対して垂直に入射するものだけでなく、斜めに入射するも のも存在する. このため、 $\alpha$  線照射試験において、標準回路で の SEU 発生率が小さくなったと考えられる.  $Q_{crit}$  を増加させ た回路では, $\alpha$ 線でエラーが発生しなかった.これらの回路も 同様にデバイスシミュレーションを用いて臨界 LET 値の評価 を行った. 結果を表 1 に示す. これらの結果より,  $Q_{crit}$  を増加 させた回路の臨界 LET 値は  $\alpha$  線のブラッグピーク付近の LET 値である  $1.4 \text{ MeV-cm}^2/\text{mg}$  [14] よりも大きいことがわかった.

### 5. 結 論

本稿では、PMOS 及び NMOS トランジスタを独立させた SEU 感度の測定手法を検討した. トランジスタ間に抵抗を挟んで分圧すると、分離させたいトランジスタでパルスが発生しても出

Area of Vulnerable Diffusion Region

図 16: PMOS トランジスタ測定用回路における SEU 発生率. エラーバーは 95% の信頼区間である.

Area of Vulaneable Diffusion Region

図 17: NMOS トランジスタ測定用回路における SEU 発生率. エラーバーは 95% の信頼区間である.

表 1: 各回路の臨界 LET 値

| $Q_{\rm crit}[{ m fC}]$ | 臨界 LET 值 [ MeV-cm <sup>2</sup> /mg] |

|-------------------------|-------------------------------------|

| 8 (standard)            | 0.6                                 |

| 11                      | 1.9                                 |

| 14                      | 2.5                                 |

力は中間電位を超えず、エラーにならない.TCAD によるデバイスシミュレーションでエラーが分離できることを確認し、この構造を用いた回路を  $65~\rm nm$  バルクプロセスで設計した. $\alpha$  線照射試験の結果より、面積の増加による SEU 発生率の変化は PMOS と NMOS で異なり、PMOS の SEU 発生率は NMOS の約  $1/50~\rm co$  あることがわかった.脆弱箇所の面積と SEU の関係は単純な比例関係でないことがわかった.これは、面積が小さい、つまり STI とゲートの距離が近いほど、斜めに粒子が入った場合に電荷収集が妨げられるためであると考える.

Qcrit を増加させた回路では, $\alpha$  線によるエラーは発生しなかった.デバイスシミュレーションによると,これらの回路の臨界 LET 値は  $\alpha$  線のブラッグピーク付近の LET 値である 1.4 MeV-cm²/mg よりも大きいことがわかった.よってこれらの回路は中性子など他の放射線による試験が必要である.

(a) 標準回路に粒子を照射した場合の断面図. STI との距離が近いため. 粒子の収集が STI に妨げられる.

(b) 面積 2 倍の回路に粒子を照射した場合の断面図.標準回路に比べて電荷が収集されやすい.

図 18: STI による電荷収集の妨害. 臨界 LET 値は標準回路で 3.8 MeV-cm²/mg,面積 2 倍の回路で 0.6 MeV-cm²/mg である. 面積が小さいほど,STI により電荷の収集が妨害されやすくなる.

#### 謝 辞

シミュレーションとレイアウト設計に使用した EDA ツールは、東京大学 d.lab-VDEC を通じて、日本ケイデンス・デザイン・システムズ社、日本シノプシス合同会社、シーメンス EDA ジャパン株式会社から提供されたものである.

#### 文 献

- R. Baumann, "The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction", Digest. International Electron Devices Meeting (IEDM), pp. 329-332, 2002.

- [2] T. Calin, M. Nicolaidis and R. Velazco, "Upset hardened memory design for submicron CMOS technology", IEEE Transactions on Nuclear Science (TNS), vol. 43, no. 6, pp. 2874-2878, Dec. 1996

- [3] F. Mori, M. Ebara, Y. Tsukita, J. Furuta and K. Kobayashi, "Intrinsic Vulnerability to Soft Errors and a Mitigation Technique by Layout Optimization on DICE Flip Flops in a 65-nm Bulk Process", IEEE Transactions on Nuclear Science (TNS), vol. 68, no. 8, pp. 1727-1735, Aug. 2021

- [4] P. Hazucha and C. Svensson, "Impact of CMOS technology scaling on the atmospheric neutron soft error rat", IEEE Transactions on Nuclear Science (TNS), vol. 47, no. 6, pp. 2586-2594, Dec. 2000

- [5] S. Sugitani, R. Nakajima, K. Yoshida, J. Furuta, and K. Kobayashi, "Radiation Hardened Flip-Flops with low Area, Delay and Power Overheads in a 65 nm bulk process", IEEE International Reliability Physics Symposium (IRPS), pp. P54.RE-1-P54.RE-5, March. 2023.

- [6] R. Nakajima, K. Ioki, J. Furuta, and K. Kobayashi, "Radiation Hardened Flip-Flops Minimizing Area, Power, and Delay Overheads with 1/100 Lower Alpha-SER in a 130 nm Bulk Process", IEEE International Symposium on On-Line Testing and Robust System Design, September. 2022.

- [7] K. Yamada, H. Maruoka, J. Furuta, and K. Kobayashi, "Sensitivity to Soft Errors of NMOS and PMOS Transistors Evaluated by Latches with Stacking Structures in a 65 nm FDSOI Process", IEEE International Reliability Physics Symposium(IRPS), pp. P-SE.3-1-5, March. 2018.

- [8] 戸坂 義春, "知っておきたいソフトエラーの実態", 日経エレクトロニクス, Vol. 2005 年 7 月 24 日号 (2005).

- [9] "ソフト・エラー対策, 待ったなし SRAM や論理回路が俎上に", 日経エレクトロニクス, No. 903, pp. 63-70 (2005)

- [10] S.Wen, R.Wong, M.Romain and N.Tam "Thermal neutron soft error rate for SRAMS in the 90nm-45nm technology range", Proc. Int. Reliability Phys. Symp., pp. 1036–1039 (online), April, 2010.

- [11] J.Ziegler, "Terrestrial cosmic rays, IBM Journal of Research and Development", Vol. 40, No. 1, pp. 19–39 (1996)

- [12] C. K. Teh, T. Fujita, H. Hara, and M. Hamada, "A 7722-transistor single-phase-clocking D-flip-flop with adaptive-coupling configuration in 40nm CMOS", In IEEE Int. Solid-State Circuits Conf., pages 338–340, Feb. 2011.

- [13] P. Shivakumar, M. Kistler, S. W. Keckler, D. Burger and L. Alvisi, "Modeling the effect of technology trends on the soft error rate of combinational logic", Proceedings International Conference on Dependable Systems and Networks, pp. 389-398, 2002.

- [14] Saqib A. Khan, Shi-Jie Wen, and Sanghyeong Baeg, "Assessing alphaparticle induced SEU sensitivity of flip-chip bonded SRAM using high energy irradiation", IEICE Electronics Express, Vol. 13, No. 17, pp. 20160627–20160627, 2016.