# 間欠動作を行う IoT 向けプロセッサに適した FiCC を用いた不揮発スタンダードセルメモリの実測評価

阿部 佑貴 $^{1,a}$  小林 和淑 $^{1,b}$  塩見  $^{2,c}$  越智 裕之 $^{3,d}$

概要:スタンダードセルを用いて論理合成と自動配置配線により設計するメモリをスタンダードセルメモリ (SCM) と呼ぶ。本稿では、間欠動作を行う IoT 向けプロセッサに適した FiCC (Fishbone-in-Cage Capacitor) を用いた不揮発スタンダードセルメモリ (NV-SCM) の実測について述べる。180nm プロセスを用いて、NV-SCM のレイアウト設計を行った。ビットセルの不揮発化による面積オーバーヘッドは 75% となった。実測により、動作周波数  $10 \mathrm{MHz}$  における NV-SCM の動作を確認した。データ保持時間は不揮発メモリへの書き込み時間を 0.5 秒とした場合、約 60 分となった。また、1 時間の内、5 分の動作を仮定すると、NV-SCM は SCM と比べ、消費エネルギーを 35.2%削減できることをシミュレーションにより示す。さらに不揮発プロセッサの設計に向けて、NV-SCM 用ビットセルの修正に加え、不揮発プロセッサ用フリップフロップを提案した。

## Nonvolatile Standard Cell Memory Using FiCC for IoT Processors with Intermittent Operations

Yuki Abe<sup>1,a)</sup> Kazutoshi Kobayashi<sup>1,b)</sup> Jun Shiomi<sup>2,c)</sup> Hiroyuki Ochi<sup>3,d)</sup>

Abstract: A standard cell memory (SCM) is a memory designed by logic synthesis and automatic placement and routing using standard cells. In this paper, we show the measurement results of a nonvolatile standard cell memory (NV-SCM) using a Fishbone-in-Cage Capacitor (FiCC), which is suitable for IoT processors with intermittent operations. The NV-SCM was fabricated in a 180nm CMOS process technology. The area overhead due to the nonvolatility of bit cells was 75%. In measurements, we confirmed the operation of the NV-SCM at an operating frequency of 10MHz. The data retention time was about 60 minutes when the writing time to the nonvolatile memory was 0.5 seconds. Assuming 5 minutes operation time per hour, the simulation results show that the NV-SCM can reduce 35.2% of energy consumption compared to the SCM. In addition, for the design of a nonvolatile processor, we modified a bit cell for NV-SCM and proposed a flip-flop for the nonvolatile processor.

## 1. はじめに

近年, IoT (Internet of Things), 5G などの情報通信技術が著しく発展を遂げている [1], [2]. ノートパソコンやスマートフォン等のモバイルデバイスは、そのバッテリ駆動

1 京都工芸繊維大学 電子システム工学専攻

Department of Electronics, Kyoto Institute of Technology

- <sup>2</sup> 大阪大学 Osaka University

- 立命館大学 Ritsumeikan University

- a) yabe@vlsi.es.kit.ac.jp

- b) kazutoshi.kobayashi@kit.ac.jp

- c) shiomi-jun@ist.osaka-u.ac.jp

- d) ochi@cs.ritsumei.ac.jp

時間の延長のため、マイクロプロセッサ等の低消費電力化が求められている [3]. 集積回路の消費エネルギー削減の効果的な手段の一つとして、電源電圧のスケーリングが挙げられる. 文献 [4] では、電源電圧をトランジスタの閾値電圧近傍までスケーリングすることで、プロセッサのエネルギー効率を最大 4.7 倍改善したことが示されている. しかし、このような低電圧領域ではプロセスばらつきに起因する集積回路の性能ばらつきが顕著に発生し、集積回路の誤動作が問題となる [5]、[6]. 集積回路の中で 6T SRAM を代表とするオンチップメモリはプロセスばらつきに脆弱な素子である [7]、[8]、[9]. SRAM はアナログ素子が多用され

ているため, 低電圧領域において動作させることは困難で ある.

SRAM に替わるメモリとして、スタンダードセルメモリ (Standard Cell Memory: SCM) が提案された [10]. ビットセルに D ラッチや D フリップフロップが用いられ、周辺 回路はランダムロジックにより実装される. ディジタル回路のみで回路実装が行われているため、極低電圧領域における安定動作を実現することが可能である. 文献 [11] では、4kbit の SCM が 350mV の電源電圧で正常動作することが示されている. 文献 [12] では SCM に不揮発素子 MTJ (Magnetic Tunnel Junction) を適用し、不揮発化した NV (Nonvolatile)-SCM が提案されているが、メモリ作成時に追加マスクが必要となる.

本稿ではメタルフリンジキャパシタの一種である FiCC (Fishbone-in-Cage Capacitor) を用いた不揮発メモリ [13] を SCM に適用することで不揮発化した NV-SCM[14] のレイアウト設計および実測評価について述べる.

## 2. FiCC を用いた不揮発メモリ

#### 2.1 FiCC

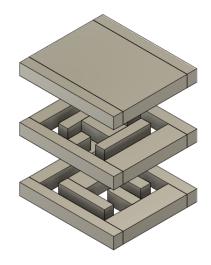

集積回路上に作ることのできるキャパシタとして, 配線 間容量を利用し、メタル配線のみで実現することができる メタルフリンジキャパシタ [15] は, 通常の CMOS プロセ スで追加マスクが不要であり,かつ理想的な線形特性を持 つキャパシタである. プロセスの微細化に伴い最小線幅や 最小配線間距離が小さくなるため、占有面積あたりの容量 が増えることから注目されている [16], [17]. しかし, メタ ルフリンジキャパシタは配線間のフリンジ容量を用いる ため、他の配線や近接して配置された他のキャパシタとの 間でクロストーク容量を生じやすく、それらを考慮したレ イアウト設計が必要である. 先行研究ではクロストーク容 量を削減するためにキャパシタごとにシールドメタルの 壁を作る方法などがとられている [18]. そのような問題を 解決するため提案されたものが FiCC (Fishbone-in-Cage Capacitor) である [19]. FiCC はキャパシタ電極を内側と 外側に分けたメタルフリンジキャパシタである. FiCC の 3D 構造を図1に示す. キャパシタの電極が内側および外側 に分かれていることがわかる. ノイズに弱い電極を内側電 極とし、GND または VDD などの電位の安定したインピー ダンスの低いネットを外側電極に接続することで, ファラ デーゲージのように内側端子をシールドする. これにより、 内側端子と他の配線または近接する他のキャパシタとのク ロストーク容量を約 1/10 にまで抑制することができる.

## 2.2 FiCC を用いた不揮発メモリ

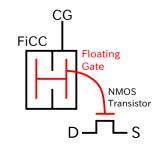

FiCC を用いた不揮発メモリはフラッシュメモリの FG (フローティングゲート) 構造に相当するものを, FiCC と NMOS を用いて実現し, CMOS 互換な不揮発メモリとし

図 1 FiCC の 3D 構造 Fig. 1 3D structure of FiCC

図 2 FiCC を用いた不揮発メモリ

Fig. 2 Nonvolatile memory using FiCC

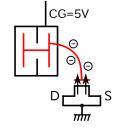

図 3 書き込み動作

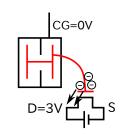

図 4 消去動作

Fig. 3 Write operation Fig. 4 Erase operation

たものである [13]. FiCC を用いた不揮発メモリを図 2 に示す. トランジスタのゲート端子とキャパシタ内側端子からなる配線は絶縁体によって外部から隔離されており, FG の役割を担う. 不揮発メモリの書き込みおよび消去動作を図 3,図 4 に示す. 書き込みは CG に 5V を印加し, トンネリングによって電子を FG に閉じ込めることで行う. 消去動作は書き込み動作とは逆のトンネリングを発生させ,電子を FG から引き抜くことで行う. 文献 [13] では, FiCC を用いた不揮発メモリ素子への書き込みにおいては 5V の書き込み電圧を 5 秒間印加すれば閾値電圧は 3V まで上昇することや, 書き込み後は一日程度のデータの保持が可能であること. 1200 回程度の書き込み, 消去動作では特性がほとんど変化しないことが示されている.

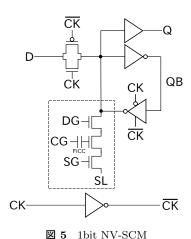

Fig. 5 1bit NV-SCM

表 1 1bit NV-SCM の動作モード **Table 1** Operation mode of 1bit NV-SCM

|       | CK | DG   | $^{\mathrm{CG}}$ | $\operatorname{SG}$ | SL   |

|-------|----|------|------------------|---------------------|------|

| ラッチ動作 | -  | 0V   | 0V               | 0V                  | 0V   |

| 退避動作  | 0V | 1.8V | 5.0V             | 0V                  | 0V   |

| 消去動作  | ı  | 0V   | 0V               | 1.8V                | 1.8V |

## 3. NV-SCM 用 D ラッチ

NV-SCM 用 D ラッチ (1bit NV-SCM) を図 5 に示す. 1bit NV-SCM は D ラッチと図中において破線で囲まれて いる不揮発部で構成される. 不揮発部は FiCC を用いた不 揮発メモリ素子を2つのNMOSで挟んだ構造となってい る. また、このような不揮発部の構造であるため、FiCCを 用いた不揮発メモリは他の不揮発メモリでも代用可能であ る. 1bit NV-SCM の動作モードは, ラッチ動作, 不揮発部 へのデータ退避動作, D ラッチへのデータ復帰動作, データ 消去動作の4つである.復帰動作を除いた、それぞれの動 作モードにおける CK, DG, CG, SG, SL ピンへの印加電圧 を**表 1** に示す. ラッチ動作時は DG, CG, SG, SL はすべて 0V とする. データの退避動作時は DG=1.8V, CG=5.0V, CK, SG, SL=0V として FiCC を用いた不揮発メモリ素子 にデータを書き込む. 書き込みによる不揮発メモリ素子の 閾値電圧上昇量は D ラッチの保持値によって決まる. デー タ消去動作時は DG, CG=0V, SG, SL=1.8V として FiCC を用いた不揮発メモリ素子のデータ消去を行う. データ復 帰動作時はまず D ラッチへ電源投入後, D ラッチに High を書き込み、その後 DG, CG, SG=1.8V, CK, SL=0V とす る. 不揮発メモリ素子の閾値電圧が 1.8V より高い場合は ラッチの保持値は変化せず、1.8Vより低い場合は、ラッチ の保持値は High から Low へと書き換えられる. このよう にしてデータの復帰を行う. そのため復帰動作では、退避 動作時における D ラッチの保持値を反転させたものが書き 戻されることになる. 復帰時における課題であるデータの 反転については、6節で詳しく述べる.

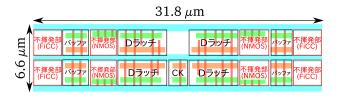

図 6 4bit NV-SCM 用 D ラッチのレイアウト Fig. 6 Layout of D-latch for 4bit NV-SCM

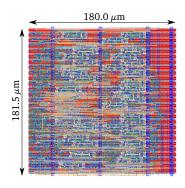

図 7 16word-8bit NV-SCM のレイアウト Fig. 7 Layout of 16word-8bit NV-SCM

## 4. NV-SCM のレイアウト設計と実測評価

#### 4.1 レイアウト設計

180nm プロセスを用いて 4bit と 16word-8bit の NV-SCM のレイアウト設計を行った. 4bit NV-SCM 用 D ラッチの レイアウトを**図 6** に示す. 4bit NV-SCM 用 D ラッチは NV-SCM 用 D ラッチを 4 つまとめて配置したものである. 論理合成および自動配置配線による NV-SCM のレイアウ ト設計において、この 4bit NV-SCM 用 D ラッチをビット セルとして用いることで、NV-SCM のレイアウト面積を 小さくすることができる. クロックは共通となっているた め,クロック用のインバータはセル全体で一つのみである. DG, CG, SG, SL はそれぞれセル内でショートしている. 4bit NV-SCM 用 D ラッチのレイアウト設計を行ったとこ ろ, 大きさは  $209.88 \mu \text{m}^2 (31.8 \mu \text{m} \times 6.6 \mu \text{m})$  となり, ビット セルの不揮発化による面積オーバーヘッドは75%となった. 4bit NV-SCM はこの 4bit NV-SCM 用 D ラッチに入力用 のバッファをつけたものである. 16word-8bit NV-SCM は 4bit NV-SCM 用 D ラッチをビットセルとして使用し、レ イアウト設計を行った. 16word-8bit MV-SCM のレイア ウトの大きさは 0.033mm<sup>2</sup>( $180.0\mu$ m× $181.5\mu$ m) となった. 16word-8bit NV-SCM のレイアウトを**図 7**に示す.

## 4.2 実測評価

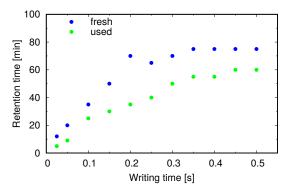

試作チップを動作周波数 10 MHz において測定し、NV-SCM の動作 (ラッチ, 退避, 復帰, 消去動作) が正常に行われていることを確認した。4 bit NV-SCM を用いてデータの退避 (書き込み) 時間と保持時間の関係を調べた。結果を図 8 に示す。FiCC を用いた不揮発メモリの劣化を確認す

図 8 FiCC を用いた不揮発メモリのデータ保持時間

Fig. 8 Retention time of nonvolatile memory using FiCC

るため、測定時に 2 つのチップを使用した. used はこれまでの測定で使用したもの、fresh は未使用のものとなっている. 書き込み時間が 0.35 秒程度までは、書き込み時間の増加に伴い、保持時間も増加している. 書き込み時間が 0.35 秒より長い場合では、書き込み時間によらず、保持時間は一定となった。 データの最大保持時間を比較すると used では 60 分、fresh では 75 分となり、used は fresh と比べてデータの保持能力が低下したことがわかる。 データの書き込みにおいて、FiCC を用いた不揮発メモリを構成する NMOSのゲート酸化膜が劣化したことが原因と考えられる。

## 5. SCM と NV-SCM の消費エネルギー比較

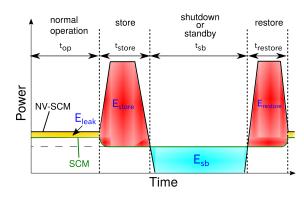

SCM と NV-SCM の消費エネルギーを比較するために HSPICE を用いてシミュレーションを行った. メモリの大 きさは 32bit, 電源電圧は 1.8V, ゲート長は 180nm, 温度は 27°C, 動作周波数は10MHz とした. SCM と NV-SCM の消 費エネルギーの関係を $\mathbf 2$  に示す. 動作時における SCM と NV-SCM の消費エネルギーの差を Eleak とする. NV-SCM は待機時に、電源を落とせるので、消費エネルギーはゼロと みなせる. そのため、 待機時において NV-SCM は SCM が 消費する分のエネルギーを削減できる. NV-SCM が削減で きる消費エネルギーを Esb とする. NV-SCM は SCM と異 なり、待機時に電源を落とすため、再度動作を開始するとき にエネルギーを消費する. そのため, Eleak + Estore + Erestore ≦ E<sub>sb</sub> となるために待機時間 (BET: Break Even Time) が 必要となる. E<sub>store</sub>, E<sub>restore</sub> はそれぞれデータの退避, 復帰 時の消費エネルギーであり、動作、待機時間と比べ、退避、 復帰時間が非常に短いため、ゼロとみなすことができる.

32bit の SCM と NV-SCM のシミュレーション結果を用いて、256word×32bit の SCM と NV-SCM の消費電力を導出する. 動作時において、同時に動作するのは 32bit とし、残りの bit は待機状態とする.256word×32bit の SCM と NV-SCM の消費電力を表 2 に示す.この結果から BET と削減エネルギーの導出を行う.まず BET を求める.NV-SCM と SCM の動作時の消費電力の差は  $0.55\mu$ W である.動作時間 1s あたりに必要な電源 OFF 時間は

**図 9** SCM と NV-SCM の消費エネルギーの関係

Fig. 9 Energy consumption diagram of SCM and NV-SCM

表 2 256word×32bit の SCM と NV-SCM の消費電力 Table 2 Power consumption of 256word-32bit SCM and NV-SCM

|        | 動作時           | 待機時           |

|--------|---------------|---------------|

| SCM    | $13.50 \mu W$ | $0.745 \mu W$ |

| NV-SCM | $14.05 \mu W$ | -             |

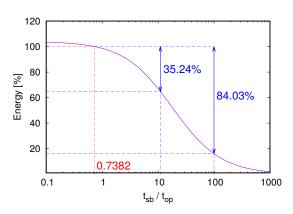

図 10 待機・動作時間の比率と削減エネルギーの関係

${\bf Fig.~10~~} {\bf Relationship~~} {\bf between~~} {\bf standby/operation~~} {\bf time~~} {\bf ratio} \\ {\bf and~~} {\bf energy~~} {\bf reduction~~}$

$0.55\mu W/0.745\mu W=0.7382s$  となる. 動作時間  $t_{op}$  を変数とすると BET は式 (1) の通りとなる. 次に削減エネルギーの導出を行う. 待機・動作時間の比率と削減エネルギーの関係を図 10 に示す. 1 時間の内, 5 分の動作を仮定すると, NV-SCM は SCM と比べ, 消費エネルギーを 35.24%削減することができる. 待機時間が動作時間の 100 倍の場合では, 消費エネルギーを 84.03%削減することができる.

$$BET = 0.7382 \times t_{op} \tag{1}$$

## 6. 不揮発プロセッサの設計に向けて

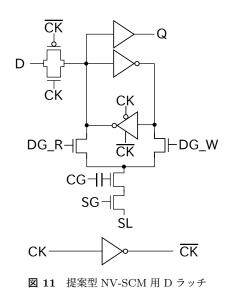

FiCC を用いた IoT 向け不揮発プロセッサの設計が今後の目標である. 不揮発プロセッサの設計には, 不揮発スタンダードセルメモリに加え, 不揮発フリップフロップが必要である. 本節では, 3 節において説明した NV-SCM 用 D ラッチの問題点を解決した, 新たな NV-SCM 用 D ラッチと, 不揮発プロセッサ用フリップフロップについて述べる.

Fig. 11 Proposed D-Latch for NV-SCM

表 3 提案型 NV-SCM 用 D ラッチの動作モード **Table 3** Operation mode of proposed D-Latch for NV-SCM

|       | CK | DG_W | DG_R | $^{\mathrm{CG}}$ | $_{ m SG}$ | SL   |

|-------|----|------|------|------------------|------------|------|

| ラッチ動作 | -  | 0V   | 0V   | 0V               | 0V         | 0V   |

| 退避動作  | 0V | 1.8V | 0V   | 5.0V             | 0V         | 0V   |

| 消去動作  | -  | 0V   | 0V   | 0V               | 1.8V       | 1.8V |

#### 6.1 提案型 NV-SCM 用 D ラッチ

3節で説明した NV-SCM 用 D ラッチを従来型 NV-SCM 用 D ラッチと呼ぶこととする. 従来型 NV-SCM 用 D ラッチには復帰時にデータの反転が生じるという課題がある. データの復帰時にラッチに High か Low のデータのどちらが書き戻されるかは, 退避時におけるラッチの保持値が関係する. 退避時におけるラッチの保持値が High の場合, 退避動作により FiCC を用いた不揮発メモリの閾値電圧は変化しない. 一方, 退避時におけるラッチの保持値が Low の場合, 退避動作により, メモリの閾値電圧が上昇する. そのため復帰動作により, 前者では Low が, 後者では High がラッチに書き戻されることになる. よって従来型 NV-SCM 用 D ラッチには復帰時にデータの反転が生じる.

提案型 NV-SCM 用 D ラッチを図 11 に示す. 従来型と 異なり, DG-W, DG-R を設けることで, データの退避と復 帰動作時においてラッチと不揮発部との経路を切り替える ことができる. 提案型 NV-SCM 用 D ラッチの動作モード は, ラッチ動作, 不揮発部へのデータ退避動作, D ラッチへ のデータ復帰動作, データ消去動作の 4 つである. 復帰動 作を除いた, それぞれの動作モードにおける CK, DG-W, DG-R, CG, SG, SL ピンへの印加電圧を表 3 に示す. ラッ チ動作時は DG-W, DG-R, CG, SG, SL はすべて 0V とす る. データの退避動作時は DG-W=1.8V, CG=5.0V, CK, DG-R, SG, SL=0V として FiCC を用いた不揮発メモリ素 子にデータを書き込む. 書き込みによる不揮発メモリ素子の 閾値電圧上昇量は D ラッチの保持値によって決まる. デー タ消去動作時は DG\_W, DG\_R, CG=0V, SG, SL=1.8V として FiCC を用いた不揮発メモリ素子のデータ消去を行う. データ復帰動作時はまず D ラッチへ電源投入後, D ラッチに High を書き込み, その後 DG\_R, CG, SG=1.8V, CK, DG\_W, SL=0V とする. 不揮発メモリ素子の閾値電圧に応じて, D ラッチへ High もしくは Low のデータの復帰が行われる. 従来型と異なり, DG\_W, DG\_R を設けることにより, 復帰時にデータの反転が生じない. 180nm プロセスにおいて, レイアウト設計を行ったところビットセルの不揮発化による面積オーバーヘッドは 74%となった. レイアウトの最適化により, 面積オーバーヘッドは従来型と同程度となった.

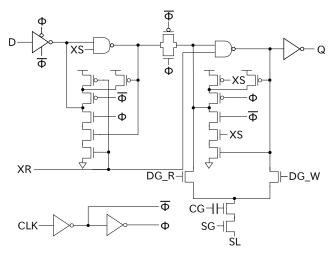

#### 6.2 不揮発プロセッサ用フリップフロップ

不揮発プロセッサ用フリップフロップを図 12 に示す. 不揮発プロセッサ用フリップフロップはフリップフロップ のセカンダリラッチに不揮発部を搭載した構造をしてい る. 不揮発部は FiCC を用いた不揮発メモリ素子と 3 つの NMOS で構成されている. DG\_W, DG\_R を設けることに より、復帰時にデータの反転が生じない. 不揮発プロセッ サ用フリップフロップの動作モードは, フリップフロップ 動作,不揮発部へのデータ退避動作,フリップフロップへ のデータ復帰動作、データ消去動作の4つである.復帰動 作を除いた、それぞれの動作モードにおける CLK, DG\_W, DG\_R, CG, SG, SL, XS, XR ピンへの印加電圧を 表 4 に示す. フリップフロップ動作時は DG\_W, DG\_R, CG, SG, SL はすべて 0V とする. データの退避動作時は DG\_W, XS, XR=1.8V, CG=5.0V, CLK, DG\_R, SG, SL=0V とし て FiCC を用いた不揮発メモリ素子にデータを書き込む. 書き込みによる不揮発メモリ素子の閾値電圧上昇量はフ リップフロップの保持値によって決まる. データ消去動作 時は DG\_W, DG\_R, CG=0V, SG, SL=1.8V として FiCC を用いた不揮発メモリ素子のデータ消去を行う. データ 復帰動作時はまずフリップフロップへ電源投入後, CLK, XS=0V としてセットをかける. その後、DG\_R、CG、SG、 XS, XR=1.8V, CLK, DG<sub>-</sub>W, SL=0V とする. 不揮発メモ リ素子の閾値電圧に応じて、フリップフロップへ High もし くは Low のデータの復帰が行われる. 180nm プロセスに おいて、レイアウト設計を行ったところフリップフロップ の不揮発化による面積オーバーヘッドは29%となった.

## 7. おわりに

本稿では、間欠動作を行う IoT 向けプロセッサに適した FiCC を用いた NV-SCM の実測について述べた.180nm プロセスを用いて、NV-SCM のレイアウト設計を行った. ビットセルの不揮発化による面積オーバーヘッドは 75%と なった.実測により、動作周波数 10MHz における NV-SCM の動作を確認した. データ保持時間は不揮発メモリへの書

図 12 不揮発プロセッサ用フリップフロップ

Fig. 12 Flip-flop for nonvolatile processor

表 4 不揮発プロセッサ用フリップフロップの動作モード **Table 4** Operation mode of flip-flop for nonvolatile processor

|            | CLK  | $DG_W$ | DG_R | $^{\mathrm{CG}}$ |

|------------|------|--------|------|------------------|

| フリップフロップ動作 | -    | 0V     | 0V   | 0V               |

| 退避動作       | 0V   | 1.8V   | 0V   | 5.0V             |

| 消去動作       | -    | 0V     | 0V   | 0V               |

|            | SG   | SL     | XS   | XR               |

| フリップフロップ動作 | 0V   | 0V     | -    | -                |

| 退避動作       | 0V   | 0V     | 1.8V | 1.8V             |

| 消去動作       | 1.8V | 1.8V   | -    | -                |

き込み時間を 0.5 秒とした場合, 約 60 分となった. また, 1 時間の内, 5 分の動作を仮定すると, NV-SCM は SCM と比べ, 消費エネルギーを 35.2%削減できることをシミュレーションにより示した. さらに不揮発プロセッサの設計に向けて, NV-SCM 用 D ラッチの修正に加え, 不揮発プロセッサ用フリップフロップを提案した.

謝辞 本研究におけるテストチップの試作は東京大学 d.lab-VDEC を通し、ローム株式会社、日本シノプシス合同会社、日本ケイデンスデザインシステム社、シーメンス EDA ジャパン株式会社の協力のもと行われたものである.

## 参考文献

- K. Shafique, B.A. Khawaja, F. Sabir, S. Qazi, and M. Mustaqim, "Internet of things (IoT) for next-generation smart systems: A review of current challenges, future trends and prospects for emerging 5G-IoT scenarios," IEEE Access, vol.8, pp.23022–23040, 2020.

- [2] K. Kaabneh and T. Ghnaimat, "A SURVEY OF QoS IN 5G NETWORK FOR IoT APPLICATIONS," International Journal, vol.8, no.6, pp.159–163, 2019.

- [3] 石橋孝一郎, "低電圧・低電力 LSI 技術の最新動向," 電子情報通信学会論文誌 C, vol.97, no.1, pp.9-16, 2014.

- [4] S. Jain, S. Khare, S. Yada, V. Ambili, P. Salihundam, S. Ramani, S. Muthukumar, M. Srinivasan, A. Kumar, S.K. Gb, et al., "A 280mV-to-1.2 V wide-operating-range IA-32 processor in 32nm CMOS," 2012 IEEE International

- Solid-State Circuits Conference, IEEE, pp.66–68, 2012.

N. Mehta and B. Amrutur, "Dynamic supply and threshold voltage scaling for CMOS digital circuits using in

- old voltage scaling for CMOS digital circuits using insitu power monitor," IEEE transactions on very large scale integration (VLSI) systems, vol.20, no.5, pp.892–901, 2011.

- [6] S. Saxena, C. Hess, H. Karbasi, A. Rossoni, S. Tonello, P. McNamara, S. Lucherini, S. Minehane, C. Dolainsky, and M. Quarantelli, "Variation in transistor performance and leakage in nanometer-scale technologies," IEEE Transactions on Electron Devices, vol.55, no.1, pp.131–144, 2007.

- [7] J. Chen, L.T. Clark, and T.-H. Chen, "An ultra-low-power memory with a subthreshold power supply voltage," IEEE Journal of Solid-State Circuits, vol.41, no.10, pp.2344–2353, 2006.

- [8] G. Chen, D. Sylvester, D. Blaauw, and T. Mudge, "Yield-driven near-threshold SRAM design," IEEE transactions on very large scale integration (VLSI) systems, vol.18, no.11, pp.1590–1598, 2009.

- [9] M. Qazi, M. Sinangil, and A. Chandrakasan, "Challenges and directions for low-voltage SRAM," IEEE design & test of computers, vol.28, no.1, pp.32–43, 2010.

- [10] P. Meinerzhagen, C. Roth, and A. Burg, "Towards generic low-power area-efficient standard cell based memory architectures," 2010 53rd IEEE International Midwest Symposium on Circuits and Systems, IEEE, pp.129–132, 2010.

- [11] O. Andersson, B. Mohammadi, P. Meinerzhagen, A. Burg, and J.N. Rodrigues, "Dual-VT 4kb sub-VT memories with < 1 pW/bit leakage in 65 nm CMOS," 2013 Proceedings of the ESSCIRC (ESSCIRC), IEEE, pp.197–200, 2013.</p>

- [12] 赤池純也,工藤優,宇佐美公良,"不揮発性素子 MTJ を適 用したスタンダードセルメモリ回路の設計と評価,"電子 情報通信学会技術研究報告, vol.116, no.93, VLD2016-25, pp.103-108, 2016.

- [13] 田中一平,宮川尚之,木村知也,今川隆司,越智裕之, "FiCC を用いた CMOS 互換な不揮発性メモリ素子の閾 値電圧特性の測定ならびに読み出し方式検討," DA シン ポジウム 2019 論文集,pp.9–14, 2019.

- [14] 阿部佑貴,小林和淑,塩見準,越智裕之,"FiCC を用いた不揮発スタンダードセルメモリ,"電子情報通信学会総合大会講演論文集,p.47,2021.

- [15] R. Aparicio and A. Hajimiri, "Capacity limits and matching properties of integrated capacitors," IEEE Journal of Solid-State Circuits, vol.37, no.3, pp.384–393, 2002

- [16] A. Matsuzawa, "Analog and RF circuits design and future devices interaction," 2012 International Electron Devices Meeting, IEEE, pp.14.3.1–14.3.4, 2012.

- [17] Q.S. Lim, A.V. Kordesch, and R.A. Keating, "Performance comparison of MIM capacitors and metal finger capacitors for analog and RF applications," 2004 RF and Microwave Conference (IEEE Cat. No. 04EX924), IEEE, pp.85–89, 2004.

- [18] D. Sandstrom, M. Varonen, M. Karkkainen, and K.A. Halonen, "W-band CMOS amplifiers achieving +10 dBm saturated output power and 7.5 dB NF," IEEE Journal of Solid-State Circuits, vol.44, no.12, pp.3403-3409, 2009.

- [19] 宮川尚之,木村知也,越智裕之, "FiCC: 高集積向け耐クロストークノイズメタルフリンジキャパシタ," 電子情報通信学会技術研究報告,vol.116,no.478,VLD2016-109,pp.43-47,2017.