# ソフトエラー耐性を高めるスタンダードセルレイアウト構造 の検討

# 京都工芸繊維大学 工芸科学研究科 張 魁元 小林 和淑

概要 近年の集積回路の素子の微細化により、ソフトエラーに代表される一過性エラーが増加し、回路の信頼性に与える影響はますます深刻になってきた。本研究ではデバイスシミュレーションを用いて数種類のスタンダードセルレイアウト構造について、その構造によるソフトエラー耐性に与える影響を比較した結果を報告する。ウェルコンタクトをセルの上下に配置する構造では、電荷共有とバイポーラ効果の抑制により、上下のセルが同時にソフトエラーの影響を受けることがほとんどなく、ソフトエラー耐性高めることができる。さらにバルク構造に加えて、薄膜 SOI 構造においても、検討を行う。

#### Analysis of Radiation-hard Standart Layout Structures

Kuiyuan Zhang, Kazutoshi Kobayashi

Dept. of Design Engineering, Graduate School of Science and Technology, Kyoto Institute of Technology

**Abstract** Recently, the soft error rates of integrated circuits is increased by process scaling. It decreases the tolerance of VLSIs. We compare the tolerance of redundant latches in several kinds of standard layout structures. When the well contacts are placed between redundant latches, the charge sharing and bipolar effects are suppressed. The redundant latches do not upset simultaneously. The tolerance of this kind structure to soft error is strong. The tolerance of SOI latches is analyzed in this paper.

## 1 序論

近年、大規模集積回路システムの信頼性は注目されている。集積回路における各種の信頼性を下げる要因もよく検討されている。集積回路の素子の微細化により、ソフトエラーに代表される一過性エラーが増加し、回路の信頼性に与える影響はますます深刻になってきた。ソフトエラーの一種の SEU (Single Event Upset) は放射線や、宇宙線などによりラッチなどの記憶素子で生じ、直接保持データを反転させる。SEUに関しては様々な測定結果や対策が報告されており、特に SRAM では ECC (Error Check Code) 回路と呼ばれる誤り訂正回路が既にサーバ等では必須の技術となっている [1,2]。他に三重化回路構造(Triple Modular Redundancy)や、DICE (Dual Interlocked storage) [3] など SEU 耐性を持つ回路構造も提案されている。

プロセススケーリングに伴い、粒子線の衝突による誘起電荷は複数のノードに収集される。複数のセルが同時に反転する MCU(Multiple Cell Upset) も大きな問題となっている [4-6]。MCU は粒子線の衝突による基板電位の上昇によって寄生バイポーラトランジスタが ON になったり、生じた電子正孔対が複数のノードに集められることによって生じるとされる。MCU はセル間の距離が短いほど発生しやすく、微細化による回路面積の減少に伴い発生率が大きく増加している。集積回路のソフトエラー耐性を高めるために、SEU 耐性だけではなくて、MCU 耐性を強くしなければならない。

本論文では、TCAD シミュレーションを用いて、数種類のレイアウト構造において、バルク構造の冗長化ラッチのソフトエラー耐性を評価する。SOI 構

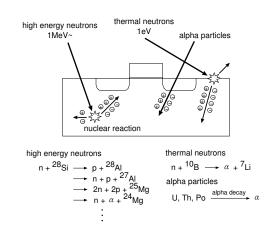

図 1: ソフトエラーを引き起こす粒子線

造を用いるラッチのソフトエラー耐性も調べる。本稿の構成を次に述べる。第2節では、ソフトエラーの発生要因について述べる。第3節では、各レイアウト構造を用いる冗長化フリップフロップのソフトエラー耐性を評価する。第4節では、薄膜 SOI 構造を用いるラッチのソフトエラー耐性について調べる。第5節では、本論文をまとめる。

# 2 ソフトエラーに関して

#### 2.1 ソフトエラーの要因

図 1 に示すように、ソフトエラーは粒子線が LSI の基板を通過、または衝突することで生じる電子正孔対によって引き起こされる。

近年の地上におけるソフトエラーの主要因は高エネルギー中性子である。しかし微細化により  $\alpha$  粒子起因のソフトエラーの割合が増加すると実測から予測している文献 [7] や、熱中性子起因のソフトエラーを報告している文献も存在しており [4]、全ての粒子に対する対策が必要とされている。

一方、宇宙空間にある人工衛星などにおいては重イオンによるソフトエラーも問題となる。重イオンは,H,D,He 以外の Li より重い元素のイオンである。 $\alpha$  粒子と同じように重イオンが MOS トランジスタの拡散領域を通過することで電子正孔対が生成され,ここで生じた電子が拡散や空乏層の電界によるドリフトにより拡散層に集められる。集められた電子によりドレインの電荷が変化し,保持値の反転が生じる。この場合には重イオンのエネルギーは LET (Linear Energy Transfer) と呼ばれる。 LET はデバイスの中に単位長における重イオン粒子が失うエネルギーのことを表し、単位は  $MeV/mg/cm^2$  である。

### 2.2 Multiple Cell Upset (MCU)

MCU とは一度の粒子の衝突で複数のラッチや SRAM が同時に反転する現象であり、MBE (Multiple Bit Error) や MNSEU (Multi-Node Single Event Upset) とも呼ばれる。発生機構として、寄生バイポーラ効果 (parasitic bipolar effect) と電荷共有 (charge sharing) が挙げられる。MCU の発生率は素子間の距離に強く依存する [8]。複数のラッチや SRAM を隣接して配置した場合は MCU が生じやすく、離すと生じにくくなる。

#### 寄生バイポーラ効果

粒子線の衝突により生じた電子正孔対のうち、基板に残留した正孔 (PMOS では電子) によって基板電位が上昇する (図 2)。基板電位の上昇によりトランジスタに寄生しているバイポーラトランジスタが ON となる。粒子線の衝突位置に隣接したトランジスタの出力も反転し、MCUとなる。ツインウェル構造に比べ、トリプルウェル構造では deep n-well により p-well が分離しているため、p-well での寄生バイポーラ効果による MCU が生じ易い [5]。

#### 電荷共有

粒子線の衝突によって生じた 2 次イオンが複数の SRAM やラッチを通過する現象である。電子正孔対が複数の SRAM 近傍で生じるため、ドリフトや拡散により複数の SRAM やラッチの保持値が反転し、MCU となる。

図 2: 寄生バイポーラ効果

## 3 ソフトエラー耐性を高めるレイ アウト構造

この節では、65nm プロセスバルク構造において、 数種類のレイアウト構造のソフトエラー耐性を評価 する。

#### 3.1 比較するレイアウト構造

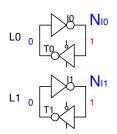

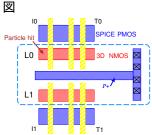

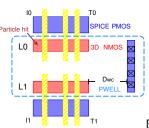

図 3 にラッチ二つが上下に並ぶ回路構造を示す。この回路構造を基づき、構築されたレイアウト構造を図 4-6 に示す。図 4 に示すように、構造 A はウェルコンタクトがラッチの間に置かれる構造である。図 5 にウェルコンタクトはラッチの横に、P+のタップがラッチの間に置かれる構造 B を示す。図 G には構造 G を示す。構造 G と異なり、構造 G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G に G

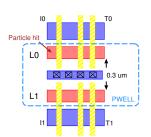

#### 3.2 シミュレーションのセットアップ

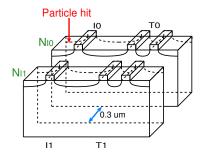

デバイスシミュレータ Sentaurus により TCAD シミュレーションを行う。重イオンモデルは垂直にインバータ I0 の NMOS に突入する。すべての NMOS は同じ P ウェル内に置く。インバータ I0 と I1 の出力ノード ( $N_{I0}$ ,  $N_{I1}$ ) の初期状態は"1"とする。そのため、冗長化ラッチが同時に反転しやすくて [9]、レイアウト構造によるソフトエラー耐性を調べるのが容易になる。図 7 に三次元 NMOS モデルを示す。その NMOS モデルは冗長化ラッチの回路図(図 3)に基づき構築され、ウェル構造はトリプルウェルである。図 7 に示すように、三次元 NMOS の間の距離は  $0.3\mu m$  である [10]。

## 3.3 レイアウト構造によるソフトエラー耐 性の分析

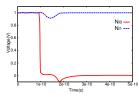

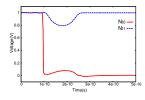

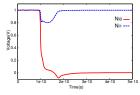

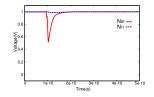

図 8 に構造 A におけるシミュレーションの結果で、ノード  $N_{10}$ 、 $N_{11}$  の状態を示す。重イオンモデル

(a) LET= $10 \text{ MeV/mg/cm}^2$  (b) LET= $20 \text{ MeV/mg/cm}^2$

図 8: レイアウト構造 A において、粒子線衝突によ 図 3: 冗長化ラッチの回路 図 4: 構造 A: ウェルコンる冗長化ラッチの出力状況

図 5: 構造 B: ウェルコ

ンタクトをラッチの横に置

き、P+のタップをラッチ

の間に置く

タクトをラッチの間に置く

図 6: 構造 C: ウェルコ く、タップなし

図 7: 冗長化ラッチの三次元モデル。重イオンモデル はラッチ L0 の NMOS の I0 に衝突する。

の LET は 10 と 20MeV/mg/cm<sup>2</sup> である。図 8(a) と 8(b) に示すように、重イオンの突入によりノード  $N_{I0}$ は反転したが、ノード  $N_{I1}$  は反転しない。構造 A に おけるラッチの間のコンタクトにより、インバータ IO で生成した誘起電荷は I1 側に到達せず、NMOS の間の電荷共有は抑制される。ラッチの基板電位も 強く固定されるため、基板電位上昇による寄生バイ ポーラ効果も抑えられる。そのため、ノード $N_{I0}$ 、 $N_{I1}$ は同時に反転してない。レイアウト構造 A における MCU は発生しない。

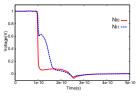

図 9 に構造 B におけるラッチの出力を示す。図 8と同じに LET は 10 と  $20 \text{MeV/mg/cm}^2$  である。図 9(a) に示すように、LET は 10 の場合ではノード  $N_{10}$ しか反転していない。構造 B におけるタップセルが 構造 A のコンタクトと同じように、電荷共有と寄生

(a) LET=10 MeV/mg/cm $^2$  (b) LET=20 MeV/mg/cm $^2$

図 9: レイアウト構造 B において、粒子線衝突によ る冗長化ラッチの出力状況

ンタクトをラッチの横に置<sub>バイポーラ</sub>効果の抑制に効果あると考えられる。し かし、LET を 20 に増やすと、ノード N<sub>IO</sub>、N<sub>I1</sub> が同 時に反転する。つまり、構造 B は高いエネルギーの 重イオンでは、二つのラッチが同時に反転する。

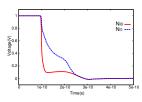

> 構造 C におけるシミュレーションの結果を図 10に示す。構造 C のウェルコンタクトはラッチの横に 置かれるため、基板電位の上昇を強く抑えることは できない。それで電荷共有と寄生バイポーラ効果に より、図 10(a) と 10(b) に示すように、LET=10 と  $20 \mathrm{MeV/mg/cm^2}$  両方の場合で、ノード  $\mathrm{N_{I0}}$ ,  $\mathrm{N_{I1}}$  が 同時に反転する。

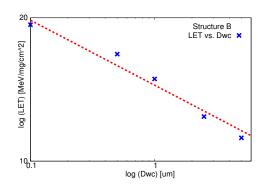

> 表 1 にレイアウト構造 A、B、C において、二つ のラッチが同時に反転する LET を示す。構造 C の ソフトエラー耐性は以上の三つのレイアウト構造の 中に一番弱い。図 11 にウェルコンタクトとラッチの 間の距離 Dwc(図 6) とラッチを反転する臨界 LET 量 の関係を示す。Dwc を離れることにより、冗長化フ リップフロップが同時に反転する臨界 LET 量がイク スポテンシャルで減る。

(a) LET= $10 \text{ MeV/mg/cm}^2$  (b) LET= $20 \text{ MeV/mg/cm}^2$

図 10: レイアウト構造 C において、粒子線衝突によ る冗長化ラッチの出力状況

表 1: レイアウト構造における臨界 LET 量

| レイアウト構造            | A  | B  | C       |

|--------------------|----|----|---------|

| $LET(MeV/mg/cm^2)$ | 55 | 13 | 図 11 参照 |

図 11: レイアウト構造 C において、臨界 LET vs. Dwc

# 4 SOI トランジスタにおけるソフ トエラー耐性

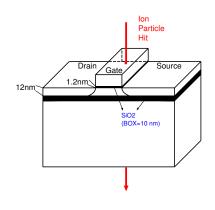

この節では、TCAD シミュレーションを用いて SOI トランジスタのエラー耐性を分析する。図 12 に SOI トランジスタの三次元モデルを示す。12nmSOI 層の下に 10 nm の BOX (埋め込み酸化膜) 層がある。BOX 層と SOI 層が共に薄い FD SOI(SOTB-Silicon on Thin BOX) 構造である [11]。この節では、図 13 の回路構造ようなラッチのソフトエラー耐性について論じ、SOI トランジスタに構築された冗長化ラッチ(図 3 に示す)のソフトエラー耐性についても述べる。

図 12: SOI トランジスタの三次元モ j デル

(a) 粒子線はドレイン部に突入する

1 0.8 LET=10 — LET=20 --- LET=50 --- LET=50

(b) 粒子線はゲート部に突入する

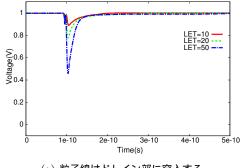

図 14: レイアウト構造 C での粒子線による SOI ラッチの出力. LET=10、20、50 MeV/mg/cm $^2$ .

## 4.1 重イオン突入位置によるソフトエラー 耐性について

SOI ラッチにおいて NMOS のドレイン部とゲート部に重イオンが衝突した場合のラッチの出力をそれぞれ図 14(a) と 14(b) に示す。重イオンモデルのLET は 10、20 と  $50 \text{MeV/mg/cm}^2$  である。重イオンは SOI トランジスタのドレイン部に突入する場合では、ドレイン部の下の BOX 層により、誘起電荷はドレインに収集されない。そのため、図 14(a) に示すように、SOI ラッチは反転しない。一方、重イオンは SOI トランジスタのゲート部に突入する場合では、ドレインとソースの間のボディ部に誘起電荷は生成し、ドレイン部に収集されるようになる。図 14(b) に示すように、LET は 10 のとき、BOX 層により少量の誘起電荷しか収集されない。しかし、LET は  $20 \text{MeV/mg/cm}^2$  に増やすと、ボディ部でより多

図 13: TCAD くの誘起電荷がドレイン部に収集されるため、SOI シミュレーショトランジスタに寄生したバイポーラトランジスタが ンに用いられる ON して、図 14(b) のようにラッチが反転する。 ラッチの回路構

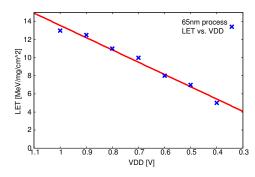

# 4.2 電源電圧スケーリングによるソフトエラー耐性

SOTBでは、SOI層が薄く、チャネル部に不純物を ドーピングしないため、ばらつきが小さく、0.4V程

Heavy Ion

度の超低電圧で動作させることができる [12]。本節では、SOI ラッチの電源電圧 VDD を 0.4V までスケーリングする場合のソフトエラー耐性について述べる。図 15 に SOI ラッチを反転させる臨界 LET 対電源電圧 VDD の関係を示す。電源電圧 VDD は 1.0V の場合では、SOI ラッチが反転する LET は  $13 \text{MeV/mg/cm}^2$ である。それに対し、、VDD を 0.4V にすると、LET が  $5 \text{MeV/mg/cm}^2$  で、SOI ラッチは反転する。電源電圧により、ラッチが反転する LET は、線形に減少することが分かった。

図 15: 65nm プロセス薄膜 SOI ラッチにおいて、VDD vs. LET

### 4.3 バルク構造と SOI 構造を用いる冗長 化ラッチのソフトエラー耐性の比較

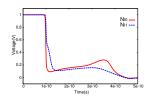

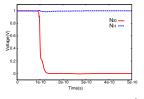

ソフトエラー耐性が一番弱いレイアウト構造 C に おいて、バルク構造とSOI構造の冗長化ラッチのソ フトエラー耐性を比較する。図16に重イオン粒子が 冗長化 SOI ラッチのゲート部に突入することによる 出力を示す。LET は  $10 \ge 20 \text{MeV/mg/cm}^2$  とする。 LET は 10MeV/mg/cm<sup>2</sup> の場合では、図 16(a) 示す ように SOI 冗長化ラッチの出力ノード N<sub>TO</sub> において エラーパルスが発生し、ノード N<sub>11</sub> におけるエラー パルスはほぼ発生しない。図 10(a) に示すシミュレー ション結果により、バルク構造では冗長化ラッチの出 カノード  $N_{I0}$ 、 $N_{I1}$  が同時に反転した。一方、LET を  $20 \mathrm{MeV/mg/cm^2}$  に増やすと、図 16(b) に示すように SOI 冗長化ラッチの出力ノード N<sub>10</sub> が反転したが、 ノードN11 は影響を受けず、反転していない。バルク 構造においては、図 10(b) の結果に示すように、ノー ド $N_{I0}$ 、 $N_{I1}$ が同時に反転する。この場合で、SOI 冗 長化ラッチの BOX 層により、ラッチの間の電荷共有 と寄生バイポーラ効果が抑制され、MCU は抑えら れる。レイアウト構造 C は MCU に弱いにも関わら ず、SOI トランジスタを用いることによって、冗長 化ラッチの MCU 耐性を高めることができる。

SOI 冗長化フリップフロップでは電荷共有とバイポーラ効果が発生しないため、レイアウト構造に関わらず、ソフトエラー耐性は大きく変わらない。

(a) LET= $10 \text{ MeV/mg/cm}^2$

(b) LET= $20 \text{ MeV/mg/cm}^2$

図 16: SOI 構造を用いる冗長化ラッチの出力. LET=10 and 20 MeV/mg/cm $^2$ .

#### 5 結論

本稿では TCAD シミュレーションを用いて、三種 類のレイアウト構造において、バルク構造の冗長化 ラッチのソフトエラー耐性を評価した。シミュレー ションの結果によると、ウェルコンタクトをラッチ の間に置く場合で、電荷共有と基板バイポーラ効果 を抑制でき、冗長化ラッチにおける MCU は発生し ていない。それに対し、ウェルコンタクトをラッチの 横に置く構造は MCU 耐性は弱いと考えられる。SOI トランジスタの BOX 層により、電荷収集メカニズ ムは抑えられ、ドレインに対する粒子線衝突ではソ フトエラーは起きない。ただし、ゲート部の直下の SOI層で正孔電子対は生成され、粒子線衝突に弱い。 電源電圧を下げることに伴い、SOI ラッチを反転す る臨界 LET 量は線形に下がる。電荷共有とバイポー ラ効果は BOX 層に抑えられるため、SOI 構造を用 いる冗長化ラッチにおける MCU は発生しない。

# 参考文献

- [1] ソフト・エラー対策,待ったなし SRAM や論理回路が俎上に,日経エレクトロニクス, No. 903, pp. 63-70 (2005).

- [2] Ando, H., Seki, K., Sakashita, S., Aihara, M., Kan, R., Imada, K., Itoh, M., Nagai, M., Tosaka, Y., Takahisa, K. et al.: "Accelerated Testing of a 90nm SPARC64V Microprocessor for Neutron SER", The Third Workshop on System Effects on Logic Soft Errors (2007).

- [3] D. Krueger, E. Francom, and J. Langsdorf. Circuit design for voltage scaling and ser immunity on a quad-core itanium processor. In ISSCC, pages 94–95, Feb. 2008.

- [4] Wen, S., Wong, R., Romain, M. and Tam, N.: "Thermal Neutron Soft Error Rate for SRAMS in the 90NM 45NM Technology Range", Reliability Physics Symposium (IRPS), 2010 IEEE International, pp. 1036-1039 (2010).

- [5] Gasiot, G., Giot, D. and Roche, P.: "Multiple Cell Upsets as the Key Contribution to the Total SER of 65 nm CMOS SRAMs and Its Dependence on Well Engineering", Nuclear Science, IEEE Transactions on, Vol. 54, No. 6, pp. 2468 –2473 (2007).

- [6] B.D. Olson, D.R. Ball, K.M. Warren, L.W. Massengill, N.F. Haddad, S.E. Doyle, and D. McMorrow. Simultaneous single event charge sharing and parasitic bipolar conduction in a highly-scaled SRAM design. In Nuclear Science, IEEE Transactions on, number 52, Issue: 6, pages 2132 2136, Dec. 2005.

- [7] Kobayashi, H., Kawamoto, N., Kase, J. and Shiraish, K.: "Alpha Particle and Neutron-induced Soft Error Rates and Scaling Trends in SRAM", Reliability Physics Symposium, 2009 IEEE International, pp. 206–211 (2009).

- [8] O.A. Amusan, A.F. Witulski, L.W. Massengill, B.L. Bhuva, P.R. Fleming, M.L. Alles, A.L. Sternberg, J. D. Black, and R. D. Schrimpf. Charge collection and charge sharing in a 130 nm cmos technology. *IEEE Trans. Nucl. Sci.*, 53(6):3253–3258, Dec. 2006.

- [9] K. Zhang, R. Yamamoto, J. Furuta, K. Kobayashi, and H. Onodera, "Parasitic bipolar effects on soft errors to prevent simultaneous flips of redundant flip-flops," IEEE International Reliability Physics Symposium, pp. 5B.2.1-5B.2.4, Apr. 2012.

- [10] K. Zhang, and K. Kobayashi Contributions of Charge Sharing and Bipolar Effects to Cause or Suppress MCUs on Redundant Latches. *IEEE International Reliability Physics Symposium*, pp. SE.5.1-SE.5.4, April 2013.

- [11] R. Tsuchiya, M. Horiuchi, S. Kimura, et al. Silicon on thin BOX: a new paradigm of the CMOSFET for lowpower high-performance application featuring wide-range back-bias control. *Proceedings IEDM 2004*, pp.631-634, Dec. 2004.

- [12] Y. Yamamoto, H. Makiyama, H. Shinohara, T. Iwamatsu, H. Oda, S. Kamohara, N. Sugii, Y. Yamaguchi, T. Mizutani and T. Hiramoto Ultralow-Voltage Operation of Silicon-on-Thin-BOX (SOTB) 2Mbit SRAM Down to 0.37 V Utilizing Adaptive Back Bias. 2013 Symposium on VLSI Technology Digest of Technical Papers, JJ2-4, 2013.