# パッケージとの接続抵抗を考慮した チップ内電源ネットワークの評価手法

西澤 真一† 小林 和淑 \$ 小野寺 秀俊 <sup>†,‡</sup>

† 京都大学大学院 情報学研究科,

§ 京都工芸繊維大学大学院 工芸科学研究科, <sup>‡</sup>JST, CREST, Japan

概要 電源の品質は回路の動作を保証する上で重要な要素である.本論文では,静的な電源ドロップの解析に用いる,電源ネットワーク評価モデルを示す.始めに,ワイヤボンディングでパッケージに封入されたチップを想定した電源モデルを作成する.チップ内部およびチップ外の電源ネットワークの抵抗成分が,チップ内の電源ドロップに与える影響について調査する.次に,実プロセスを例に電源ネットワーク内の電源ドロップ分布を取得する回路を提案する.提案回路を用いて,実測結果とシミュレーション結果の検証を行う.実測結果とシミュレーション結果は良く一致し,その誤差は最大 $0.3\,\%$ であった.

# Design Methodology of On-Chip Power Distribution Network Considering Package Parasitic Resistance

Shinichi Nishizawa<sup>†</sup>, Kazutoshi Kobayashi<sup>§</sup> and Hidetoshi Onodera<sup>†,‡</sup>

Graduate School of Informatics, Kyoto University,

<sup>§</sup>Graduate School of Science and Technology, Kyoto Institute of Technology, <sup>‡</sup>JST, CREST, Japan

Abstract Quality of power distribution network (PDN) stronglly affect to circuit operation. In this paper, we propose a PDN evaluation model which considers both on-chip and off-chip parasitic resistance. PDN is composed of both on-chip PDN and off-chip PDN. Firstly, we show how parasitic resistance of both on-chip PDN and off-chip PDN affect to the IR-drop in LSI. Simulation result shows off-chip parasitic resistance stronglly affect to both maximum IR-drop and minimum IR-drop. Secondly, we propose a test structure to measure an IR-drop map in real silicon. Measurement and simulation result have good consistency, and maximum error is 0.3 %.

### 1 序論

外部から供給される電源電圧を分配するために,LSI中には配線による電源ネットワーク (Power distribution network: PDN) が構成されている.近年の微細なプロセスでは大量のトランジスタを一つの LSI に集積することが可能であるため,LSI は大量の電力を消費する.PDN が不十分な設計では PDN 内の抵抗が大きくなり,電源ドロップ (IR-drop) に起因するタイミングエラーによって回路が誤動作する.強固な PDN を構成することで IR-drop の影響を抑えることができるが,一方で回路を設計するときに利用する信号配線や信号用 IO の資源を制限する.そのため適切な PDN の設計を行う必要がある.

PDN の評価および設計手法については,すでに多くの議論がなされている [1] [2] [3] [4]. これらは主に LSI 内部のコアエリアにおける電源ネットワークの構成手法について注目しており,コアエリアへは理想電源が接続されると仮定している.一方で,現実の LSI はパッケージに封入されるため,パッケージにおけるリードフレームの抵抗といった,LSI 外部の PDN の影響を調査する必要がある.

PDN モデルの検証のために,実際のシリコンの IRdropの評価手法についても議論がなされている.IR-dropを測定する回路は,アナログ波形を観測するものと [5],リングオシレータ (Ring oscillator: RO) 回路の発振周波数をデジタル値として観測するものがあげられる [6].アナログ波形を観測する手法は測定解像度が高いが,回路規模が大きくなり測定環境構築が難しい.RO は回路規模が小さく,実測や測定が容易であり,デジタル回路との親和性が高い.一方で RO はプロセスばらつきの影響を受けやすいため,IR-dropの絶対値を測定する事は難しい欠点がある.

本論文では、PDN の評価手法について議論する.始めに、PDN 内の抵抗の評価を行う.従来研究ではチップ内部の抵抗を考慮した設計手法が提案されていたが、チップ外部の抵抗がチップ内の電源電圧に及ぼす影響が十分考慮されていなかった.チップ外部の抵抗を考慮した PDN シミュレーションモデルを提案する.次に,提案シミュレーションモデルを利用して、チップ外部の抵抗がチップ内の電源電圧に及ぼす影響について議論を行う.最後に、実際のチップ内のIR-dropを測定する回路を提案し、その測定結果について議論する.電圧制御電流源 (Voltage controlled current source: VCCS) と RO

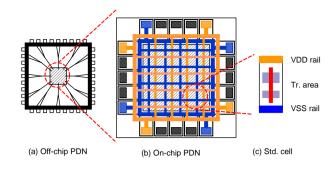

図 1: メッシュ構造を持つ PDN 模式図 . チップは QFP パッケージにワイヤボンディングされる .

回路を組み合わせる事で,実チップ内の電源電圧分布を 得る手法を提案する.また測定結果からシミュレーショ ンモデルの妥当性を検討する.

論文の構成を以下に示す.2章では,パッケージに封入された実際のチップを想定し,提案 PDN シミュレーションモデルについて述べる.3章では,2章で述べた PDN を例に,PDN のパラメータがチップ内の IR-drop に与える影響を議論する,4章では,IR-drop 測定回路 の提案を行い,シミュレーション結果と実測結果の比較 通して,シミュレーションモデルの妥当性を検証する.5章にて結論を述べる.

### 2 PDN 内の抵抗の抽出とモデル化

### 2.1 PDN の構造

本論文で想定する PDN の構造を図1に示す.QFPパッ ケージを想定し,パッケージ4辺にはリードフレームが 配置されている、パッケージ中心にはインターポーザが 設置されており,インターポーザの中心にチップが搭載 されている.リードフレームとインターポーザ,および インターポーザとチップの間は,ボンディングワイヤに よってワイヤボンディングされる構造である.インター ポーザはガラス繊維入りのエポシキ等で構成されており、 配線には金が使われている、ボンディングワイヤではな くインターポーザを利用することで,ボンディングワイ ヤの抵抗を削減し, また MCM (Multi chip package) の ように複数チップを一つのパッケージに搭載する事が可 能となる、ボンディングワイヤは、ボンディングが容易 かつ抵抗を削減するために,一般に金(Au)が使われる。 ボンディングワイヤはチップ上のパッドにボンディング され,パッドとコア領域の間は電源用 IO セルによって接 続される.電源用IO セルは内部にESD 保護ダイオード や L di/dt ノイズを削減するためにデカップリングキャ パシタを内蔵する. そのため IO セル内部の電源配線の 抵抗は無視できない値となる.コア領域の周辺には IO RING が張り巡らされており、電源 IO セル間の電位差を 緩和する働きを持つ、現在の多層配線プロセスにおける 一般的な PDN は , メッシュ構造による電源配線である .

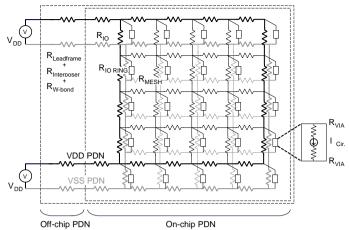

図 2: PDN シミュレーションモデル・メッシュ構造となるチップ内部 PDN に , リードフレーム , ボンディングワイヤ , インターポーザ上の配線からなるチップ外部 PDN が接続される . コアエリアには Stacked VIA を介して回路の消費電流を模す消費電流源が接続される .

メッシュ構造では縦方向と横方向の配線はそれぞれ異な る配線層で構成される.抵抗の削減と下層に設置される 信号配線の領域を確保するために,電源メッシュは厚み のある上層に設置される.メッシュの交点は VIA によっ て接続される.一般的な電源メッシュは2層構造を持つ が,一部の設計では2層以上の多層構造にする事で,抵 抗の削減を行っているものもある.電源メッシュはコア 領域外部の IO RING との交点で終端され,異なるレイ ヤーを縦貫する Stacked VIA によって接続されている. 一部のプロセスでは大量の信号配線領域を確保するため に 10 層以上の信号配線層が設置される.信号配線層が増 えるに従い Stacked VIA が長くなるため, Stacked VIA が持つ抵抗は無視できなくなる.回路を構成するスタン ダードセルは,チップのコア領域に配置される.コア領 域にはスタンダードセルの電源となる VDD と VSS 用の 電源レールが交互に配置される、一般的に電源レールは スタンダードセル内の配線領域である Metall や Metal2 といった下層のメタル層で構成される.

# 2.2 チップ外部の抵抗を考慮した PDN シミュレーションモデル

PDN にはチップ内部に構成されるものの他に,チップ外部にも存在する.チップ外部の PDN を考慮した,PDN シミュレーションモデルを図 2 に示す.PDN シミュレーションモデルは,前節にて抽出した抵抗成分による線形回路網で表現される.チップ内部の PDN はメッシュ構造である.チップ外部の PDN はリードフレーム,ボンディングワイヤ,インターポーザの配線抵抗すべてが直列に接続される.チップ外部の PDN とコアエリア

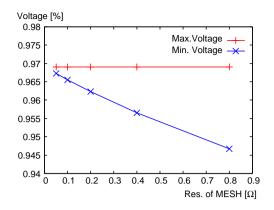

図 3: 電源メッシュの抵抗と IR-drop の関係.

は,電源 IO セルの抵抗を介して接続される.コアエリアにおける VDD と VSS の間は,Stacked VIA の抵抗を介して回路の消費電流を模す消費電流源が接続される,

# 3 PDN 中の抵抗が IR-drop に与える影響

本節では, PDN 中の抵抗が, PDN の品質に与える影 響を評価する.従来は,電源メッシュの抵抗,IO RING の抵抗の影響の評価のみが行われていた.本論文では, 上記に加え,電源 IO セルからチップ外部に存在する電 源までの PDN の抵抗を評価対象とする.そのため評価 対象は,電源メッシュ, IO RING の他に,電源 IO セル から外部電源までの抵抗,および電源 IO セルの数であ る.本論文では図2に示したLSI電源モデルを想定し 上記パラメータの変動が IR-drop 分布に与える影響を調 べる. 利用する LSI モデルのパラメータを表 1 に示す. 本モデルではメッシュベースの PDN を想定し,コアエ リアには均一な消費電流源が配置される.電源メッシュ は,コアエリア周辺において IO RING によって終端さ れる.初期状態では各辺中央に1つずつ計4つの電源IO セルが配置される、電源 IO セルからチップ外部の理想 電圧源までは,抵抗を持つPDNでもって接続されると 仮定する.以下の評価では,PDN に発生した IR-drop により低下した電源電圧 (VDD-VSS) の最大値と最小値 でもって, PDN の品質を評価する.

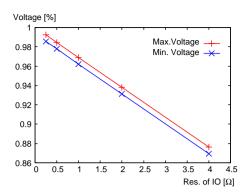

電源メッシュの抵抗が IR-drop に及ぼす影響 電源メッシュの抵抗と,IR-drop の関係を図 3 に示す.横軸は電源メッシュを構成する配線の単位メッシュあたりの抵抗を示し,縦軸はコア領域における電源電圧の最大値と最小値を示している.LSI モデルが正方形であるため,IR-drop の最大値はコアエリア中央部で観測され,IR-drop の最小値は IO RING のうち IO セルが接続された箇所にて観測された.図から,電源メッシュの抵抗を削減する事で,IR-drop の最大値の減少は線形であり,電源メッシュの抵抗値が理想的に 0 になった点で,IR-drop の最小値と

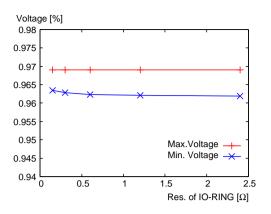

図 4: IO RING の抵抗と IR-drop の関係.

一致する、以上から、電源メッシュの抵抗は PDN における IR-drop の最大値と最小値の比を決めるパラメータである事がわかる、

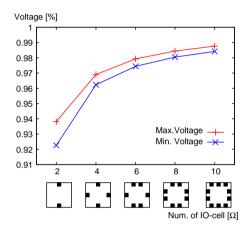

IO RING の抵抗が IR-drop に及ぼす影響 IO RING の抵抗と IR-drop の関係を図 4 に示す . 横軸は IO RING の単位 IO RING あたりの抵抗を示し , 縦軸はコア領域における電源電圧の最大値と最小値を示す . 図から , IO RING の抵抗が IR-drop 分布に及ぼす影響は小さいことがわかる . 理由として , 利用した LSI モデルにおいて ,電源 IO セルーつあたりに流れる電流量が均一である事があげられる .

IO セルあたりの抵抗が IR-drop に及ぼす影響 IO セルからパッケージ外部の理想電圧源までの PDN の抵抗と, IR-drop の関係を図 5 に示す. 横軸は IO セルからパッケージ外部までの抵抗を示し, 縦軸はコア領域における電源電圧の最大値と最小値を示す. 図から, IO セルからパッケージ外部までの抵抗は IR-drop の最大値最小値共に強く影響していることがわかる.

**IO セルの数が IR-drop** に及ぼす影響 IO **セルの数**と, IR-drop の関係を図 6 に示す. 横軸は IO セルの数を示し, 縦軸はコア領域における電源電圧の最大値と最小値

表 1: 評価に用いた PDN モデルにおける抵抗の一覧 . VDD と VSS は同一条件である .

|                | Num.                      | 補足              |

|----------------|---------------------------|-----------------|

|                | ivaii.                    | 11872           |

| メッシュ数          | $64 \times 64$            | 正方形             |

| PDN の IO 数     | 4                         | 各辺中央に配置         |

| 電源メッシュ         | $0.2 [\Omega]$            | 単位メッシュあたり       |

| IO RING        | $0.6 \left[\Omega\right]$ | 単位 IO RING あたり  |

| Stacked VIA    | $0.9 [\Omega]$            |                 |

| IO             | $1.0 \left[\Omega\right]$ | 単位 IO あたり       |

|                |                           | チップ外 PDN の抵抗も含む |

| Supply voltage | 1.0 [V]                   |                 |

| 消費電流           | 60 [mA]                   | 均一に配置           |

図 5: IO セルの抵抗と IR-drop の関係.

図 6: IO セルの数と IR-drop の関係.

を示す. 横軸下部に,各 LSI モデルにおける IO セルの配置箇所を示した. IO セルの配置にあたっては,各 IO セルを流れる電流量が一定になるように配置している. 図より, IO セルの数が増大するに従って,IR-drop が急激に回復することがわかる.

# 4 実シリコン上の IR-drop 分布の実測

## 4.1 IR-drop 測定回路

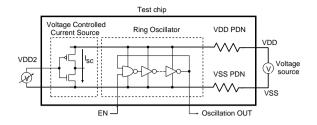

図7に提案するIR-drop 分布測定回路を示す、IR-drop 分布測定回路は、VCCS と RO 回路から構成される、VCCS はインバータのゲート電圧をチップ外部から任意に供給できる回路となっており、ゲート電圧を調節する事でショートサーキットカレントを任意に変更する事が可能である、図7では、インバータの PMOS ソースには VDD が、ゲートには VDD2 が接続されている、VDD2 の電圧を調節することで VDD と VSS に電流を流すことが可能となる、RO の電源ノードには VDD が、グランドノードには VSS が接続されている、VCCS によって VDD および VSS に電流が流れ IR-drop が発生すると、RO の発振周波数が減少する、VCCS と RO を

図 7: 提案 IR-drop 測定回路 . VCCS と RO から構成される .

用いる事で,チップ内の IR-drop 分布は以下のように測定することが可能である.

Step1: 複数の電流消費状態における RO の発振周波数の取得 VDD2 の電圧を変更することで VDD と VSS に電流を流し, RO の発振周波数の取得する. VDD2 の電圧を複数点とることで,次の Step 2 におけるフィッティングを可能にする.

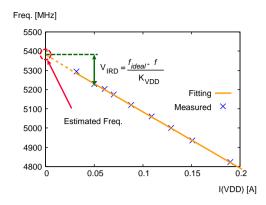

Step2: 理想条件における RO の発振周波数の推測 RO の電源電圧と発振周波数の関係は,電源電圧の変動が小さい範囲内では線形である.従って,VDD と VSS に流れる電流と RO の発振周波数の関係は,電流の変動が小さい範囲内では線形になる.X 軸に PDN に流れた電流,Y 軸に RO の発振周波数をとると,IR-drop のない理想状態における RO の発振周波数として Y 切片の値を推測することが可能になる.

Step3: IR-drop の算出 RO の発振周波数の変動要因が IR-drop によるものだと仮定すると,ある消費電流が流れる点における IR-drop 量  $V_{IRD}$  は

$$V_{IRD} = \frac{f_{ideal} - f}{K_{VDD}}, \qquad (1)$$

となる.ここで  $f_{ideal}$  は IR-drop が存在しない条件にお ける RO の発振周波数 f はある消費電流が流れている 時における RO の発振周波数 ,  $K_{VDD}$  は回路シミュレー ションによって求めた電源電圧に対する RO 発振周波数 の感度係数である.提案手法の特徴は,(1)フィッティ ング操作によってすべての RO の発振周波数のキャリブ レーションを行っていること,(2)フィッティングによっ て推測した理想的な発振周波数との差分から IR-drop を 求めている点である、RO はプロセスばらつきの影響を 受けやすい. 提案手法と同様に IR-drop の測定に RO を 用いる Abuhamdeh らの手法では, 異なる電圧条件にお ける RO の発振周波数を回路シミュレーションであらか じめ求め, RO の発振周波数の実測値から回路の電源電 圧を推測する[6].この手法ではプロセスばらつきの影響 を排除することが難しい.提案手法では複数の消費電流 が流れる条件における発振周波数の差分をとることで、 プロセスばらつきの及ぼす影響を抑制している.

図 8: IR-drop の測定例.

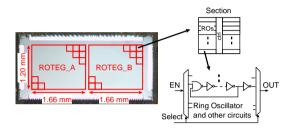

図 9: ブロックダイヤグラム.

図 8 に 1 つの RO における IR-drop の推測結果を示す.X 軸は PDN に流れた電流値を示し,Y 軸は RO の発振周波数を表す.Step 2 で述べたとおり,電流の変動が小さい領域では発振周波数の変動はおおむね線形である事がわかる.この測定結果をフィッティングすることで,IR-drop の無い条件における RO の発振周波数を推測することができる.また式 (1) を用いることで,任意の消費電流における IR-drop を求めることができる.提案回路をチップ上に集積することで,チップ内の PDNの IR-drop 分布を得ることが可能となる.

#### 4.2 65nm プロセスにおける PDN の抵抗の抽出

図 9 に , QFP パッケージに封入された IR-drop 分布測定 TEG の写真と , 回路のブロックダイアグラムを示す . 65 nm 12 配線層プロセスにて作成した . この TEG は , "ROTEG\_A"と "ROTEG\_B" と呼ばれる大きなブロックから構成されている . 各 "ROTEG" マクロには "Section" と呼ぶ基本要素がアレイ状に構成され , 各 "ROTEG" マクロは "Section" マクロを縦 15 個 , 横 18 個の計 270 個搭載している . アレイ構造をとることで ,  $79.2\mu$ m/ $79.2\mu$ m という解像度でチップ内の IR-drop 分布を得ることが可能である . 各 "Section" マクロには RO と VCCS が搭載されるが , "ROTEG\_A" に搭載された "Section" マクロと , "ROTEG\_B" に搭載された "Section" マクロ内部の RO の種類は異なる . そのためスタンバイ電流が 2 つ

の "ROTEG"マクロで異なり,"ROTEG\_A"は 32~mA,"ROTEG\_B"は 1~mA となっている.IR-drop 分布の取得で利用した RO は,2~つの "ROTEG"マクロで同一構造を持つ標準サイズのインバータからなる 7~PR RO を利用した.

TEG の電源構造は,2章で議論したメッシュ構造を とっている.TEG は QFP パッケージに封入され,パッ ケージ内部ではインターポーザによる配線を利用する ことで抵抗を削減している.インターポーザを介する ため, リードフレームとインターポーザ間, およびイン ターポーザと PAD の間はボンディングワイヤによって 接続されている . チップ外周部にはコア領域を囲うよう に IO RING が配置され,電源 IO セルを介して PAD と IO RING が接続されている. コア領域には VDD およ び VSS 用の電源メッシュがあり, それぞれ  $236 \times 91$  本 と  $432 \times 182$  本の電源配線から構成されている. VDD および VSS の電源 IO セルはそれぞれ 8 個と 16 個であ リ, 等間隔に IO RING に接続されている、表 2 にレイ アウトおよびデータシートから算出した各抵抗の情報を 示す . 特筆すべき点として , リードフレーム , ボンディ ングワイヤおよび IO セル内部の抵抗はすべて直列に接 続される事があげられる.そのため計  $1.885~\Omega$  の抵抗が 各電源 IO セルに接続されていることになる.

#### 4.3 測定結果とシミュレーション結果の比較

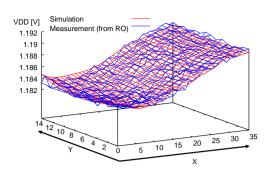

IR-drop 測定回路を用いて測定した IR-drop 分布と,表 2 のパラメータを利用してシミュレーションした結果を図 10 に示す.図の各交点は,IR-drop 分布の測定に利用した VCCS と RO が配置されている "Section"マクロの位置を示している.VDD には外部から定格電圧となる 1.2 V を供給している.実測およびシミュレーション結果はほぼ同等の分布となり,"ROTEG\_A"マクロにおいてもっとも IR-drop が発生していることがわかる.結果から,およそ 10 mV の IR-drop が各電源 IO セル部にて発生している事がわかる.この IR-drop は各電源IO セルの抵抗成分に起因するものであり,チップ内部

表 2: PDN 中の重要な抵抗の一覧.

|                      | $[\Omega]$ | 補足                               |

|----------------------|------------|----------------------------------|

| リードフレーム              | 0.318      | L = 15 mm と仮定                    |

| リードフレーム-インターポーザ      | 0.124      | L = 2.5  mm,                     |

| 間のボンディングワイヤ          |            | $\phi = 25 \ \mu \mathrm{m}$ と仮定 |

| インターポーザの配線           | 0.610      | $L=5~\mathrm{mm}$ と仮定            |

| インターポーザ-チップ間の        | 0.249      | L = 5  mm,                       |

| ボンディングワイヤ            |            | $\phi=25~\mu\mathrm{m}$ と仮定      |

| 電源用 IO セル            | 0.579      |                                  |

| IO RING              | 0.552      | 14.4 μm あたり                      |

| 電源メッシュ               | 0.276      | 14.4 μm あたり                      |

| コア領域における Stacked VIA | 0.9        | 9 層スタック                          |

| 電源レール                | 0.124      | 11.4 μm あたり                      |

図 10: IR-drop 分布の実測およびシミュレーション結果

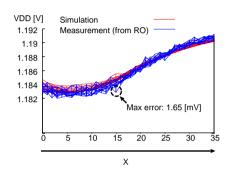

図 11: IR-drop 分布の実測およびシミュレーション結果 (断面図).

の電源メッシュの最適化では改善することはできない、またチップ周辺の電圧分布が一定であると述べている文献 [1][2] とは異なり、チップ周辺の電圧分布も均一ではない事がわかる、IR-dropの最大値は "ROTEG-A"マクロ中央付近にて観測され、IR-dropの最小値との差は約5 mV であった、この TEG の設計では、電源メッシュの性能よりも各電源 IO セルの抵抗がチップ内の IR-drop分布に与える影響の方がより大きいことがわかる。

図 11 は図 10 を横から見た図である.実測結果とシミュレーション結果との誤差は $1.65~\mathrm{mV}$  である.供給される電源電圧  $1.2~\mathrm{V}$  に対する誤差は $1.65~\mathrm{mV}$  である. 供給される電源電圧  $1.2~\mathrm{V}$  に対する誤差は $1.65~\mathrm{mV}$  である. この誤差の原因は,電源電圧に対する発振周波数の感度係数  $K_{VDD}$  をシミュレーションから求め,すべての RO に適用しているためである.RO はそれぞれプロセスばらつきによって特性が変動しているため,電源電圧に対する発振周波数の感度係数は RO ごとに異なるためである. 一方で,RO の発振周波数のチップ内ばらつきは $1.55~\mathrm{W}$ であった. 提案手法の誤差はチップ内ばらつきよりも小さく,プロセスばらつきの影響をよく抑制していると言える.

### 5 結論

本論文では、チップの PDN を評価するために用いる シミュレーションモデルの提案およびその評価につい て議論した . チップ内部だけでなく , チップ外部となる パッケージ等の抵抗を考慮した PDN シミュレーション モデルを示した. PDN シミュレーションモデルを用い た検討結果から,リードフレーム,インターポーザ,ボ ンディングワイヤの抵抗は PDN の品質に影響を及ぼす ことがわかった.これらチップ外部の PDN における抵 抗は , チップの IR-drop の最大値だけでなく , 最小値に も影響した.一方で電源メッシュや IO RING といった チップ内部の PDN の抵抗は, IR-drop の最大値と最小 値の比を変える事がわかった.両者を考慮した全体的な PDN の設計を行う必要がある事が明らかになった、構 築したシミュレーションモデルの妥当性を検証するため、 65 nm 12 配線層プロセスを例にした PDN の抵抗の抽 出,およびIR-drop 測定回路を利用したIR-drop の実測 を行った.抽出した抵抗によるシミュレーションモデル と実測結果の傾向はよく一致し,最大誤差は0.13%で あった. リードフレームやボンディングワイヤといった 各電源 IO セルあたりの抵抗は、チップ内部の IR-drop 分布に影響を及ぼすことが実測結果からも確認された.

# 謝辞

本研究の一部は、経済産業省から STARC に委託された「次世代回路アーキテクチャ技術開発事業」により実施した。チップ試作は東京大学大規模集積システム設計教育研究センターを通し 株式会社半導体理工学研究センター、(株) イー・シャトルおよび富士通株式会社の協力で行われた。

# 参考文献

- [1] K. Shakeri et al., "Compact Physical IR-Drop Models for Chip/Package Co-Design of Gigascale Integration (GSI)," *IEEE Trans. on Electron Devices*, vol. 52, pp. 1087–1096, 2005.

- [2] R. Bhooshan et al., "Optimum IR Drop Models for Estimation of Metal Resource Requirements for Power Distribution Network," in VLSI-SoC, 2007, pp. 292– 295.

- [3] R. Bhooshan, "Novel and Efficient IR-drop Models for Designing Power Distribution Network for Sub-100nm Integrated Circuits," in *ISQED*, 2007, pp. 287–292.

- [4] Q.K. Zhu et al., "Simulation and Planning Method for On-Chip Power Distribution An Industry Perspective," in *DDECS*, 2009, pp. 174–177.

- [5] T. Okumoto, et al., "A built-in technique for probing power-supply noise distribution within large-scale digital integrated circuits," in VLSI Symp. on Circuit, 2004, pp. 98–101.

- [6] Z. Abuhamdeh, et al., "Separating Temperature Effects from Ring-Oscillator Readings to Measure True IR-Drop on a Chip," in ITC, 2007, pp. 21–26.