# 集積回路におけるシングルイベント効果の評価と ソフトエラー耐性向上手法の提案

古田 潤

# 目次

| 目次  |                                |    |

|-----|--------------------------------|----|

| 第1章 | 序論                             | 1  |

| 1.1 | まえがき                           | 1  |

| 1.2 | 放射線が LSI に与える影響                | 3  |

| 1.3 | シングルイベント効果の歴史的背景               | 6  |

|     | 1.3.1 シングルイベント効果の動向            | 6  |

| 1.4 | シングルイベント効果の種類                  | 7  |

|     | 1.4.1 SET                      | 7  |

|     | 1.4.2 SEU                      | ç  |

|     | 1.4.3 SEMT ∠ MCU               | 10 |

| 1.5 | <b>従来研究</b>                    | 12 |

|     | 1.5.1 シミュレーションによるシングルイベント効果の評価 | 12 |

|     | 1.5.2 加速試験によるシングルイベント効果の評価     | 14 |

|     | 1.5.3 耐ソフトエラー回路                | 15 |

| 1.6 | 本研究の目的と概要                      | 16 |

|     | 1.6.1 論文の構成と各章の概要              | 16 |

| 第2章 | 回路シミュレーションを用いたシングルイベント効果の評価    | 19 |

| 2.1 | まえがき                           | 19 |

| 2.2 | 回路シミュレーションを用いたシングルイベント効果の評価手法  | 20 |

|     | 2.2.1 中性子起因の誘起電荷による電流          | 20 |

|     | 2.2.2 デバイスシミュレーションの電流波形との比較    | 22 |

|     | 2.2.3 粒子線衝突による基板電位の変動の適用       | 24 |

<u>ii</u> <u>目次</u>

|     | 2.2.4 回路シミュレーションの意義と限界              | 2 |

|-----|-------------------------------------|---|

| 2.3 | フリップフロップにおけるシングルイベント効果の評価           | 2 |

|     | 2.3.1 評価に用いた回路の構造                   | 2 |

|     | 2.3.2 保持データとクロック信号依存性               | 3 |

|     | 2.3.3 ウェルコンタクト距離依存性                 | 3 |

|     | 2.3.4 ラッチ間距離依存性                     | 3 |

| 2.4 | 論理ゲートにおけるシングルイベント効果の評価              | 3 |

|     | 2.4.1 評価に用いた回路の構造                   | 3 |

|     | 2.4.2 駆動力に対する SET 発生率の変化            | 3 |

|     | 2.4.3 SET のパルス幅分布                   | 3 |

| 2.5 | まとめ                                 | 4 |

| 第3章 | 加速試験を用いたシングルイベント効果の特性評価             | 4 |

| 3.1 | まえがき                                | 4 |

| 3.2 | フリップフロップにおけるシングルイベント効果の特性評価         | 4 |

|     | 3.2.1 シフトレジスタを用いた評価手法               | 4 |

|     | 3.2.2 フリップフロップにおけるシングルイベント効果の特性評価回路 | 4 |

|     | 3.2.3 加速試験によるシングルイベント効果の評価方法        | 4 |

|     | 3.2.4 中性子線による評価結果                   | 4 |

|     | 3.2.5 フリップフロップにおけるシングルイベント効果の特性のまとめ | 5 |

| 3.3 | 論理ゲートにおけるシングルイベント効果の特性評価回路          | 5 |

|     | 3.3.1 既存の評価手法と問題点                   | 5 |

|     | 3.3.2 チェイン通過によるパルス幅変動現象             | 5 |

|     | 3.3.3 パルス幅縮小現象を利用した SET パルス幅測定回路    | 6 |

|     | 3.3.4 リングオシレータ構造を用いた SET パルス幅測定回路   | 6 |

| 3.4 | 論理ゲートにおけるシングルイベント効果の特性評価結果          | 6 |

|     | 3.4.1 加速試験によるシングルイベント効果の評価方法        | 6 |

|     | 3.4.2 SET パルス幅測定回路の動作確認結果           |   |

|     | 3.4.3 中性子線による評価結果                   | 7 |

|     | 3.4.4 論理ゲートにおけるシングルイベント効果の特性のまとめ    | 7 |

| 3.5 | まとめ                                 | 8 |

| 第4章 | ソフトエラー耐性向上手法                        | 8 |

| 4.1 | まえがき                                | 8 |

| 4.2 | 従来の耐ソフトエラー回路                        | 8 |

|     | 4.2.1 三重化フリップフロップ                   | 8 |

| 43  | 耐ソフトエラー回路の提案                        | Ç |

| 目次 | iii |

|----|-----|

|    |     |

| 4.4  | 多重化   | 回路のソフトエラー耐性向上手法     | 88  |

|------|-------|---------------------|-----|

|      | 4.4.1 | MCU 発生率を低減する設計手法    | 89  |

|      | 4.4.2 | SET によるエラーを低減する設計手法 | 91  |

| 4.5  | 加速試   | 験によるソフトエラー耐性評価結果    | 96  |

|      | 4.5.1 | 設計した多重化回路の構造        | 96  |

|      | 4.5.2 | 多重化回路のソフトエラー耐性評価回路  | 96  |

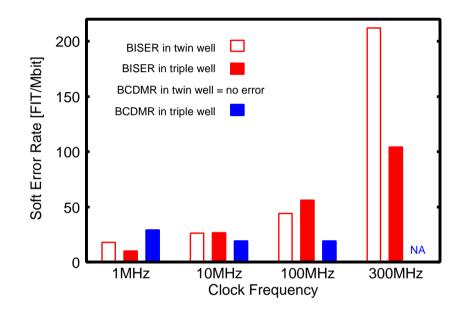

|      | 4.5.3 | 加速試験によるソフトエラー率の評価結果 | 98  |

| 4.6  | まとめ   |                     | 103 |

| 第5章  | 結論    |                     | 105 |

| 謝辞   |       |                     | 109 |

| 参考文南 | ‡     |                     | 111 |

| 発表論文 | てリスト  |                     | 121 |

## 第1章

# 序論

#### 1.1 まえがき

半導体の微細加工技術の進歩により、LSI (Large Scale Integrated circuit, 大規模集積回 路) に搭載されるトランジスタの個数はムーアの法則に従い指数関数的に増加している [1]. 近年では製品レベルで最小ゲート長が 22nm を達成し、数億トランジスタが 1 チップ に集積される. 製造プロセスの微細化により、LSI は小型化・大規模化している. 一方で 放射線起因のシングルイベント効果による誤動作が増加しており、LSIの信頼性の低下に 対する懸念が高まっている. シングルイベント効果とは、重イオンや中性子などの放射線 が LSI に入射することにより生じる [2]. 放射線の電離作用によって生じた電子正孔対が ドリフトなどによってトランジスタの拡散領域に収集され、トランジスタの出力が一時 的に反転する. シングルイベント効果によって論理ゲートの出力に一過性のパルスが生 じたり、SRAM などの記憶素子の保持値が反転したりする. この放射線起因の誤動作は一 時的なものである. 永続的なエラーであるハードエラーと区別するために, ソフトエラー と呼ばれる[2]. トランジスタの微細化に伴い, LSI のソフトエラー発生率は増加してい る[3]. 以前は放射線の多い宇宙空間で稼働する衛星などの宇宙機器での問題であった. しかし 2000 年代になると地上でもソフトエラーが原因の故障が顕在化し、サーバやスー パーコンピュータ向けの LSI ではソフトエラーの対策が必須となっている [4]. また誤動 作が人命に関わる医療機器や自動車のブレーキ制御などでも高い信頼性が要求されるた め、ソフトエラーの対策が求められる [5] 人工衛星などの宇宙用の LSI では、回路の動作 速度よりも故障しないことが要求される. そのため数世代前のプロセスを用いて設計す るなどの回路性能を犠牲にしたソフトエラー対策が行われている[6]一方でスーパーコ

第1章 序論

ンピュータやデータセンターなどの場合では、製造コストを小さくすることが要求されるだけでなく、高い動作速度や低消費電力が求められる. 地上で使用される LSI ではより 効率的なソフトエラー対策が必要である.

ソフトエラーの対策にはシステムレベルの対策から、フリップフロップなどの回路レベルの対策まで幅広く存在する。システムレベルでの対策として、同一の処理を複数回実行する方法や、LSIを複数用意して同一の処理を行う方法がある。システムレベルでの対策では LSI の実行結果を比較することでソフトエラーによる誤動作を確実に検出できる。しかし消費電力や実行時間が倍増するため、コストが高い。また、京コンピュータに代表されるスーパーコンピュータでは数万単位の LSI で構成されるため、回路レベルの対策なしでは数分に1回の割合でソフトエラーが生じる[7]。スーパーコンピュータではシステムレベルの対策のみを行っても、ソフトエラーを除去することは困難である。システムレベルの対策を行う場合でも回路レベルの対策は必須となる。

回路レベルでのソフトエラー対策として一般的に用いられる構造には、三重化回路に代表される多重化回路と、SRAM に良く用いられる ECC (Error Checking and Collectionまたは Error Check Code) がある [8]. 三重化回路はフリップフロップなどの記憶素子を三重化し、保持値の多数決をとることで出力値を決定する。そのため、シングルイベント効果によって1つのフリップフロップの保持値が反転しても、出力は正しい値を保ち続ける。 ECC では誤り訂正符号を SRAM に付加することで、シングルイベント効果による値の反転を検知して正しい値に修正する。 回路レベルでのソフトエラー対策では、シングルイベント効果に脆弱な回路構造を特定し、その部分に対策を施すことで効率的に LSI 全体のソフトエラー耐性を向上することが出来る。 効率的にソフトエラー耐性を向上させるにはシングルイベント効果に脆弱な構造をトランジスタレベルで評価する必要がある。

微細設計技術の進歩により、放射線の影響は単一トランジスタのみでなく、隣接する複数のトランジスタに同時に影響を与えるようになっている [9–11] 複数のトランジスタが影響を受けるため、複数の記憶素子が反転する多ビットエラーが生じる。 多ビットエラーが生じると多重化回路でも保持データが反転してしまう。 ソフトエラー耐性を高く保つには多ビットエラー発生率を低減する回路設計手法や回路構造が求められる。 効果的な低減手法を検討するためには多ビットエラーの特性を実測などによって評価する必要がある。

本研究の目的は、地上でのシングルイベント効果を評価し、LSIのソフトエラー耐性を向上させる設計手法を提案することである。実測やシミュレーションを用いて地上でのシングルイベント効果の特性を評価する。評価した結果を基にして、効率的なソフトエ

ラーの対策を検討する. 本研究は回路シミュレーションを用いたシングルイベント効果の解析と,実測によるシングルイベント効果の評価,それらの評価結果を考慮したソフトエラー耐性向上手法の提案から構成される. 回路シミュレーションを用いた解析では,放射線による基板電位の変動を回路モデルに組み込むことで,放射線が複数のトランジスタに与える影響を評価する. 実測によるシングルイベント効果の評価では,回路を試作して白色中性子ビームを照射する. 回路シミュレーションや実測によるシングルイベント効果の評価結果を基にして、ソフトエラー耐性を効果的に向上させる設計手法を示す.

本章の構成を以下に示す. 1.2 節では放射線が LSI に与える影響を示す. 1.3 節ではソフトエラーの歴史的背景を説明して, 地上でのソフトエラーを引き起こす放射線の種類をまとめる. 1.4 節でシングルイベント効果の分類を示し, 微細化により複雑化するシングルイベント効果の発生原理を説明する. 1.5 節で本研究分野における課題と従来研究を説明する. 最後に本稿の構成と, 各章の概要を 1.6.1 節にまとめる.

#### 1.2 放射線がLSIに与える影響

放射線がLSIに与える影響は主に3種類に分類される[12].

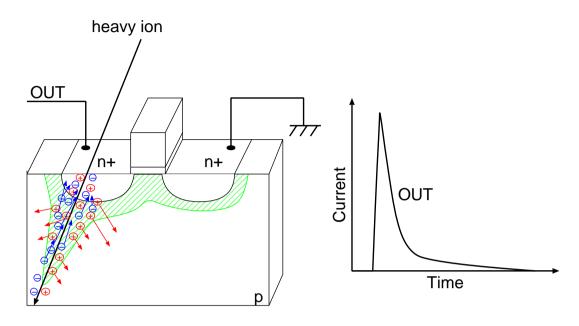

シングルイベント効果 (SEE: Single Event Effect) 重イオンなどの放射線が LSI に入射 すると、その電離作用により LSI の基板などに電子正孔対が生じる. 生じた電子正 孔対によってイオンが通過した領域が高伝導状態になる. 高伝導状態になるとそれ まで空乏層に印加されていた電界がゆがみ、空乏層の外まで電界が延びる. 延びた 電界によって空乏層外の電荷がトランジスタの拡散領域に収集される. この現象を ファネリング効果と呼ぶ[13]. ファネリングとドリフトによってトランジスタの拡 散領域に電荷が収集され、その後に拡散によって緩やかに電荷が収集される. シン グルイベント効果による電荷の収集を図1.1に示す. 収集された電荷によってトラ ンジスタの出力が一時的に反転する.放射線によってトランジスタの出力が一時的 に反転現象をシングルイベント効果と呼ぶ. シングルイベント効果が記憶素子を構 成するトランジスタで生じると、その保持データが反転してしまう、またシングル イベント効果により生じた論理ゲートのパルス状の反転をフリップフロップが取り 込んだ場合でも保持データが反転してしまう. これらのシングルイベント効果によ る保持データの反転をソフトエラーと呼ぶ. シングルイベント効果によってフリッ プフロップの保持データが反転してソフトエラーが生じても、そのデータが参照さ れない場合も多く、その場合にはLSIの出力に影響を及ぼさない.

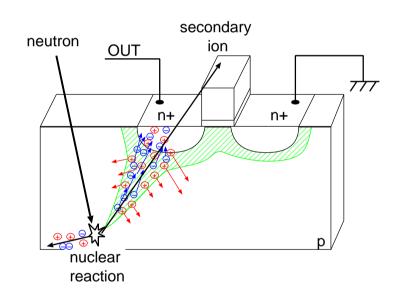

宇宙空間では重イオンがシングルイベント効果の主要因である。一方で地上におけるシングルイベント効果の主要因は中性子起因の二次イオンである [14]. 高エネルギー中性子が LSI の Si 原子核と核反応を起こし、二次イオンが生じる。生じた二次イオンの電離作用により、電子正孔対が生じてシングルイベントが発生する [2]. この中性子起因の二次イオンによるシングルイベント効果を図 1.2 に示す.

シングルイベント効果は1つの放射線がLSIを通過することで生じる確率的な誤動作である. 放射線が多い宇宙空間ではシングルイベント効果の対策が必須である. 放射線の少ない地上でも回路規模の大きいサーバや, 誤動作が人命に関わる医療機器や自動車などでLSIの信頼性を低下させる要因として注目されている. シングルイベント効果によって生じるソフトエラーは一過性であるため, 誤動作が生じたLSIでも再起動すれば正常に動作する.

トータルドーズ効果 (TID: Total Ionizing Dose Effect) 放射線が LSI に入射することで生じる電子正孔対により、固定電荷や界面準位が形成される. 形成された固定電荷や界面準位により、半導体素子のリーク電流の増加やしきい値電圧のシフトなどが生じる. この放射線による半導体素子の特性の劣化をトータルドーズ効果と呼ぶ[12]. トータルドーズ効果によってトランジスタのリーク電流が増加すると、DRAMが値を保持できなくなり、LSI が誤動作する. 劣化した諸特性は回復しないため、一度誤動作が生じると LSI は永続的なエラーであるハードエラーとなる.

トータルドーズ効果はLSIに入射した累積放射線量に依存するため、重イオンなどの放射線が多い宇宙空間で問題となっている。地上では放射線量が少ないため、トータルドーズ効果による半導体素子の特性の劣化は生じない。半導体素子の特性が劣化すると、回路構造やシステムでの対策が不可能である。トータルドーズ効果による半導体素子の特性の劣化量を小さくするために、遮蔽物などによってLSIに入射する放射線を減らす方法が用いられる。

はじき出し損傷効果 (DDD: Displacement Damage Dose Effect) 放射線の入射により、半導体結晶を構成する原子がはじき出されることによって引き起こされる. トータルドーズ効果と同様に半導体素子の諸特性を劣化させるハードエラーに分類される. MGy オーダーの非常に多量の放射線によって生じる [12].

トータルドーズ効果とはじき出し損傷効果は放射線の影響が蓄積することで生じるため、放射線の多い宇宙空間でのみ問題となる.一方でシングルイベント効果は宇宙空間だけ

図 1.1: シングルイベント効果の発生原理.

図 1.2: 中性子起因の二次イオンによるシングルイベント効果.

でなく、地上でもシングルイベント効果による誤動作が問題となっている。サーバやスーパーコンピュータ向けのLSIではシングルイベント効果を考慮した設計が必須となっている [4,7]. 本論文では地上でのシングルイベント効果を研究対象とする。シングルイベント効果が回路に与える影響や特性を評価し、シングルイベント効果によるソフトエラーを低減する手法を検討した結果を報告する。

第1章 序論

#### 1.3 シングルイベント効果の歴史的背景

シングルイベント効果が最初に報告されたのは 1975 年に人工衛星で発生した LSI の不具合である [15]. この不具合は宇宙空間に存在する陽子や He などによって生じたと報告された. 現在でも重イオンによるソフトエラーは宇宙開発における重要な問題として認識されている.

地上でのソフトエラーが最初に報告されたのは 1978 年である. プラスチップパッケージに含まれるウランやトリウムなどの不純物から放出された  $\alpha$  線により, DRAM の保持データが反転することが報告された [16]. パッケージ材料の高純度化や, ポリイミド・コーティングによる遮蔽などの対策により,  $\alpha$  線によるソフトエラーの発生率は減少した.

1980年代では $\alpha$ 線によるソフトエラーの研究が中心であった。1996年以降にはIBMの研究グループが中性子起因のソフトエラーに関する広義な研究を報告したことにより、その重要性が強く認識されるようになった [17]。宇宙から飛来した重イオンが大気中に突入することで高エネルギー中性子が生じる。生じた中性子はLSI 基板の Si 原子と核反応して二次イオンを生成し、ソフトエラーを引き起こす。1995年には層間絶縁膜として使われている BPSG (borophosphosilicate glass) 膜に存在する  $^{10}$ B が熱中性子を吸収して $\alpha$ 線を放出することにより、ソフトエラーを引き起こすと報告された [18]。2000年以降になると、BPSG 膜による層間絶縁膜の平坦化処理に代え、CMP (Chemical Mechanical Polishing) と呼ばれる化学的機械研磨が一般的に用いられるようになった。BPSG 膜の使用頻度の減少に伴い、熱中性子によるソフトエラーの影響は小さくなった。しかし配線中にも  $^{10}$ B が存在するため、熱中性子起因のソフトエラーは完全に除去できていない [19]。

#### 1.3.1 シングルイベント効果の動向

微細化によって動作電圧の低下やトランジスタのゲート容量の減少により、トランジスタの出力を反転するために必要な電荷が減少している。そのためプロセスの微細化に伴って SRAM 1 ビット当たりのシングルイベント効果の影響は増加した [2,3]. しかし 0.18 μm プロセス以降では、SRAM 1 ビット当たりの中性子起因のソフトエラー率は減少傾向にある [20]. SRAM の面積が小さくなることで放射線の入射確率が減少したためである。チップ当たりの SRAM の集積数は増加傾向にあるため、チップ当たりのソフトエラー率自体は増加している.

ラッチやフリップフロップのソフトエラー率に関しては文献[3]で微細化に伴い急激

に増加すると予想されている。文献 [21] では 130nm と 90nm プロセスのラッチのソフトエラー率を測定し、SRAM のソフトエラー率と同等になっていることを報告している。 SRAM と同様にラッチやフリップフロップでもシングルイベント効果に対する対策が必要となっている.

#### 1.4 シングルイベント効果の種類

シングルイベント効果によるソフトエラーは粒子線の通過箇所により 2 種類に分類される. 組み合わせ回路部分で生じる SET(Single Event Transient) と, SRAM などの記憶素子で生じる SEU(Single Event Upset) である. 1 つの粒子が入射することで複数の SET や SEU が生じる場合がある. 複数の SET が生じた場合を SEMT(Single Event Multiple Transient) と呼び, 複数の SEU が生じた場合を MCU(Multiple Cell Upset) と呼ぶ.

回路レベルでのソフトエラー対策では、これらのシングルイベント効果を全て低減する必要がある。シングルイベント効果が回路動作に与える影響を評価し、SET や SEU の発生率を求め、発生率に応じた対策を行う必要がある。

#### 1.4.1 **SET**

放射線の通過により、組み合わせ回路の論理ゲートの出力に電荷が生じると、論理ゲートの出力が反転する。しかし論理ゲートの入力は反転していないため、放射線によって生じた電荷はトランジスタのオン電流によって打ち消される。論理ゲートの出力は元の値に戻るが、値が元に戻るまでの時間幅のパルスが生じる。この論理ゲートの出力に生じる一過性のパルスが SET である。SET のパルスがラッチのデータ通過期間とデータ保持期間の切り替え時にラッチに丁度到達していると、ラッチが反転した値を保持してしまう。SET はラッチやフリップフロップに取り込まれない限りエラーとはならない。ラッチの入力に到達する前に様々な要因で SET によるパルスはパルス幅が減衰したり、消滅してしまう場合がある。この SET パルスを減衰または消滅させる 3 種類の遮蔽効果を以下に示す。

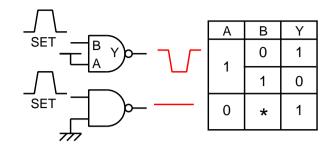

論理的遮蔽 (logical masking) SET パルスが論理ゲートを通過する時に,他の入力の値によっては SET パルスの入力の値はドントケアの場合がある. この場合では論理ゲートの出力は SET によって変化しないため, SET が除去される. 例を挙げると図 1.3 に示す 2 入力 NAND などがある. NAND の片側の入力が 0 の場合では,もう片方の

8 第1章 序論

入力に SET による反転が入力されても出力は正しい値を保つ.

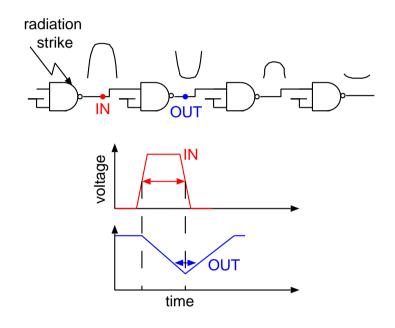

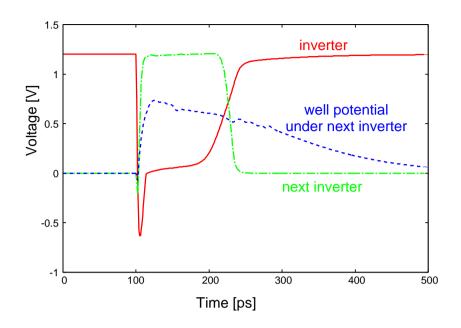

電気的遮蔽 (electrical masking) 生じた SET のパルス幅が論理ゲートの遅延時間より小さい場合では、論理ゲートの出力が SET によって完全に反転する前に入力値が元の値に戻る。そのため、論理ゲートを通過するごとにパルス幅が減少する。電気的遮蔽の例を図 1.4 に示す。図 1.4 は NAND チェインに SET が生じた場合の、生じた SET の電圧波形と、次段の NAND の出力波形を示している。生じた SET のパルス幅が論理ゲートの立ち上がり遅延時間よりも小さいため、図 1.4 下に示す NAND の出力は0まで下がらない。そのため、SET のパルス幅が NAND ゲートを通過すると減少する。電気的遮蔽によってパルス幅が減少するため、SET はラッチに取り込まれにくくなる。

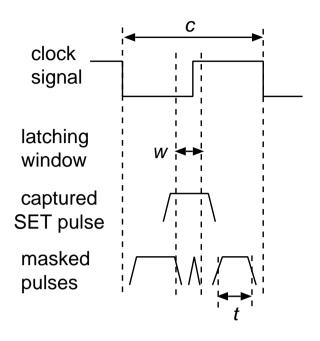

保持制約による遮蔽 (latching window maskinig) ラッチが値を取り込むためにはセットアップ制約とホールド制約を満たす必要がある. 保持制約による遮蔽を図 1.5 に示す. 図 1.5 にはフリップフロップのクロック入力の電圧波形と, 2 種類のデータ入力の電圧波形を示している. 図 1.5 の一番下側に示すラッチのセットアップ時間よりも短い SET や, クロックが遷移するタイミング以外で到達した SET は保持制約による遮蔽によってラッチに取り込まれない. ラッチに SET パルスが取り込まれる確率は SET のパルス幅 t, ラッチの保持制約 w, クロック周波数 1/c より求められる. ラッチの SET パルスによるソフトエラー率 (Soft Error Rate: SER) は式 (1.1) となる [22].

$$SER_{SET} = \int_{w}^{c} \Delta N(t) \frac{t}{c} dt$$

(1.1)

$\Delta N(t)$  はパルス幅 t の SET が発生する確率である. 式 (1.1) に示すように, クロック 周波数が増加すると SET によるエラーは増加する.

組み合わせ回路で生じる SET によるエラーの発生率を見積もるためには、これら 3 種類の遮蔽効果を考慮する必要がある. しかし論理遮蔽や電気的遮蔽の影響は組み合わせ回路の構造によって異なる. 保持制約による遮蔽も LSI の動作周波数に依存する. SET によるエラーを評価する場合では、まず論理ゲートで生じる SET の発生率とそのパルス幅を評価する. 評価した SET の発生率とパルス幅を基にして上記の遮蔽効果の影響を計算し、任意の構造の組み合わせ回路で生じる SET の影響を見積もることが重要となる.

図 1.3: 論理的遮蔽 (logical masking) の例.

図 1.4: 電気的遮蔽 (electrical masking) の例.

#### 1.4.2 **SEU**

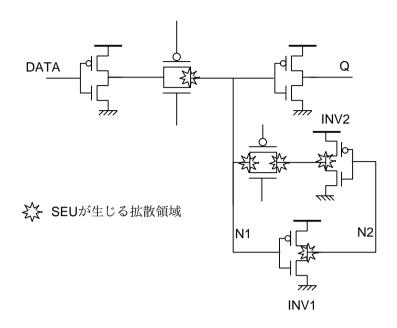

SRAM やラッチはデータを保持するループ状の構造を持つ. このループ構造に接続されているトランジスタの拡散領域に放射線による電荷が収集されると, 保持データが反転してしまうことがある. 図 1.6 においてラッチの保持データ Q が "1" である場合を例に SEU の発生を説明する. 放射線が入射して INV1 の nMOS トランジスタのドレイン領域に電荷が収集されると, N2 の値は "1" から "0" に反転する. N2 の値が "1" に戻る前に INV2 の出力が反転すると, INV1 の入力である N1 も反転してしまう. N2 が "0", N1 が "1" で安定し, ラッチの保持データ Q が反転する. このようにラッチ内部に放射線が衝突し, ラッチの保持データを直接反転させるシングルイベント効果が SEU である.

10 第1章 序論

図 1.5: 保持制約による遮蔽 (latching window masking).

SEU は SET とは異なり、記憶素子の保持データを直接反転する. しかし保持データが反転しても回路が必ず誤動作するわけでは無い. シングルイベント効果によってフリップフロップの保持データが反転しても、そのデータが参照されない場合も多く、その場合には LSI の出力には影響を及ぼさない.

トランジスタの出力が反転している時間は収集された電荷量に依存する。そのため、一定量以上の電荷がドレインに集められると必ずラッチの保持データが反転して SEU となる。このラッチの保持データを反転するのに必要な最低電荷量を臨界電荷量  $Q_{crit}$  (critical charge) と呼ぶ [23]。 微細化により電源電圧が低下し、トランジスタのゲート容量が減少している。そのため  $Q_{crit}$  は減少し続けている。 SEU は SET と比較して発生しやすく、サーバやスーパーコンピュータなどの SRAM の多い LSI では対策が必須である。 2008 年にはラッチにも SEU 対策を施したサーバ用 LSI が報告されている [24].

#### 1.4.3 SEMT \( \subseteq MCU

MCU は 1 つの放射線の入射によって複数の SRAM やラッチの保持データが反転する 現象である. MBE (Multiple Bit Error) や SEMU (Single Event Multiple Upset) とも呼ばれる. 同様に SEMT は 1 つの放射線の入射によって複数の論理ゲートの出力が一時的に反

図 1.6: SEU が生じるラッチのトランジスタの拡散領域.

転し、複数の一過性のパルスが生じる現象である。MCU や SEMT の発生原理として、寄生バイポーラ効果 (parasitic bipolar effect) と電荷共有 (charge sharing)、連続衝突 (successive hits) が挙げられる。各発生原理を以下に示す。

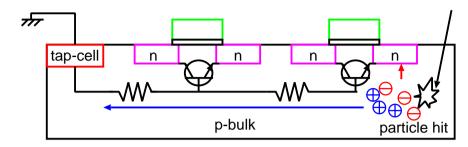

- 寄生バイポーラ効果 (parasitic bipolar effect) 寄生バイポーラ効果による MCU を図 1.7 (a) に示す. 中性子の衝突により生じた電子正孔対のうち, 基板に残留した電荷によって基板電位が上昇する. トランジスタのドレイン-基板-ソース間に寄生しているバイポーラトランジスタが基板電位の上昇により ON となる. 粒子線の衝突位置に隣接したトランジスタの出力も反転し, MCU や SEMT となる [25]. 基板電位を固定するウェルコンタクト近傍では寄生バイポーラ効果は発生しにくい [10].

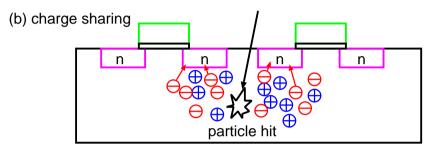

- 電荷共有 (charge sharing) 電荷共有による MCU を図 1.7 (b) に示す. トランジスタの微細化により, トランジスタのサイズは小さくなっている. トランジスタのサイズと比較した場合, 放射線が入射したことによって生じる電子正孔対の発生範囲は相対的に広くなっている. そのため, 生じた電子正孔対の影響を複数のトランジスタが受け, MCU や SEMT が発生する. この現象を電荷共有と呼ぶ. 寄生バイポーラ効果による電荷も含めて電荷共有と呼ばれる場合もある.

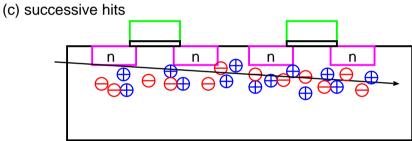

連続衝突 (successive hits) 連続衝突による MCU を図 1.7 (c) に示す. 放射線が複数のト

ランジスタ近傍を通過して電子正孔対を生成する. ドリフトやファネリング, 拡散により複数のトランジスタの拡散領域に電荷が収集される. 連続衝突は放射線の入射角度に依存している.

発生原理が異なるとその対策も異なる。電荷共有による MCU の対策では、トランジスタ間にダミーのトランジスタを配置し、生じた電荷をダミートランジスタに収集させる手法が提案されている [26]。しかし寄生バイポーラ効果による MCU や SEMT ではこの手法は効果がない。ダミーのトランジスタに衝突した場合では基板電位が変動し、寄生バイポーラ効果による MCU が生じやすくなると推測される。 MCU や SEMT を低減するにはその特性を評価し、 MCU や SEMT の発生原因となっている現象を明らかにする必要がある。

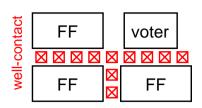

MCU が SRAM で生じると、SRAM でのソフトエラー対策である単純な誤り訂正符号では除去できない。MCU は SRAM にとって非常に大きな問題となっており、多くの文献で測定結果が報告されている [10,11]。 MCU は集積度の高い SRAM での問題であった。しかし微細化によりトランジスタ間距離が小さくなっているため、フリップフロップでも MCU は生じると推測される。ソフトエラー耐性回路である三重化フリップフロップでMCU が生じ、2 つのフリップフロップの保持データが反転すると、三重化フリップフロップはエラーとなる。フリップフロップでも MCU の発生率などの評価や、MCU 発生率を低減する回路設計が必要とされる。

#### 1.5 従来研究

ここでは従来研究について説明するとともに、従来研究で不足している点や改善すべき点を述べる。シングルイベント効果の評価結果である加速試験を用いた評価と、シミュレーションを用いて評価した文献を紹介する。次に、シングルイベント効果を低減する回路構造を紹介する。

#### 1.5.1 シミュレーションによるシングルイベント効果の評価

シングルイベント効果の評価方法はシミュレーションを用いた手法と放射線を照射して加速試験を行う方法の2種類がある. 加速試験はLSI 全体のソフトエラー率や, 記憶素子のソフトエラー率を評価するために用いられる. 一方でシミュレーションを用いる場合ではシングルイベント効果に対する脆弱性をトランジスタ単位で評価できる. また実

1.5. 従来研究 13

#### (a) parasitic bipolar effect

図 1.7: 放射線による多ビットエラーの発生原理.

際にLSIを試作する必要がない、シミュレーションはLSIの設計時にシングルイベント効果によるソフトエラー率を概算したり、シングルイベント効果に脆弱な部分を修正するために必要となる評価手法である。

放射線によって生じた電子正孔対の挙動を評価して、シングルイベント効果がトランジスタに与える影響を解析する場合には、デバイスシミュレーションが用いられる [27-30]. 文献 [31] では重イオンが入射した位置に対するトランジスタに収集される電荷量の変化が報告されている。 文献 [28,29] では寄生バイポーラ効果の影響を評価し、ウェルコンタクトによる SET 低減効果を確認した結果が報告されている。 中性子線によるシングルイベント効果の評価をする場合では、核反応シミュレータを用いて中性子と Si 原子の核反応を評価し、生じた二次イオンの影響をデバイスシミュレーションを用いて評価される。 文献 [27] では多ビットエラーの発生率を中性子の入射角度を変更して評価した結果が報

告されている. メタル層やコンタクトがソフトエラーに与える影響を評価している文献 も存在する [30].

放射線によって反転したトランジスタの出力が回路動作に与える影響を評価する場合では、回路シミュレーションが用いられる [23,32,33]. 文献 [23,32] では放射線の入射によって生じる励起電流を電流源に置き換えてシングルイベント効果の回路に対する影響を評価している。 文献 [33] では電圧源を用いて回路のソフトエラー耐性を評価している。 回路シミュレーションでは多ビットエラーの複雑な放射線の影響を評価する手法は提案されていない。 複数のトランジスタで生じる放射線の影響はデバイスシミュレーションを用いて評価されるが、回路規模が大きくなるとシミュレーションに必要な時間が増大する。 回路シミュレーションを用いて微細化により増加する多ビットエラーの影響を高速に評価することは、ソフトエラー耐性の高い LSI を設計するために重要となる。

#### 1.5.2 加速試験によるシングルイベント効果の評価

実測によるシングルイベント効果の評価は、集積度が高い SRAM を中心として行われている [10,11,20,25,34–36]. 文献 [10] では重イオン起因の SEU と MCU を測定し、生じた MCU の形状やウェルコンタクトに対する依存性が報告されている. 文献 [25] は SEU と MCU の電源電圧と基板電位に対する依存性を測定し、中性子による MCU が寄生バイポーラ効果によって生じていることを示した. 文献 [11] では複数の文献で示されている MCU と SEU の測定結果に基づき、微細化による MCU 発生割合 (MCU / SEU) の増加を示した. 65nm プロセス SRAM の中性子による MCU の割合はトリプルウェルで 80%を越えており、ツインウェルでも 20%と増加している. 微細化による MCU 発生割合の増加は文献 [20] でも報告されており、MCU は SRAM で生じるエラーの主要因となっている.

SRAM でのシングルイベント効果の評価結果と比較すると少ないものの, フリップフロップやラッチでのシングルイベント効果の測定結果も報告されている [21,37,38]. ラッチでの MCU に関する測定結果は 2011 年に文献 [39] で初めて報告されたが, それ以降の発表件数も SRAM での MCU の実測結果に比べると極めて少ない. 先に説明したように, 多重化フリップフロップでも MCU が生じるとエラーとなる. フリップフロップでの MCU 発生率が高い場合では, 多重化フリップフロップのエラー耐性の向上に MCU の対策が必須となる. 多重化フリップフロップのソフトエラー耐性を効率的に向上させるために, フリップフロップにおける MCU の特性評価が必要となる.

論理ゲートにおけるシングルイベント効果である SET の測定結果も報告されている

1.5. 従来研究 15

[40-44]. しかし文献 [45] では SET のパルス幅がインバータチェインを通過する間に線形に増加または減少することが報告されている. 多くの文献で測定対象として長い論理ゲートのチェインを用いているため, SET のパルス幅の測定精度に大きな問題がある. SET を正確に測定可能な回路構造と, SET のパルス幅を正確に評価した結果が求められている. 文献 [46] では 20 段のインバータチェインを用いることでチェイン通過によるパルス幅の変動の影響を抑制し, 100ps 以下の SET パルス幅分布を測定した結果を報告している. しかし文献 [46] では 100ps 以上の SET パルスのパルス幅分布は測定できていない.

#### 1.5.3 耐ソフトエラー回路

シングルイベント効果によるソフトエラーの対策として最も知られている手法は誤り訂正符号 (ECC) と回路の多重化である [47–50]. サーバなどの SRAM では ECC が標準的に使用されている [4]. 微細化により SRAM での MCU 発生率が上昇しているため, MCU が発生しない SRAM の構造や, MCU が生じても訂正可能な ECC の構造が提案されている [8,51]. 一方でソフトエラー耐性を持つフリップフロップやラッチの構造では多重化回路が複数提案されている. 文献 [52] ではラッチ 2 つと C 素子を用いた二重化回路が提案されている. 文献 [47,53] では DICE ラッチと呼ばれる回路が提案されている. DICE ラッチでは値を保持するループ構造を構成するインバータが 2 つから 4 つに増加した構造を持つため, 保持データが反転しにくい. DICE ラッチは実際のサーバにも利用されている [24]. また, 文献 [54] では負荷容量をフリップフロップに接続することでソフトエラー耐性を増加させる手法も提案されている.

SRAM では MCU の低減手法の研究が盛んに行われている。一方で多重化回路では MCU を考慮した構造を提案している文献は少なく [24,50], MCU の特性を評価した結果 を基にして設計手法を提案している文献はない。フリップフロップで MCU が生じた場合,多重化回路の複数の保持データが同時に反転してエラーとなる。40nm プロセスでは 実測により DICE ラッチ等のソフトエラー耐性が通常のフリップフロップの 3 倍程度で あることが報告されている [55]. 文献 [24] では DICE ラッチのソフトエラー耐性を通常 のラッチの 100 倍に向上させるために,DICE ラッチを構成するトランジスタを 1.1  $\mu$ m 以上離して配置している。多重化フリップフロップのソフトエラー耐性を向上させるために、トランジスタなどの配置手法などの回路構造以外の検討も必要である。

16 第1章 序論

#### 1.6 本研究の目的と概要

本研究は地上でのシングルイベント効果の特性を評価し、ソフトエラー耐性を向上させる設計手法を提案することを目的とする。シングルイベント効果の特性を基にしたソフトエラー低減手法を提案することで、実用性の高い耐ソフトエラー設計手法を示す通常のフリップフロップの 100 倍のソフトエラー耐性を具体的な数値目標として設定し、ソフトエラー耐性の向上手法の検討を行う。100 倍のソフトエラー耐性は実際のサーバ用プロセッサで利用されている DICE ラッチのソフトエラー耐性を参考にして決定した [24].シングルイベント効果の特性評価では、中性子線を照射する加速試験と回路シミュレーションによる解析を行う。SEU や SET の特性を評価するだけでなく、フリップフロップにおける MCU の特性も評価する。MCU が多重化フリップフロップのエラー耐性を低下させていることをシミュレーションだけでなく、実測からも示す。評価結果を基にしてMCU や SET を効果的に低減する回路の配置方法の提案を行う。最後に提案する設計手法を用いて多重化回路を設計し、実測によって提案する設計手法の有効性を確認する。

#### 1.6.1 論文の構成と各章の概要

第2章では、回路シミュレーションを用いてシングルイベント効果が回路動作に与える影響をトランジスタ単位で評価する。基板をモデル化し回路モデルに組み込むことで、寄生バイポーラ効果の影響を回路シミュレーションで評価可能とした。提案回路モデルを用いた回路シミュレーションにより、フリップフロップでもMCUが生じることを示す。同時に寄生バイポーラ効果がMCUの発生だけでなく、SEUやSETの発生率にも影響を与えることを示す。ソフトエラー耐性向上には寄生バイポーラ効果を考慮した設計が必要となることを示す。

第3章では、フリップフロップや論理ゲートでのシングルイベント効果を加速試験を用いて評価する。MCU の発生率を測定し、多重化フリップフロップのソフトエラー耐性が MCU によって低下していることを示す。論理ゲートの SET パルス幅を測定し、フリップフロップでの SEU 発生率と比較することで、SET によるエラーが占める割合を評価する。また MCU のフリップフロップ間距離依存性やウェルコンタクト密度依存性を実測により明らかにする。

第4章では、ソフトエラー耐性の高い二重化フリップフロップの提案を行う.また第2章と第3章で示すシングルイベント効果の特性評価結果を基にして、ソフトエラー耐性

が向上する設計手法の検討を行う. 提案する二重化フリップフロップを設計し, 加速試験によってソフトエラー耐性を評価する. 提案手法により, フリップフロップの 100 倍以上のエラー耐性が実現できることを示す.

## 第2章

# 回路シミュレーションを用いたシングルイベント効果の評価

本章では中性子線衝突による基板電位の変動を回路モデルに組み込み、寄生バイポーラ効果による影響を考慮した回路シミュレーション手法を示す。65nm プロセスのフリップフロップと論理ゲートにおけるシングルイベント効果の影響を評価する。

#### 2.1 まえがき

シミュレーションによるシングルイベント効果の評価には回路シミュレーションとデバイスシミュレーションの2種類の方法が使用されている. デバイスシミュレーションは荷電粒子の通過により生じた電子正孔対の挙動の評価に用いられる[28]. 例えばトランジスタ近傍の任意の位置に荷電粒子を通過させ, トランジスタの拡散領域に流れる電流を評価する場合に使用される[31]. 中性子線によるシングルイベント効果の場合では核反応を介して生じる. そのため粒子反応シミュレータである GEANT4 などを組み合わせてデバイスシミュレーションを行うことで, 中性子線で生じた二次イオンによる影響が評価される[56]. デバイスシミュレーションはトランジスタ単体に対するシングルイベント効果の影響を評価するのに適している. しかしシミュレーションに必要な時間が長いため, 回路全体の挙動まで評価することは困難である.

シングルイベント効果が回路の挙動に与える影響を評価する場合では、回路シミュレーションが用いられる。 荷電粒子の通過によってトランジスタに流れる電流をモデル化することで、シングルイベント効果の影響は回路モデルに組み込まれる。 回路シミュレーションはデバイスシミュレーションと比較して高速であるため、 大規模な回路でも容易にシングルイベント効果の評価が可能である。 しかし荷電粒子の通過による影響を正確

にモデル化し、回路モデルに組み込まなければ評価精度が大きく損なわれてしまう.

本章では回路シミュレーションを用いてシングルイベント効果の特性を評価し、フリップフロップや組み合わせ回路の中性子によるソフトエラーの発生率を求めた結果について報告する. 提案手法では中性子の衝突による基板電位の変動を回路モデルに組み込み、寄生バイポーラ効果による MCU などの多ビットエラーを評価可能とした. 提案手法を用いて 65nm プロセスにおけるシングルイベント効果の影響を評価した結果を報告する. フリップフロップで生じ、フリップフロップの保持データを直接反転する SEU (Single Event Upset) や、複数の保持データを反転する MCU (Multiple Cell Upset) の評価を行う. SEU とMCU の保持データ依存性や、基板電位を固定するウェルコンタクト距離依存性を評価する. また組み合わせ回路で生じる一過性の反転である SET (Single Event Transient) のパルス幅分布と駆動力依存性を評価した結果を示す.

本章の構成は以下の通りである。第2.2節では提案する中性子の衝突による基板電位の変動を考慮した回路シミュレーション方法を説明する。第2.3節では回路シミュレーションを用いてフリップフロップにおけるシングルイベント効果である SEU と MCU の特性を評価した結果を示し、第2.4節で論理ゲートの SET の特性評価結果を示す。第2.5節で回路シミュレーションによるシングルイベント効果の評価結果をまとめ、本章の結論を述べる。

# **2.2** 回路シミュレーションを用いたシングルイベント効果の 評価手法

本節では従来の回路シミュレーション手法を紹介する。次に中性子の衝突による基板電位の変動を回路モデルに組み込んだ提案方法を説明する。

#### 2.2.1 中性子起因の誘起電荷による電流

中性子が Si 原子と衝突すると二次イオンが生じ、生じた二次イオンがトランジスタの拡散領域近傍を通過すると電子正孔対が生成される。電界によって電子が引き寄せられるファネリングとドリフトによる急激な電流がトランジスタのドレイン端子に生じる。その後、拡散による電荷がドレイン端子に緩やかに流れる。

この中性子起因の誘起電荷による電流をモデル化した式は2種類ある. 文献 [32,57,58] では式 (2.1) の指数二項モデル (double exponentail model), 文献 [22,23,59,60] では式 (2.2)

の単一指数モデル (single exponentail model) が提案されている.

$$I(t) = Q \frac{\alpha \beta}{\beta - \alpha} (\exp(-\alpha t) - \exp(-\beta t))$$

(2.1)

$$I(t) = \frac{2Q}{T\sqrt{\pi}}\sqrt{\frac{t}{T}}\exp\left(\frac{-t}{T}\right)$$

(2.2)

式 (2.1) の  $\alpha$  は立ち上がりの時定数であり,  $\beta$  は立ち下がりの時定数である. 式 (2.2) の T はプロセスによって決まる時定数であり, プロセスの微細化とともに減少していくと予想されている [23]. 式 (2.1), 式 (2.2) を t=0 から  $t=\infty$  まで積分すると Q となる. この変数 Q はドレインに集められる電荷の総量を示している. 中性子線衝突により発生した二次イオンが通過したと仮定するトランジスタのドレイン端子に, 式 (2.1), または式 (2.2) のモデル式を満たす電流源を接続することで, シングルイベント効果の影響を回路モデルに組み込む. 例えば SEU の評価ではラッチなどの記憶素子を構成するトランジスタに電流源を接続し, 値が反転する最小の電荷量  $Q_{crit}$  を求める.

単位時間内に中性子が衝突して $Q_{crit}$ 以上の電荷が生じる確率は式(2.3)で表される[23].

$$N_{\rm SEU}(Q_{\rm crit}) = F \times A \times K \times \exp\left(-\frac{Q_{\rm crit}}{Q_{\rm s}}\right)$$

(2.3)

式 (2.3) は実験的に求められた式である. K は比例定数で, 文献 [23] によるとその値はプロセスによらず  $2.2\times10^{-5}$  である. F は中性子束 (Neutron Flux) であり, ソフトエラーの要因となる 10MeV 以上のエネルギーを持つ中性子に限定すると地上では 0.00565 cm $^{-2}$ s $^{-1}$  である [23]. A はソフトエラーを起こす可能性のある Jードに接続された MOS トランジスタのドレイン面積の総和であり, 単位は cm $^2$  である.  $Q_s$  は電荷収集効率 (charge collection efficiency) と呼ばれ, 単位は  $Q_{crit}$  と同じ C である.  $Q_s$  はプロセスによって決まる量であり, プロセスの微細化とともに減少していくと予想されている [23].

本論文で用いた各パラメータの値を表 2.1 にまとめる。電荷収集効率  $Q_s$  は文献 [23] で示されている  $Q_s$  の  $0.35\mu m$  プロセスの値である 35fC と,  $0.1\mu m$  プロセスの値である 13fC から線形近似して 65nm プロセスの値を決めた。文献 [23] で示されているように,電荷収集効率  $Q_s$  は nMOS トランジスタと pMOS トランジスタで異なり, $0.1\mu m$  プロセスでは nMOS トランジスタが約 13fC,pMOS トランジスタが約 6fC である。pMOS トランジスタの  $Q_s$  は nMOS トランジスタに比べて約 1/2 倍であるため,pMOS トランジスタでソフトエラーが生じにくい。本論文では回路シミュレーションの簡略化を考慮し,pMOS トランジスタではソフトエラーが生じないと仮定してシングルイベント効果を評価する。

| パラメータ        | 値                                      |

|--------------|----------------------------------------|

| 比例定数 K       | 2.2 ×10 <sup>-5</sup>                  |

| 中性子量 F       | $0.00565 \text{ cm}^{-2}\text{s}^{-1}$ |

| 電荷収集効率 $Q_s$ | 10 fC                                  |

表 2.1: 回路シミュレーションに用いた式 (2.3) のパラメータの値.

#### 2.2.2 デバイスシミュレーションの電流波形との比較

本節では式(2.1)と式(2.2)による電流の波形と、荷電粒子通過によってトランジスタの拡散領域に流れる電流をデバイスシミュレーションで評価した結果を比較する。比較することで回路シミュレーション上で中性子による励起電流が正しく表現できているかを確認するとともに、本論文の回路シミュレーションで用いる電流波形を決定する。デバイスシミュレーションには Synopsys 社の Sentaurus を用いた。ツインウェル (twin-well) 構造の p ウェル (p-well) に 2 つのラッチの nMOS トランジスタを配置したデバイスモデルを構成し、LET(Linear Energy Transfer) が 20MeV-cm/mg の荷電粒子をドレイン領域に対して垂直に入射した [61]。荷電粒子が通過した nMOS トランジスタに収集された電荷による電流波形を評価した。ドリフトやファネリング、拡散による電荷のみを評価しており、寄生バイポーラによって供給される電荷を除外している。

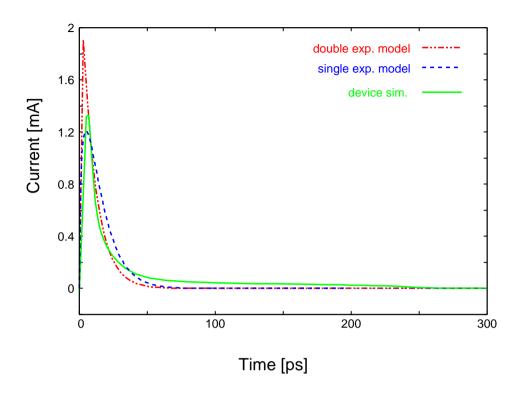

デバイスシミュレーションでの電流波形と式 (2.2), 式 (2.1) の電流波形を図 2.1 に示す. デバイスシミュレーションと比較すると, 式 (2.2) のドリフトによる急激な電流の最大値は同等である. しかし拡散による電流は大きく異なり, 式 (2.2) と式 (2.1) のモデルでは拡散による電流は短時間しか流れない. 50ps 以上では電流量がほぼ 0 となっている. 拡散による電流は SET のパルス幅に大きく寄与するため, 式 (2.2) を用いてシミュレーションを行うと SET によるエラーを過小評価することになると推測される.

拡散による電流が大きく異なる点を修正するために、時定数 T が異なる 2 つの式 (2.2) を加算した式 (2.4) を満たす電流源を使用する.

$$I(t) = 0.55 \frac{2Q}{5 \text{ps } \sqrt{\pi}} \sqrt{\frac{t}{5 \text{ps}}} \exp{(\frac{-t}{5 \text{ps}})} + 0.45 \frac{2Q}{70 \text{ps } \sqrt{\pi}} \sqrt{\frac{t}{70 \text{ps}}} \exp{(\frac{-t}{70 \text{ps}})}$$

(2.4)

第一項がドリフトとファネリングによる電流,第二項が拡散による電流に対応している. 第一項と第二項の比率は電流の最大値がデバイスシミュレーションと一致するように決

図 2.1: 粒子線による励起電流のデバイスシミュレーション結果と回路シミュレーションでの電流波形の比較.

定した. 式 (2.4) による電流波形とデバイスシミュレーションの電流波形を図 2.2 に示す. ドリフトとファネリングによる急激な電流と, 拡散による緩やかな電流が切り替わっている 120ps から 140ps の間では, デバイスシミュレーションと式 (2.4) の電流波形はやや異なる. しかしトランジスタの出力が反転するかどうかはドリフトとファネリングによる急激な電流によって決定され, 反転の持続時間は拡散による緩やかな電流の電流値によって決定される. そのため, 120ps から 140ps の間の電流波形が異なっていてもシミュレーション結果に大きな影響を与えない. 式 (2.4) を満たす電流源をインバータの出力に接続した場合のインバータの出力電圧波形を図 2.3 に示す. 式 (2.4) の Q は 35fC とし, 100ps の時に中性子が衝突したと仮定してシミュレーションを行った. 図 2.3 ではドリフトとファネリングによってインバータの出力が瞬時に反転している. 250ps 程度まではインバータの pMOS によって供給される電荷量より拡散による電荷量の方が多いため, シングルイベント効果による反転が持続している. しかし 250ps 以上になると, 拡散によって収集される電荷量が減少し, インバータの出力が元に戻る.

図 2.2: 粒子線による励起電流のデバイスシミュレーション結果と式 (2.4) による電流波形の比較.

#### 2.2.3 粒子線衝突による基板電位の変動の適用

微細化により顕在化した多ビットエラーの特性や発生率を回路シミュレーションで求めるには、多ビットエラーの発生原理である寄生バイポーラ効果や電荷共有などの影響を回路モデル内に組み込む必要がある。本論文では寄生バイポーラ効果に着目し、回路シミュレーションで評価を行う。寄生バイポーラ効果は中性子起因の二次イオン通過により生じた電荷が基板の電位を変動させることで生じる。寄生バイポーラ効果を評価するには基板電流を表現した電流源を基板の等価回路モデルに接続し、基板電流の影響と寄生バイポーラトランジスタの動作を考慮した回路シミュレーションを行う必要がある。

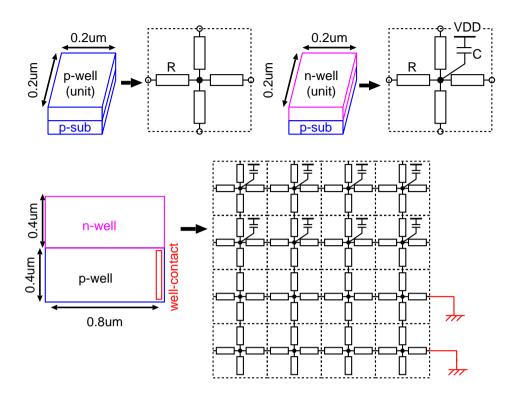

基板変動を回路モデル内に組み込むために、抵抗と容量を用いてpウェルをモデル化した. 想定する基板の構造はツインウェル構造であり、nウェルとpウェル直下にp基板 (p-sub) があるとする. また、本論文では中性子起因の二次イオンが nMOS トランジスタを通過した場合のみ回路シミュレーションで評価する. そのため、pウェルのみをモデル化する. モデル化したpウェルの単位構造を図 2.4 の上側に示す.  $0.2\mu m$  の単位領域のpウェルを、4 隣接領域それぞれへの接続抵抗 4 本でモデル化した. またnウェル

図 2.3: 式 (2.4) を満たす電流源をインバータの出力に接続した場合のインバータの出力電圧波形.

の場合ではnウェル直下に存在するpウェルのみをモデル化した. nウェル直下に存在するpウェルの場合では, 4 隣接領域それぞれへの接続抵抗 4 本に加えて, n ウェルとp ウェル間に存在する接合容量を摸擬した 1 個の容量を追加してモデル化した.

単位領域の p ウェルモデルをメッシュ状に接続することで基板全体をモデル化した. 基板全体をモデル化した回路図を図 2.4 下に示す. p ウェルはウェルコンタクトによって電位を 0V に固定されるため, ウェルコンタクトを配置した位置の単位 p ウェルモデルの位置で電位を固定している. 図 2.4 下の図では右端にウェルコンタクトを配置しているため, 右端の単位 p ウェルモデルをグラウンドに接続している.

トランジスタに寄生するソース-基板-ドレイン間のバイポーラトランジスタのモデル化は、デバイスシミュレーションの結果と単体トランジスタの測定結果を元に決定した。中性子衝突により基板に流れる電流はドレイン領域に収集される電流と等しい。よって回路モデルに基板電位の変動を組み込むために、式 (2.4) を満たす電流源を中性子が衝突したと仮定するトランジスタ直下の単位基板モデルに接続した。例として横方向にインバータを2段並べた場合の、回路シミュレーションに用いた p ウェル構造とトランジスタの接続を図 2.5 に示す。インバータの nMOS トランジスタを 3 単位 p ウェルモデル離して接続することで、0.6μm 間隔で配置された 2 つのインバータ間の距離を回路モデルで表

表 2.2: 回路シミュレーションに使用した基板モデルの抵抗と寄生バイポーラトランジスタの $\beta$ の値. 抵抗 R は図 2.4 の  $0.2\mu$ m 角の p ウェルモデルに示した R の値である.

| パラメータ  | 値      |

|--------|--------|

| 抵抗 R   | 1300 Ω |

| 電流増幅率β | 50     |

している. また右端の p ウェルモデルをグラウンドに接続することでウェルコンタクトの位置を表す. 中性子起因の二次イオンが通過したと仮定するトランジスタのドレイン端子に電流源  $I_e(t)$  を接続することで, シングルイベント効果によるトランジスタの出力の反転を摸擬した. 同様に中性子起因の二次イオンが通過したと仮定するトランジスタ直下の p ウェルモデルに電流源  $I_h(t)$  を接続し, 基板電位の変動を回路モデルに組み込んだ.  $I_e(t)$  と  $I_h(t)$  は式 2.4 を満たす電流源である.

シミュレーションに用いた基板モデルの抵抗の値と寄生バイポーラトランジスタの $\beta$  のパラメータの値を表 2.2 に示す。本章で示す回路シミュレーションでのシングルイベント効果の評価結果は標準電圧 1.2V の 65nm プロセスの結果である。抵抗は 65nm プロセスの実測結果から決定した。寄生バイポーラトランジスタの電流増幅率 $\beta$  はデバイスシミュレーションの結果から決定した。pMOS トランジスタのソース電位を 0V, ドレイン電位を 1.2V とした場合に、基板電位が 0.7V から 0.8V まで変化したときの $\beta$  をデバイスシミュレーションを用いて評価した。容量の値は n ウェルと p ウェル間ダイオードのspice モデルを参考に決定した。

#### 2.2.4 回路シミュレーションの意義と限界

回路シミュレーションではシングルイベント効果による影響を電流源や式を用いてモデル化しているため、評価精度に限界がある。シングルイベント効果によるソフトエラー率を正確に見積もるためには実際に回路を設計して測定する必要となる。測定精度に限界があるものの、回路シミュレーションを用いてシングルイベント効果を評価する意義は多数存在する。

1 つは LSI を設計する段階でソフトエラー率を見積もることが出来る点である. LSI の 回路構造を設計後に変更することは困難であるため, サーバなどの LSI を設計する場合 では回路シミュレーションによって事前にソフトエラー率を予測することが必要となる. またより耐性の高い構造を検討する場合に, 回路シミュレーションを用いて比較すると

図 2.4: p ウェルのモデル化.  $0.2\mu m$  角の p ウェルを 4 つの抵抗とし, それをメッシュ状に接続することで p ウェルをモデル化する. n ウェルの場合では, n ウェルの下に存在する p ウェルを 4 つの抵抗と, n ウェルと p ウェル間の容量 1 つでモデル化する.

高速かつ低コストで行うことが出来る. 回路シミュレーションによるシングルイベント 効果の評価結果は耐ソフトエラー LSI の設計指針となる.

回路シミュレーションではトランジスタ単位でシングルイベント効果に対する脆弱性を評価することができる点も意義として挙げられる。シングルイベント効果は確率的な現象であるため、どのトランジスタで生じたかを実際に設計した回路で評価するのは困難である。そのため、実測による評価では設計した回路のどのトランジスタに電荷が生じるとエラーとなりやすいか、MCUが原因でエラーとなっているのか、などの解析が出来ない。トランジスタ単位でシングルイベント効果に対する脆弱性を評価するにはシミュレーションによる評価が必要となる。

図 2.5: 横方向にインバータを 2 段並べた場合の, 回路シミュレーションに用いた well 構造とトランジスタの接続. 中性子が衝突したと仮定するトランジスタのドレイン端子とその直下の基板モデルに電流源を接続する.

#### 2.3 フリップフロップにおけるシングルイベント効果の評価

本節では前節で説明した回路シミュレーション方法を用いてフリップフロップのシングルイベント効果を評価した結果を報告する.

#### 2.3.1 評価に用いた回路の構造

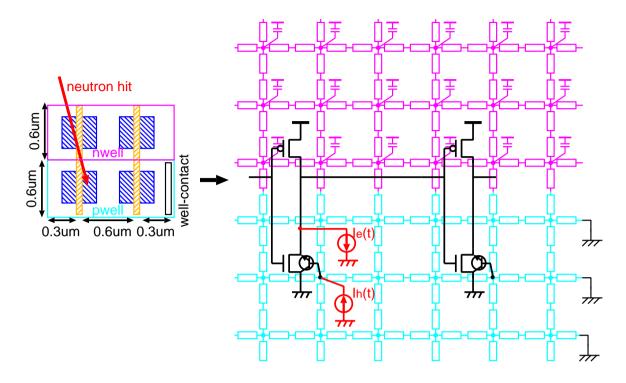

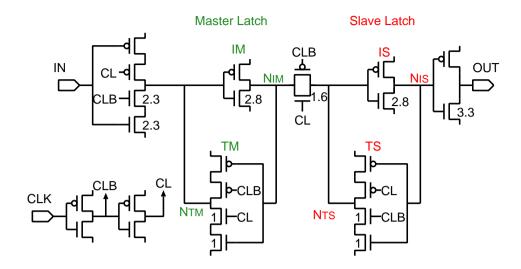

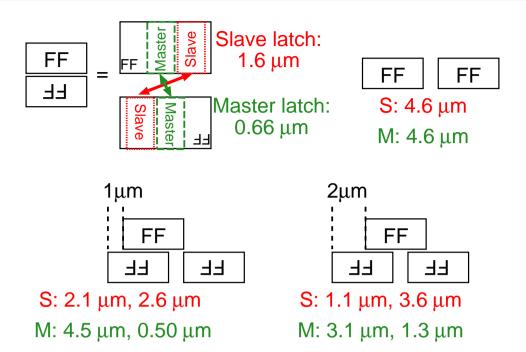

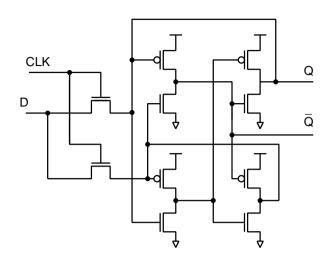

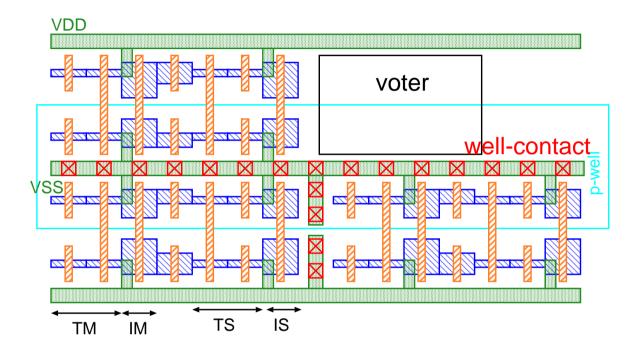

シングルイベント効果を評価するために用いたフリップフロップの構造を図 2.6 に示す. 各トランジスタの数値はトランジスタのゲート幅の比率を表す. 図 2.6 のフリップフロップは, 第 3 章で示す実測評価に用いたフリップフロップと同一の構造である. 設計したフリップフロップのレイアウトから, 各トランジスタを図 2.4 に示した p ウェルのモデル上に配置し,全てのトランジスタに寄生バイポーラトランジスタを接続した. フリップフロップは上下方向に並べて配置するが,下側のフリップフロップを上下に反転することで,それぞれの nMOS トランジスタが同一の p ウェルに収納される構造とした.

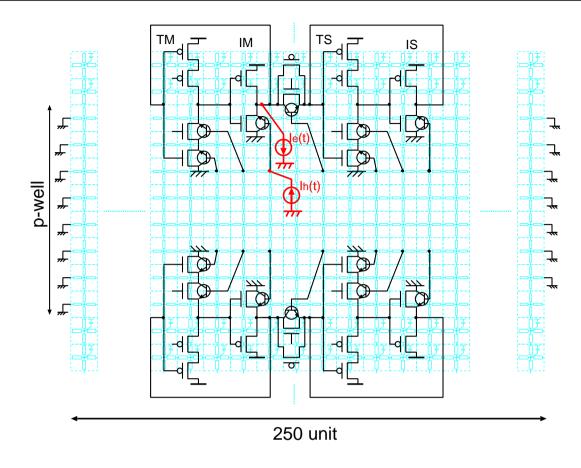

回路シミュレーションに用いたフリップフロップの配置を図2.7に示す. 図2.7では簡

図 2.6: 回路シミュレーションに用いたフリップフロップの構造. 各トランジスタの数値 は nMOS トランジスタのゲート幅の比率を表す.

略化のため、図 2.6 の IM と、TM、IS、TS、トランスミッションゲートのみ示している。ウェルコンタクトの配置間隔は  $50\mu$ m で固定している。フリップフロップとウェルコンタクト間の最小の距離をウェルコンタクト距離  $D_w$  と定義する。2 つのフリップフロップの配置を左右に移動することで  $D_w$  を変更し、MCU のウェルコンタクト距離依存性を評価した。また、フリップフロップのラッチを構成するトランジスタのチャネル間の距離をラッチ間距離 D と定義する。下側のフリップフロップを右方向にずらすことで D を変更し、MCU のラッチ間距離依存性を評価した。

回路シミュレーションに用いた図 2.7 の等価回路を図 2.8 に示す. 中性子起因の二次イオンが通過したと仮定する nMOS トランジスタのドレイン端子と, そのトランジスタ直下のウェル抵抗に式 (2.4) の電流源をそれぞれ接続する. 片方のフリップフロップが反転する電荷量  $Q_{MCU}$  を評価した. なお, 上側のフリップフロップの nMOS トランジスタに中性子起因の二次イオンが通過した場合のみを想定してシミュレーションを行った. そのため, 下側のフリップフロップは基板電位の変動の影響のみを受ける.

図 2.7: 回路シミュレーションに用いたフリップフロップの配置. 下側のフリップフロップは p ウェルを共有するために上下反転している.  $D_w$  はウェルコンタクトとフリップフロップの最小距離を示し, D はラッチ間距離を示す.

#### 2.3.2 保持データとクロック信号依存性

SEU の保持データとクロック信号依存性

クロック信号値および保持データのそれぞれが0および1である場合の4通りについて、SEU が生じる電荷量  $Q_{\text{SEU}}$  と MCU が生じる電荷量  $Q_{\text{MCU}}$  を求めた結果を表 2.3 に示す. 比較のために基板電位の変動を考慮しない既存手法を用いてシミュレーションした結果も示す. ラッチ間距離はフリップフロップを上下に揃えて並べた場合の $0.6~\mu\text{m}$ 、ウェルコンタクト距離は $20~\mu\text{m}$  とした.

SEU は保持データに大きく依存する結果となっている. ラッチを構成するインバータの出力が1の場合に,中性子によって28 fC 以上の電荷が生じると, SEU は発生しない. この原因は中性子の衝突によって導通した TM や TS に寄生するバイポーラトランジスタにより, 反転したインバータの出力がトライステートインバータの出力に伝播するのが防止されるためである[62].

この寄生バイポーラトランジスタによる反転値の伝搬が防止される現象を図 2.8 に示す回路シミュレーションモデルを用いて解析する. クロック信号を1に固定してマスターラッチをデータ保持状態とする. 保持データは2 つのフリップフロップをともに1とし.

図 2.8: 回路シミュレーションに用いた図 2.7 の等価回路.

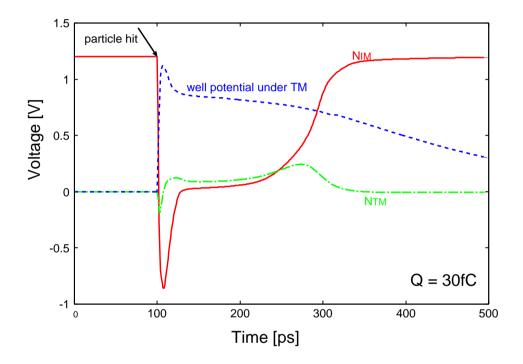

ウェルコンタクト距離  $D_{w}$  は  $20~\mu m$  とした. 図 2.8 の IM の出力にシングルイベントにより総電荷量 30~fC の電荷注入が発生した場合のノード  $N_{IM}$  とノード  $N_{TM}$ , 及び TM 直下における p ウェルの電位変動をシミュレーションした結果を図 2.9 に示す. 中性子線がマスターラッチのインバータ IM に衝突したことにより, IM の出力  $N_{IM}$  は 1~h 5~0~h 6~0~h 1~0~0~h 1~0~h 1~0~0~h 1~0~h 1~0~0~h 1~0

次に保持データが0の場合, すなわち $N_{TM}$ が1の場合に, 中性子起因の二次イオンが

表 2.3: 保持データ, クロック信号の違いによる SEU, MCU が生じる電荷量  $Q_{\text{SEU}}$ ,  $Q_{\text{MCU}}$ の変化. ラッチ間距離 =  $0.6~\mu\text{m}$ , ウェルコンタクト距離 =  $20~\mu\text{m}$  の場合.

|        |       | 基板電位の変動なし             | 基板電位の変動あり               |                   |

|--------|-------|-----------------------|-------------------------|-------------------|

| クロック信号 | 保持データ | Q <sub>SEU</sub> [fC] | $Q_{\mathrm{SEU}}$ [fC] | $Q_{ m MCU}$ [fC] |

| 1      | 0     | 2.2                   | 2.2                     | 40                |

|        | 1     | 14                    | 13 – 27                 | No Error          |

| 0      | 0     | 11                    | 9 – 22                  | No Error          |

|        | 1     | 2.0                   | 2.0                     | 40                |

図 2.9: 寄生バイポーラトランジスタによる反転値の伝播防止. 寄生バイポーラトランジスタによって  $N_{TM}$  が反転せず,  $N_{IM}$  は元の値に戻る.

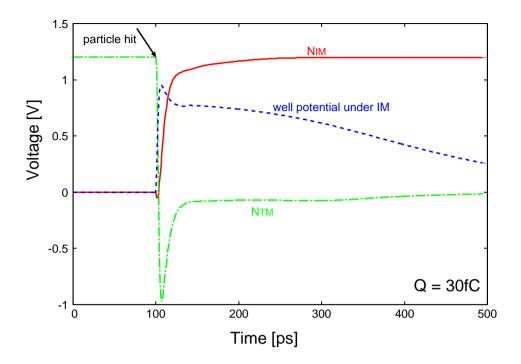

TM を通過したと想定する回路シミュレーションの結果を図 2.10 に示す. 駆動力の大きい IM は基板電位が上昇しても、出力である  $N_{IM}$  は IM に寄生するバイポーラトランジスタによって0 に固定されない. そのため、 $N_{TM}$  が0 に反転すると、 $N_{IM}$  は0 から1 に反転する.  $N_{TM}$  が1 の場合では基板電位が変動しても SEU が発生する.

図 2.10: 寄生バイポーラトランジスタによる反転値の伝播防止が発生しない場合. 基板電位が変動しても, 駆動力の強いインバータの出力である  $N_{\rm IM}$  は反転する.

#### MCU の保持データ依存性

クロック信号を 1 に固定して、2 つのフリップフロップの保持データがそれぞれ 0 および 1 である場合の 4 通りについて、MCU が生じる電荷量  $Q_{MCU}$  を求めた結果を表 2.4 に示す.

MCU の保持データ依存性は SEU よりも顕著であり、2 つのフリップフロップの保持データが 0 場合のみ、MCU が生じた.この原因は SEU と同じく寄生バイポーラトランジスタによってフリップフロップの値の反転が防止されるためである.保持データが 1 の場合では寄生バイポーラトランジスタによって値の反転が防止され、電荷量 Q が 28fC 以上では反転しない.一方で保持データが 0 の場合では基板電位の変動により、フリップフロップの保持データは反転する.しかし、基板電位の変動によって値が反転するには 40fC 以上必要である.そのため、上側のフリップフロップの保持データが 1 の場合では、下側のフリップフロップが反転しても、上側のフリップフロップは寄生バイポーラ効果によって値の反転が防止されるため、上側のフリップフロップの保持データは反転しない.以上により、2 つの保持データが 0 である場合以外では、MCU が生じない.

| 上側のFFの | 下側のFFの |                   |

|--------|--------|-------------------|

| 保持データ  | 保持データ  | $Q_{ m MCU}$ [fC] |

| 1      | 0      | No Error          |

|        | 1      | No Error          |

| 0      | 0      | 40                |

|        | 1      | No Error          |

表 2.4: MCU が生じる電荷量  $Q_{\mathrm{MCU}}$  の保持データ依存性.

表 2.5: 保持データ, クロック信号の違いによる SEU 発生率と MCU 発生率の変化. ラッチ間距離が  $0.6~\mu m$ , ウェルコンタクト距離が  $20~\mu m$  の場合. 発生率の単位は [FIT/Mbit] で示す.

| クロック |       | 基板電位の変動なし | 基板電位の   | の変動あり   |

|------|-------|-----------|---------|---------|

| 信号   | 保持データ | SEU 発生率   | SEU 発生率 | MCU 発生率 |

| 1    | 0     | 241       | 241     | 5.3     |

|      | 1     | 131       | 109     | 0       |

| 0    | 0     | 64        | 57      | 0       |

|      | 1     | 204       | 204     | 4.6     |

### SEU 発生率と MCU 発生率

$Q_{SEU}$  と  $Q_{MCU}$  を式 (2.3) に代入して計算した SEU 発生率と MCU 発生率を表 2.5 に示す. MCU の発生率は SEU 発生率の約 1/50 となった. この結果から三重化フリップフロップのエラー耐性は MCU により減少し, 通常のフリップフロップの 50 倍程度になると推測される. SEU 発生率では保持データによって 4 倍程度変化する. 基板電位の変動を考慮しない既存手法と提案手法を比較すると, SEU 発生率はほぼ等しい結果となった. 寄生バイポーラトランジスタによって保持データの値の反転が防止されるが, SEU の発生率には大きな影響を与えない.

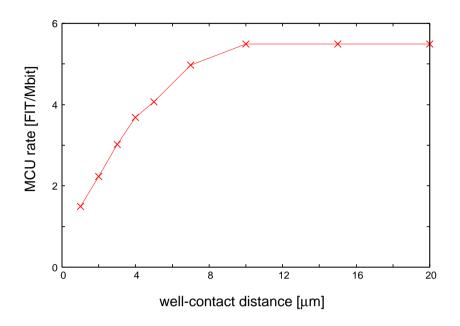

# 2.3.3 ウェルコンタクト距離依存性

ウェルコンタクトからフリップフロップまでの距離  $D_w$  (図 2.7 参照) を変更した場合の,  $Q_{\text{SEU}}$  と  $Q_{\text{MCU}}$  の変化を表 2.6 に示す. ウェルコンタクト距離に対する MCU 発生率の変化を図 2.11 に示す. ただし,  $D_w$  が  $0.3\mu\text{m}$  の場合のみウェルコンタクトの配置方法が異

表 2.6: ウェルコンタクト距離  $(D_w)$  を変更した場合の,  $Q_{SEU}$  と  $Q_{MCU}$  の変化. ウェルコンタクトを距離を  $0.3\mu m$  とした場合のみ上下に配置したフリップフロップ間にウェルコンタクトを配置した場合である.

| ウェルコンタクト距離 [μm]      | $Q_{ m SEU}$ [fC] | $Q_{ m MCU}$ [fC] |

|----------------------|-------------------|-------------------|

| 1                    | 2.2               | 53                |

| 2                    | 2.2               | 49                |

| 3                    | 2.2               | 46                |

| 4                    | 2.2               | 44                |

| 5                    | 2.2               | 43                |

| 7                    | 2.2               | 41                |

| 10                   | 2.2               | 40                |

| 15                   | 2.2               | 40                |

| 20                   | 2.2               | 40                |

| 0.3(上下のフリップフロップ間に配置) | 2.2               | No Error          |

なる. 図 2.7 に示した上下のフリップフロップの間にのみウェルコンタクトを配置した場合である. クロック信号は 1, 保持データは 0, ラッチ間距離を  $0.6\mu m$  として MCU が生じやすい条件で評価した.

$Q_{\rm SEU}$  はウェルコンタクト距離にかかわらず一定である. SEU は 2.2 fC と低い電荷で SEU が生じている. SEU の場合では寄生バイポーラ効果による電荷供給がなくても値が 反転するため,  $Q_{\rm SEU}$  はウェルコンタクト距離に依存しないと推測される

一方で  $Q_{\rm MCU}$  ではウェルコンタクト距離  $D_w$  が  $0.3\mu{\rm m}$  の場合には、上下に配置したフリップフロップ間にウェルコンタクトを配置しており、基板電位の変動がもう片方のフリップフロップに伝播しない。そのため、MCU が生じない結果となった。多重化フリップフロップのフリップフロップを上下に配置し、その間にウェルコンタクトを挿入することで、多重化フリップフロップのエラー耐性が大きく向上すると推測される。一方でウェルコンタクトをフリップフロップの横に配置する場合、ウェルコンタクトの距離が  $7\mu{\rm m}$  以下の領域では MCU 発生率はおおよそ線形に減少している。しかし、ほぼ隣接して配置している  $D_w=1$   $\mu{\rm m}$  でも MCU 発生率は 0 とはならず、 $D_w=20$   $\mu{\rm m}$  の 1 / 4 程度にしか減少しない。フリップフロップに隣接してウェルコンタクトを配置しても、マスターラッチはフリップフロップの中央部分にあるため、ウェルコンタクト距離が  $1\mu{\rm m}$  離れてしまうことが原因であると推測される。

図 2.11: クロック信号を 1 に固定し, 2 つのフリップフロップの保持データを両方とも 0 とした場合の, MCU のウェルコンタクト間距離依存性.

# 2.3.4 ラッチ間距離依存性

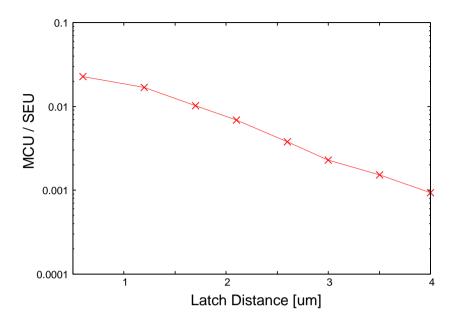

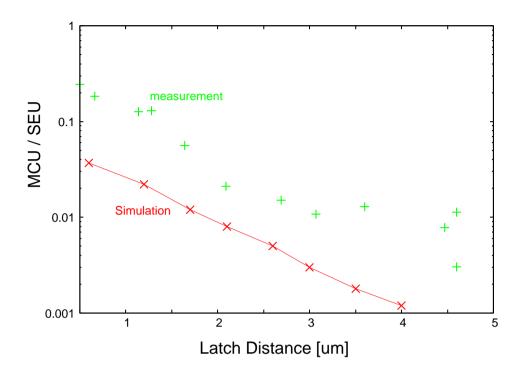

MCU のラッチ間距離依存性を図 2.12 に示す. MCU の割合を示す MCU / SEU はラッチ間距離に対して指数で減少している. しかしその傾きは緩やかであり,  $0.6\mu m$  から  $3\mu m$  に離しても 1/10 しか減少しない. 多重化フリップフロップのラッチ間距離を  $2\mu m$  ほど離さなければ、通常のフリップフロップの 100 倍のエラー耐性は実現できない.

# 2.4 論理ゲートにおけるシングルイベント効果の評価

本節ではフリップフロップと同様に、回路シミュレーションを用いてインバータのシングルイベント効果を評価した結果を報告する.

## 2.4.1 評価に用いた回路の構造

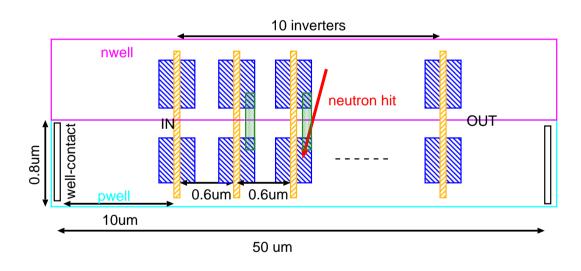

論理ゲートにおけるシングルイベント効果である SET の評価には 10 段のインバータチェインを用いた. 標準の駆動力を持つインバータチェインの配置を図 2.13 に示す. インバータを  $0.6\mu$ m 間隔で 10 段配置し,入力 IN を 0 に固定した. 3 番目のインバータに中性子線が衝突したと仮定してシミュレーションを行い,出力 OUT のパルス幅を測定した.

図 2.12: クロック信号を 1 に固定し, 2 つのフリップフロップの保持データを両方とも 0 とした場合の, MCU/SEU のラッチ間距離依存性.

図 2.13: 回路シミュレーションで用いた駆動力 1x のインバータチェインの配置.

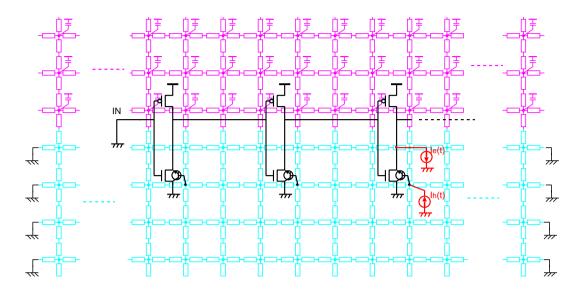

ウェルコンタクトは  $50\mu$ m 間隔で配置し、最初のインバータとは  $10\mu$ m 離して配置した. 回路シミュレーションで用いた図 2.13 の等価回路モデルを図 2.14 に示す. 中性子起因の二次イオンが通過したと仮定する 3 段目のインバータの nMOS トランジスタのドレイン端子と、その直下の p ウェル抵抗に式 (2.4) の電流源をそれぞれ接続した. 生じた SETのパルス幅と、収集された電荷量 Q の関係を評価した.

図 2.14: 回路シミュレーションで用いた図 2.13 の等価回路モデル

# 2.4.2 駆動力に対する SET 発生率の変化

駆動力が標準, 2 倍, 4 倍, 16 倍のインバータチェインで 40ps 以上の SET が生じる最小電荷量  $Q_{40ps}$  と SET 発生率を表 2.7 に示す. 40ps はフリップフロップに取り込まれる最小のパルス幅であり, 式 (1.1) のラッチ保持制約 w の値と等しい.

基板電位の変動を考慮しない既存手法では駆動力の増加に対して $Q_{40ps}$ が線形に増加する。駆動力の増加に対し、負荷容量は線形に増加するため、出力を反転するために必要な電荷量も線形に増加することが原因と考えられる。一方で基板電位の変動を考慮した提案手法では $Q_{40ps}$  は駆動力の増加に従って増加するものの、駆動力の増加量に比べて $Q_{40ps}$  の増加量は少ない。トランジスタ数の多い駆動力が4倍などのインバータでは、寄生バイポーラ効果による電荷の収集量が増加するためと推測される。 $Q_{40ps}$  と式 (2.3) から計算した SET 発生率では、4倍の駆動力を持つインバータと 2 倍の駆動力を持つインバータの SET 発生率の差が小さい。 $Q_{40ps}$  の増加による発生率の減少を、ドレインの面積増加による中性子衝突確率の増加で打ち消しているためである。寄生バイポーラ効果によって駆動力増加による SET 発生率の低減効果は小さくなり、クロックツリーなどを構成する駆動力の大きいインバータでも SET が生じることが分かる。

| $\boldsymbol{z}$ -ops $\boldsymbol{z}$ |                                  |                      |                                  |                      |

|----------------------------------------|----------------------------------|----------------------|----------------------------------|----------------------|

|                                        | 基板電位の変動なし                        |                      | 基                                | 板電位の変動あり             |

| 駆動力                                    | $Q_{40\mathrm{ps}}[\mathrm{fC}]$ | SET 発生率 [FIT/M inv.] | $Q_{40\mathrm{ps}}[\mathrm{fC}]$ | SET 発生率 [FIT/M inv.] |

| 1x(標準)                                 | 16                               | 33                   | 15                               | 37                   |

| 2x                                     | 34                               | 6.9                  | 24                               | 17                   |

| 4x                                     | 68                               | 0.4                  | 36                               | 11                   |

| 16x                                    | 323                              | 1×10 <sup>-12</sup>  | 78                               | 0.68                 |

表 2.7: 駆動力に対する SET 発生率の変化. Q<sub>40ps</sub> は 40 ps 以上の SET が生じる最小電荷量.

# 2.4.3 SET のパルス幅分布

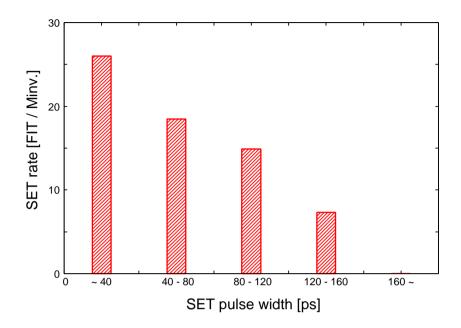

標準の駆動力を持つインバータのパルス幅分布を図 2.15 に示す. 1-40ps のパルス幅の SET が生じる電荷量 Q の範囲を回路シミュレーションで求め, 式 (2.3) を用いて 1ps から 40ps までの SET の発生率を計算した. 同様の方法で各パルス幅範囲の SET 発生率を求め, 求めた SET 発生率を図 2.15 に示す.

SET のパルス幅が大きくなるほど発生率が低くなっており、160ps 以上の SET はほとん ど発生しない. 今回のシミュレーションではインバータの間隔を 0.6µm としているため, 基板電位の影響を次段のインバータも受ける. その結果、SEU のシミュレーション結果の ように値の反転が伝播しない状態になり、インバータチェインの出力における SET のパ ルス幅が小さくなる. このパルス幅が減少する効果はパルス幅縮減効果 (pulse quenching) と呼ばれる [63]. パルス幅縮減効果のシミュレーション結果を図 2.16 に示す. 30 fC の電 荷が 1x インバータの出力に収集された場合のインバータの出力と、次段のインバータの 出力、次段のインバータ直下の基板電位を図2.16に示している。中性子起因の二次イオン が通過したインバータに生じた SET のパルス幅は 110ps である. しかし次段のインバー タの出力のパルス幅はパルス幅縮減効果によって80psに減少している.パルス幅縮減効 果はインバータが隣接して配置されている場合のみ生じる. インバータの配置間隔を変 更し,  $0.6\mu$ m から  $5\mu$ m とした場合ではパルス幅縮減効果は発生しない.  $5\mu$ m 間隔でイン バータを配置した場合のインバータの出力波形と次段の出力波形、次段のインバータ直 下の基板電位を図 2.17 に示す. 図 2.17 では生じた電荷量は図 2.16 と同じく 30fC として おり、異なる点はインバータの配置間隔のみである、次段のインバータはパルス幅縮減効 果を受けず、入力の SET と同一のパルス幅の SET が出力に伝搬している.

図 2.15: 標準の駆動力を持つインバータのパルス幅分布. 160ps 以上の SET はほとんど生じない

図 2.16: 30 fC の電荷が収集された場合の, 駆動力 1x インバータの出力と基板電位の値. 基板電位の変動により, 100ps 以上の SET パルスが次段のインバータに伝播せず, パルス幅が減少する.

2.5. まとめ 41

図 2.17:  $5\mu$ m 間隔でインバータを配置した場合の SET パルスの伝搬. パルス幅縮減効果は生じない.

# 2.5 まとめ

本章では寄生バイポーラトランジスタを含んだ基板部分の等価回路を用いた回路シミュレーションによりシングルイベント効果の評価を行った. 従来の手法ではドリフトや拡散によってトランジスタのドレイン領域に流れる励起電流のみを考慮してシングルイベント効果を評価していた. 提案手法では多ビットエラーを引き起こす寄生バイポーラ素子を基板等価回路に組み込むことで、寄生バイポーラ効果の影響を考慮可能とした.

65nm プロセスで用いるフリップフロップを想定し、このフリップフロップで生じる SEU と MCU の評価を行った。MCU と SEU の発生率はともに保持データに強く依存する。 ラッチを構成するインバータの出力が 1 の場合、基板電位の変動がラッチが保存する データの反転を防止する方向に働くことが判明した。MCU に関して、ラッチ間距離依存性やウェルコンタクト距離依存性も評価した。MCU 発生率はラッチ間距離に対して指数関数的に減少し、MCU の発生率を SEU の 1/100 にするにはラッチ間距離を  $2 \mu m$  程度離す必要がある。 また、上下に配置したラッチ間にウェルコンタクトを配置することで、MCU の発生率は 0 となった。 ソフトエラー率を向上させるには寄生バイポーラ効果を考慮した設計が必要となる。 同様にしてインバータで生じる SET の発生率やパルス幅の評価を行った。 駆動力が大きいインバータでも寄生バイポーラトランジスタにより SET が

生じることを確認した. 寄生バイポーラ効果は SET の発生率にも影響を与える. SEU の 場合でも、SEUの発生を防止する方向に働く場合があり、単一ビットエラーの影響を評価 する場合でも重要となる.

# 第3章

# 加速試験を用いたシングルイベント効果の 特性評価

本章では加速試験を用いてシングルイベント効果を測定した結果を報告する. フリップフロップにおける SEU 発生率と MCU 発生率の測定結果を示し, 次にインバータにおける SET のパルス幅分布測定結果を示す.

# 3.1 まえがき

第2章では寄生バイポーラ効果の影響を回路モデルに組み込み,シングルイベント効果の特性を回路シミュレーションを用いて評価した.寄生バイポーラ効果が多ビットエラーだけでなく、単一ビットエラーにも影響を与えていることを示した.

本章では実際に設計した LSI に中性子線を照射することで、フリップフロップの SEU や MCU 発生率を測定し、SEU や MCU の特性を明らかにする. 同時にパルス幅測定回路を用いてインバータチェインの SET パルス幅の測定を行う. 加速試験であるものの、地上でのエネルギースペクトルと同等の中性子線を照射することで、実際の使用環境でのエラー率を推測する. 照射する中性子は地上の中性子のエネルギースペクトルと同様の分布を持つため、測定された SEU 発生率などの値は実際に使用される環境でのエラー率と近い値となる. 回路シミュレーションを用いて評価したシングルイベント効果の特性を実測を用いて同様に評価し、ソフトエラーを低減する手法を検討する.

中性子線を用いた加速試験を行う場合では、ヘリオトロンなどの加速器を用いるため、中性子線を照射する時間が制限される. 短時間でより多くの測定結果を得るために、省面積な評価回路が必要とされる. 本章では最初にシングルイベント効果の特性を評価する回路構造を説明する. 次に加速試験を用いてシングルイベント効果の特性を評価した結

果を示す.

# **3.2** フリップフロップにおけるシングルイベント効果の特性 評価

本節ではフリップフロップにおけるシングルイベント効果である, SEU と MCU の特性を加速試験を用いて評価した結果について報告する. フリップフロップのデータを保持するループ構造に中性子線が衝突し, 保持データを直接反転させるソフトエラーを測定対象とする. クロック部分で生じた SET によってフリップフロップが誤動作する現象は測定対象に含まない.

# 3.2.1 シフトレジスタを用いた評価手法

フリップフロップにおけるシングルイベント効果の測定にはシフトレジスタ構造が主に用いられる [37]. 保持データの書き込み時にはクロック信号を入力し、中性子線照射時にはクロック信号を "0" または "1" に固定する. これにより粒子線によって反転した値をフリップフロップに保持させることができる. 粒子線照射後に再びクロック信号を入力することでフリップフロップの保持データを読み出し、初期値と比較することで SEU の発生数やその発生位置を取得できる.

加速試験時にはクロック信号を入力していないため、論理回路で生じる SET はフリップフロップに取り込まれない。また全てのフリップフロップを同じ値に初期化する場合では、クロックツリーで SET が生じてもフリップフロップの保持値は反転しない。以上により、SET によるエラーを無視した測定が行える。フリップフロップで生じるシングルイベント効果のみの測定が可能となる。またシフトレジスタでは発生位置も取得可能であるため、隣接する複数のフリップフロップが同時に反転する MCU に関しても測定可能である。

# 3.2.2 フリップフロップにおけるシングルイベント効果の特性評価回路 特性評価回路の目的

測定に用いた特性評価回路の主な目的を以下に示す。

● フリップフロップにおける SEU の発生率を実測で評価し、フリップフロップにおけ

る SEU が LSI の信頼性に与える影響を評価する.

- フリップフロップにおける MCU の発生率を測定し, 多重化回路のソフトエラー率を推測する.

- ラッチ (フリップフロップ) 間距離を変更した回路を測定することで, MCU のラッチ (フリップフロップ) 間距離を変更した回路の MCU 低減手法を検討する.

- 寄生バイポーラ効果が SEU と MCU の発生に与える影響を評価する. そのために、 基板電位を固定するウェルコンタクトの密度 (距離) の異なるフリップフロップを 試作し、SEU と MCU の発生率を比較する.

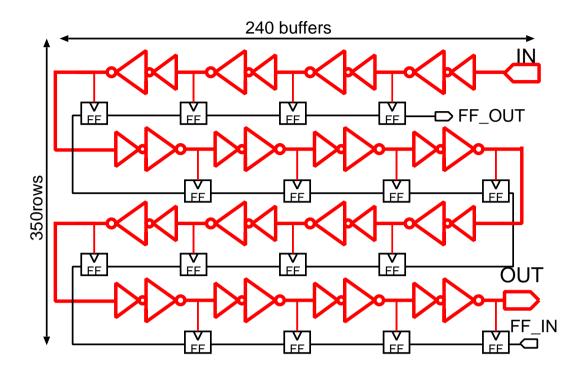

#### 評価回路の構造

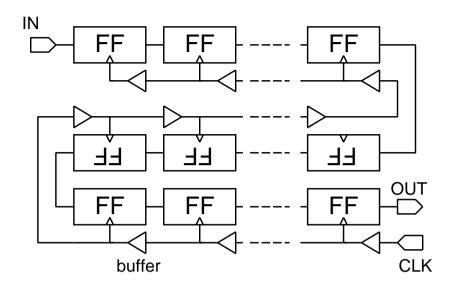

フリップフロップにおけるシングルイベント効果の特性を実測評価するために,図3.1 に示すシフトレジスタを試作した[64]. 評価回路は同数のフリップフロップとバッファで構成されており,クロック信号はバッファチェインを用いて出力側のフリップフロップから供給される構造とした.クロック信号の供給にクロックツリーを用いず,バッファチェインを用いた理由を以下に示す.

- クロックスキューにより、クロック信号が遷移するタイミングがフリップフロップ間でずれると、正しく動作しない場合がある[65]. フリップフロップにクロック信号が入力されて出力の値が変化する前に、後段のフリップフロップにクロック信号が入力されないと、正しい値を保持できない. 必ず後段のフリップフロップからクロック信号が入力されるように、バッファチェインを用いた.

- クロックスキューを考慮せずに配置できるため、フリップフロップを規則的に配置しやすい. 規則的に配置したシフトレジスタではフリップフロップ間の距離が一定となり、MCUのフリップフロップ間距離依存性の測定が容易となる.

- バッファチェインで生じた SET のパルス幅を測定可能となる. 詳細は 3.3.3 節で説明する.

図 3.1: 測定に用いたシフトレジスタの構造 [64]. 最後段からクロック信号を供給することで、クロックスキューによる誤動作を防いでいる.

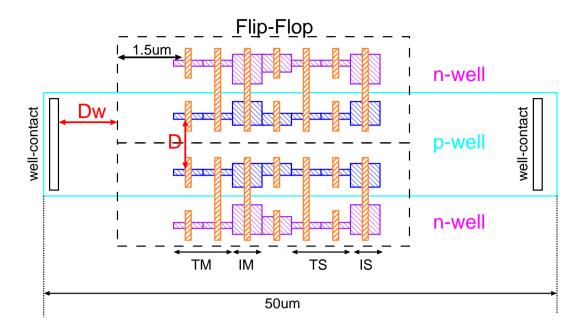

# フリップフロップの配置とウェルコンタクトの配置

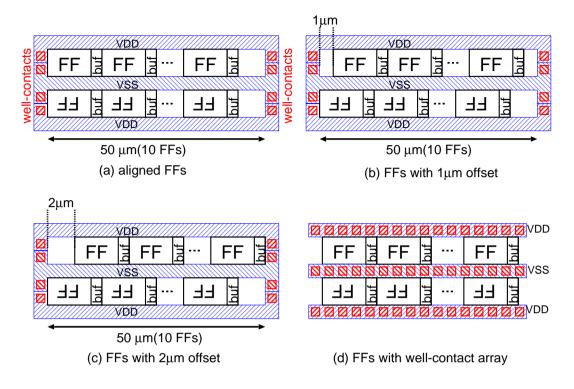

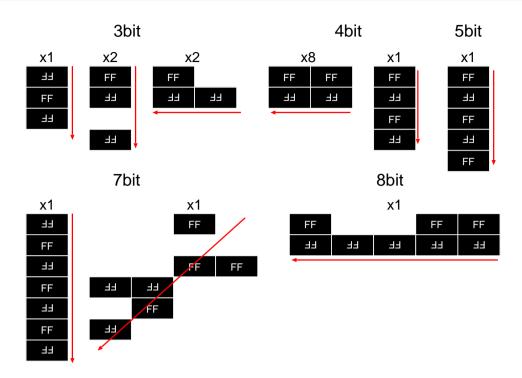

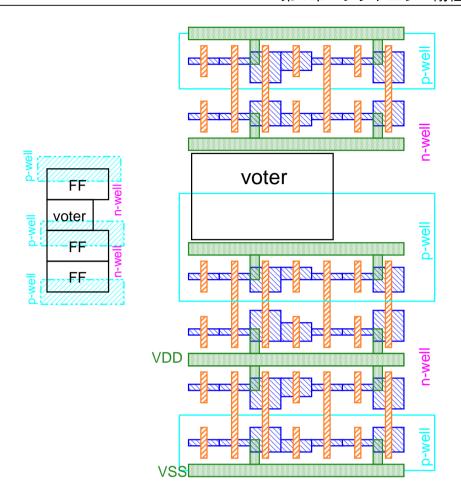

図 3.1 のシフトレジスタを図 3.2 に示すように配置した. 図 3.2 の (b) と (c) では偶数行のフリップフロップをそれぞれ  $1\mu$ m と  $2\mu$ m だけ離して配置している. 離して配置することで上下方向と斜め方向のフリップフロップ間距離を変更した. 図 3.2 の (a) がら (c) までのシフトレジスタにおけるマスターラッチ間距離とスレイブラッチ間距離の種類を図 3.3 に示す. 生じた MCU の形状ごとに発生率を求めることで, MCU のラッチ間距離依存性を  $0.5\mu$ m から  $4.6\mu$ m の範囲で 12 点測定できる.

ウェルコンタクト密度依存性を測定するために、図 3.2 (d) のシフトレジスタを試作した. (d) のシフトレジスタではウェルコンタクトの挿入方法が異なり、電源 (VDD) とグラウンド (VSS) の配線直下に配置した. 一方で (a) から (c) までのシフトレジスタではウェルコンタクトを 50µm (10 フリップフロップ) ごとに配置しており、ウェルコンタクトの挿入した間隔や個数、位置が異なる. 単位面積あたりのウェルコンタクトの挿入個数を密度と定義すると、(d) のシフトレジスタのウェルコンタクト密度は、(a) から (c) までのシフトレジスタの約 60 倍である. フリップフロップの配置 (ラッチ間距離) が等しい (a) と (d) のMCU 発生率を測定し、その発生率を比較する. それによりウェルコンタクト密度によるMCU 発生率の変化を取得し、寄生バイポーラが MCU の発生率に与える影響を評価する.

図 3.2: シフトレジスタの配置とウェルコンタクトの構造.

# 3.2.3 加速試験によるシングルイベント効果の評価方法

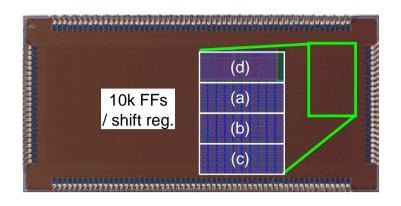

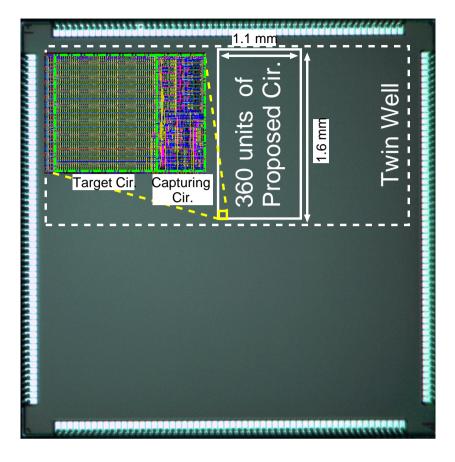

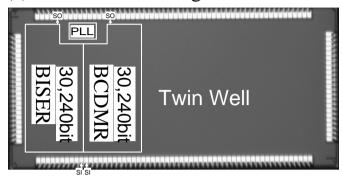

中性子線を照射してフリップフロップのシングルイベント効果を評価するために、図 3.4 に示すチップを試作した. 設計には 65nm、ツインウェル構造のバルク CMOS プロセスを用いた. 標準電源電圧は 1.2V である. 2.1mm × 4.2mm のチップに、図 3.2 の (a)–(d) を各 10,000(縦 100 行 × 横 100 列) 段試作した. 設計に用いたフリップフロップの構造は、第 2 章の回路シミュレーションに使用した図 2.6 の構造と等しい. シフトレジスタ (d) ではウェルコンタクトを左右方向に配置していないため、横幅が他のシフトレジスタよりも約 10%小さくなっている.

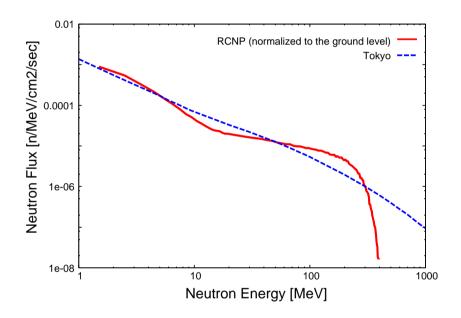

シングルイベント効果を実測評価するため、試作したチップに白色中性子ビームを照射する加速試験を行った。加速試験は大阪大学の核物理研究センター (Research Center for Nuclear Physics: RCNP) で行った。本実験の加速係数は約 $3.7 \times 10^8$  であり、加速試験の1 秒は実環境の約12年に相当する。照射した白色中性子ビームのエネルギースペクトルを図3.5に示す。地上でのエネルギー分布と比較すると、300MeV 以下では良く一致する分布を持つことが分かる。

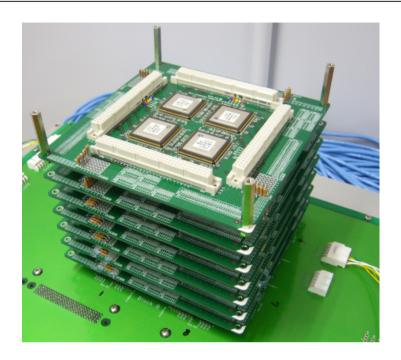

短時間でより多くの SEU と MCU を測定するために. DUT ボードを 7 段積みにして測

図 3.3: 図 3.2 の (a) - (c) のシフトレジスタにおけるラッチ間距離の種類. 簡略化のためバッファは省略している.

定した. 測定に用いた 7 段積みの DUT ボードを図 3.6 に示す. 1 つの DUT ボードには 4 つチップが実装されており, 合計で 28 チップを同時に測定した. よって各シフトレジスタで 280,000 個, 合計で 1,120,000 個のフリップフロップを測定している. 7 段積みの DUT ボードは, 中性子線の入射方向に対して垂直に配置した. 中性子線が入射する照射口と DUT の位置関係を図 3.7 に示す. 試作チップの制御には LSI テスタを用いている. LSI テスタでシングルイベント効果が生じないように, 中性子ビームの射出口から 2m 以上離して LSI テスタを配置した. 中性子照射実験時の測定の手順を以下に示す.

- 1. 全てのシフトレジスタを "0" または "1" で初期化する.

- 2. クロック信号を"0"または"1"で固定し、5分間待つ.

- 3. クロック信号を入力してシフトレジスタの保持データを読み出し、初期値と比較する.

- 4.1.に戻る.

保持データが反転したフリップフロップのうち、隣接したフリップフロップも同様に反転していた場合ではMCUによる反転とした。隣接したフリップフロップが反転していない場合ではSEUによる反転と分類してSEU、MCU発生率等を決定した。

図 3.4: 65nm プロセスを用いて試作したチップの顕微鏡写真. 図 3.2(a) - (c) を各 10,000 段搭載している.

図 3.5: 測定に用いた白色中性子線のエネルギースペクトル.

# 3.2.4 中性子線による評価結果

本節ではフリップフロップにおける中性子線起因のシングルイベント効果の測定結果を示す. MCU 発生数では同時に反転した個数に関わらず 1 として定義する. また SEU 発生数は MCU 発生数を含んだ値を示している. 例えば 3 つの隣接したフリップフロップが同時に反転していた場合, MCU 発生数と SEU 発生数は共に 1 となる. MCU / SEU の割合が最大で 100%になるように設定するためである.

図 3.6: 7 段積み DUT ボード. 1 つの DUT ボードには4 つチップが実装されている.

図 3.7: ビーム射出口と DUT ボードの配置.

# SEU と MCU の発生数とウェルコンタクト密度依存性

フリップフロップの保持データを "0" に初期化し, クロック信号を "1" に固定した場合の SEU 発生数と MCU 発生数を表 3.1 に示す. 51 回の測定結果を合計した結果である.

表 3.1: フリップフロップの保持データを "0" に初期化し, クロック信号を "1" に固定した場合の各シフトレジスタの SEU 発生数と MCU 発生数. 51 回の測定結果を合計した値である.

| 9.      |         |         |         |           |

|---------|---------|---------|---------|-----------|

|         | 最小ラッチ間  |         |         | MCU / SEU |

| シフトレジスタ | 距離 [µm] | SEU 発生数 | MCU 発生数 | [%]       |

| (a)     | 0.66    | 617     | 110     | 17.8      |

| (b)     | 0.5     | 631     | 148     | 23.4      |

| (c)     | 1.3     | 654     | 91      | 13.9      |

| (d)     | 0.66    | 498     | 1       | 0.2       |

|         |         |         |         |           |

MCU はフリップフロップでも生じており、MCU / SEU は最大で 23.4%となった. 65nm プロセスでは三重化フリップフロップなどの多重化回路のエラー耐性が MCU によって 減少していると推測される. 多重化回路を構成するフリップフロップを上下に並べて設計した場合では、多重化回路のソフトエラー耐性は非冗長化フリップフロップの 4 倍程度まで減少する場合が生じる.

基板電位を固定するウェルコンタクトを密に配置したシフトレジスタ (d) では MCU の発生数はわずか 1 であり、MCU / SEU は 0.2%と極めて小さい. フリップフロップの配置方法が等しいシフトレジスタ (a) と比較すると、MCU の発生率は 1/110 である. 基板電位を固定するウェルコンタクトを挿入することで 99%の MCU が除去されている. シフトレジスタ (a) のフリップフロップで生じた MCU の 99%が基板電位の変動による寄生バイポーラ効果によって生じていると推測される. 第 2 章で示した寄生バイポーラ効果のみを考慮した回路シミュレーション結果の妥当性を示しており、第 2.3.3 節のシミュレーション結果は、フリップフロップ間にウェルコンタクトを配置した場合では MCU の発生率が 0 となっている. シフトレジスタ (d) の実測結果では 1 つ MCU が生じているものの、回路シミュレーション結果と良く一致する. MCU 耐性の向上にはウェルコンタクトをフリップフロップの間に配置することが効果的である.

### 保持データ依存性

SEU と MCU の保持データに対する変化を表 3.2 と表 3.3 に示す. クロック信号は "0" に固定して測定した結果である. 表 3.2 では SEU と MCU の発生数を示し, 表 3.3 では比較のために発生率に変換した値である. 第 2.3.2 節のシミュレーション結果も表 3.3 に示

表 3.2: 各シフトレジスタにおける SEU 発生率と MCU 発生率の保持データ依存性. クロック信号を"0"に固定した場合の測定結果である. 保持データが"0"の場合では29回測定した結果の合計であり, 保持データが"1"の場合では51回測定した結果の合計である.

| 保持データ          | シフトレジスタ | SEU 発生数 | MCU 発生数 |

|----------------|---------|---------|---------|

| ALL0           | (a)     | 60      | 0       |

| $(N_{TS}=0)$   | (b)     | 78      | 0       |

|                | (c)     | 79      | 0       |

|                | (d)     | 91      | 0       |

| ALL1           | (a)     | 254     | 15      |

| $(N_{TS} = 1)$ | (b)     | 283     | 10      |

|                | (c)     | 259     | 33      |

|                | (d)     | 165     | 0       |

す. このシミュレーション結果はシフトレジスタ (a) の場合に相当する.

保持データが"0"(図 2.6 の N<sub>TS</sub> = 0) の場合では、どのシフトレジスタでも SEU と MCU の発生率が低い. 特に保持データの値による MCU の発生率の違いは顕著であり、保持データが"0"では MCU が生じない結果となった. この原因は第 2.3.2 節のシミュレーション結果で示したように、基板電位の上昇が値の反転を阻害しているためであると考えられる. 前節で示したように、MCU の 99%は寄生パイポーラトランジスタによって生じている. しかし保持データが"0" の場合では、基板電位が変動してもフリップフロップの保持データが寄生バイポーラ効果によって反転しない. よって 99%の MCU は生じなくなるため、MCU の発生率が大きく低下していると推測される. 保持データが"0" の場合に SEU 発生率が低いのは、インバータの方がトライステートインバータよりも駆動力が大きく、生じた電荷によって保持データが反転しにくいためである. この保持データ依存性の結果は回路シミュレーションよりも SEU の値が 3 倍程度大きいものの、その傾向は一致する. MCU に関しても発生率に大きな差があるものの、保持データが"0" の場合では実測とシミュレーションともにエラーが発生しなかった.

クロック信号が "0" の場合にシフトレジスタ (a) - (c) で生じた MCU のうち, 96% が p ウェルを共有するフリップフロップの間で生じていた. p ウェルに中性子が衝突すると移動度の低い正孔によって長時間基板電位が変動するため, MCU が生じやすいと推測される. この結果は p ウェルを分離して設計した DICE ラッチの構造を提案している文献 [50] の評価結果と良く一致する.

表 3.3: 各シフトレジスタにおける SEU 発生率と MCU 発生率の保持データ依存性. クロック信号を "0" に固定した場合の測定結果である.

|                | ic grayer and it | SEU 発生率    | MCU 発生率    |

|----------------|------------------|------------|------------|

| 保持データ          | シフトレジスタ          | [FIT/Mbit] | [FIT/Mbit] |

| ALL0           | (a)              | 132        | 0          |

| $(N_{TS} = 0)$ | (b)              | 171        | 0          |

|                | (c)              | 173        | 0          |

|                | (d)              | 200        | 0          |

|                | sim.             | 64         | 0          |

| ALL1           | (a)              | 559        | 33         |

| $(N_{TS} = 1)$ | (b)              | 622        | 22         |

|                | (c)              | 570        | 72         |

|                | (d)              | 363        | 0          |

|                | sim.             | 204        | 2.0        |

### MCU / SEU のラッチ間距離依存性

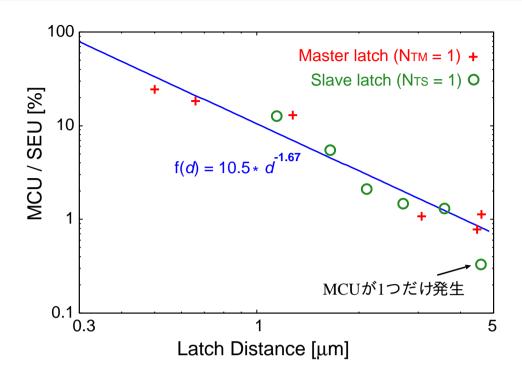

MCU / SEU のラッチ間距離依存性を図 3.8 と図 3.9 に示す.  $N_{TS}=0$  では MCU が生じなかったため, 図 3.8 と図 3.9 では省略した.

MCU / SEU の値はラッチ間距離に対してべき乗で減少する結果となった。また図 3.9 に示すように、3µm までは片対数でも直線となっており、指数で減少しているともいえる。ラッチ間距離が増加すると MCU の割合は減少するものの、その減少量はあまり大きくない。 MCU / SEU が 1%以下となるには約 3µm 程度必要となる。また図 2.6 で示したように、フリップフロップのマスターラッチとスレイブラッチでは構成するインバータのトランジスタサイズや負荷容量が異なる。しかしマスターラッチとスレイブラッチの測定結果は共に同一の直線上に分布している。 MCU / SEU の距離依存性は駆動力や負荷容量にあまり影響されないといえる。 文献 [66] では、耐放射線フリップフロップのエラー耐性は回路の構造ではなく多重化したノード間の距離に依存すると報告されている。 今回の測定結果はこの報告と一致する。また SRAM における距離依存性とも一致する [36].

回路シミュレーションと比較した結果を図 3.9 に示す. 実測と比較するとシミュレーション結果の MCU / SEU は小さく、おおよそ 4 倍程度異なる. しかしその傾向は一致しており、片対数で直線となっている. 回路シミュレーションでは、特定の電荷収集条件における MCU 発生率を求めている. しかしながら、実際には様々な電荷収集が行われてい

図 3.8: 両対数でプロットした場合の MCU/SEU のラッチ間距離依存性.

る. 回路シミュレーションにおいてはこれらの影響が考慮されていない. また, 電荷収集効率を表す Q<sub>s</sub> の値も, 実際のシリコンでの値と, シミュレーションで仮定した値が異なっていると想定される.

#### 3ビット以上のMCUの形状

図 3.2 のシフトレジスタ (a)–(c) では 3 ビット以上同時に反転した MCU も発生した. その形状と個数を図 3.10 に示す. 生じた個数が少ないため (a)–(c) の区別をせず, 合計して図 3.10 に示した.

3 ビット以上の MCU の発生率は SEU 発生率の 0.95%である. 3 ビット以上反転した MCU の場合では直線上に並んだフリップフロップの保持データが反転している. また 上下方向に並んだフリップフロップの保持データが 3 つ以上反転しているものも存在している. この場合では反転した全てのフリップフロップで同じウェルを共有していないため, 寄生バイポーラトランジスタによって MCU が生じたとは考え難い. 中性子衝突によって生じた二次イオンが複数のフリップフロップを貫通する連続衝突により, 3 ビット以上の MCU は発生したと考えられる. 図 3.9 の 4μm 以上の MCU の発生率が 1%で飽和

図 3.9: 片対数でプロットした場合の MCU/SEU のラッチ間距離依存性.

しているのはこの連続衝突による MCU が原因であると推測される.

# **3.2.5** フリップフロップにおけるシングルイベント効果の特性のまとめ 図 3.2 の 4 種類のシフトレジスタを測定することで以下の特性が明らかとなった.

- 65nm プロセスではフリップフロップでも MCU が生じており、その割合は最大で SEU 発生数の 23%となる. 多重化回路を構成するフリップフロップを上下に並べ て設計した場合では、多重化回路のソフトエラー耐性は通常のフリップフロップの 4 倍程度まで減少する場合が生じる.

- SEU と MCU 発生率はデータ依存性が強い. 駆動力の弱いトライステートインバータの出力が"0"の場合では MCU が発生せず、SEU の発生率も 1/5 程度となる.

- MCU はウェルコンタクト密度に強く依存する. 上下に配置したフリップフロップ の間にウェルコンタクトを配置することで MCU /SEU が 0.2% となる.

- MCU は p ウェルを共有するフリップフロップ間で 96%の MCU が生じており, p ウェルでの基板電位の変動が MCU を引き起こすと考えられる.

図 3.10: 3 ビット以上の MCU の形状.

- MCU はラッチ間距離に対して指数またはべき乗で減少する. MCU / SEU を 1%以下にするには、ラッチ間距離を約 3μm 程度離す必要がある.

- 3 ビット以上の MCU は主に連続衝突によって生じると考えられる.

多重化回路では MCU が大きな問題となる. しかし MCU の特性はラッチ間距離や保持データ, ウェルコンタクトの挿入方法などに強く依存している. これらの特性を考慮して設計することにより多重化回路のエラー耐性は大きく変化する.

# 3.3 論理ゲートにおけるシングルイベント効果の特性評価回路

本節では論理ゲートにおけるシングルイベント効果である SET のパルス幅を測定する 回路構造を説明する.

# 3.3.1 既存の評価手法と問題点

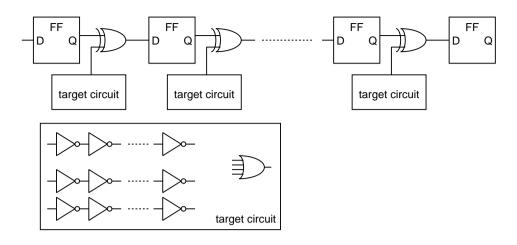

論理ゲートにおけるシングルイベント効果である SET の評価手法は主に 2 種類の方法がある. 1 つは SET によって値が反転したフリップフロップのエラー率を測定することで SET によるエラー率を測定する方法である [67]. 組み合わせ回路部分において発生した SET により SEU が発生する状況を実験的に求めるための回路を図 3.11 に示す. シフトレジスタを構成するフリップフロップの各入力に, 測定対象であるインバータチェイン等の論理ゲートを XOR ゲートなどを介して接続している. 粒子線照射時には任意の周波数のクロック信号を入力する. 測定対象の回路 (target circuit) のインバータで SET が生じると, XOR ゲートを介してフリップフロップの入力が一時的に反転する. SET によって反転している間にクロック信号が遷移すると, フリップフロップが間違った値を取り込みエラーとなる. フリップフロップの値が反転した個数は, シフトレジスタの出力に接続されたカウンタ等を使用して数えられる. 粒子線照射後にカウンタの値を読み出すことで, SET によるエラーを測定する手法である.

この手法ではSETによるエラーだけでなく、フリップフロップで生じるSEUのエラー率も加算されて測定される。そのため、SEUが生じにくいDICEラッチなどのソフトエラー耐性回路が用いられる。SETによるエラーの割合を増加させるために、フリップフロップ1つあたりに接続される論理ゲートの個数を多くする。またクロック周期が短くなるほどSETによってフリップフロップの保持値が反転する確率は増加するため、高速なクロック信号を用いる必要がある。クロック周期に対するエラー率の変化を測定し、クロック周期にあまり依存しないSEUによるエラー率との分離が行われる。この手法ではSETを直接測定していないため、生じたSETのパルス幅が不明となる。そのためSETの詳細な特性評価には向かない。

もう1つの SET 評価手法は TDC(Time to Digital Converter) を用いて SET のパルス幅を測定し、パルス幅ごとの発生率を測定する方法である。 文献 [42] で提案されている SET パルス幅測定回路を図 3.12 に示す。 測定対象の回路 (target circuit) はインバータチェインで構成されており、インバータチェインで生じた SET を測定回路であるラッチのチェインと SR ラッチを用いて捕捉する構造となっている。 回路の動作を以下に箇条書きで説明する。

- SR ラッチの保持データをリセット信号を入力して 0 に初期化する. 全てのラッチはデータ通過状態となる.

- 被測定回路 (target circuit) で SET が生じるとパルスが伝播し、ラッチに入力される.

入力された SET パルスはラッチを伝播していく.

- SET パルスは遅延素子 (delay) を通過した後に SR ラッチにも入力され, SR ラッチの保持データが 1 となる. SR ラッチによって SET の発生が検出される.

- SR ラッチの出力が 1 となるため, ラッチがデータ保持状態になり, 値を保持する. SET パルスはラッチのチェインを伝播しているため, SET のパルス幅に応じた数の ラッチが反転した値を保持する.

- 反転したラッチの個数とラッチ1段分の遅延の積でSETのパルス幅が求められる.

SET のパルス幅の測定には上記のような伝播遅延と記憶素子を利用した測定回路が主に用いられている [44].

SET の測定では SEU と比較して発生数が少ないため、被測定回路として非常に長いイ ンバータなどのチェインが用いられることが多い. 文献 [68] では 1000 段, 文献 [69] では 330,000 段のインバータチェインを測定対象として用いている. しかし文献 [45] などでは パルスがインバータを伝播する間にパルス幅が変動することを報告している. 変動量は 伝播したインバータの段数に比例するため、生じた SET のパルス幅が同じでも SET が生 じたインバータチェインの位置によって出力されるパルス幅が異なってしまう. その変 動量は 90nm プロセスでインバータ 1 段当たり 1ps 程度と報告されており [45], 1000 段の インバータチェインでは最大で 1ns 程度異なってくる. 文献 [68] に示されている中性子 起因 SET のパルス幅は最大で 1.4ns であるため. 最大で 1ns になるチェイン通過によるパ ルス幅の変動の影響は非常に大きい、1000段などの段数の多いインバータチェインを測 定対象とする場合では、SET パルス幅を正確に測定することは困難である. チェイン通過 によるパルス幅の変動を抑えるために, 文献 [46] ではインバータチェインを 20 段として いる. また文献 [70] では OR ゲート等を用いてチェインを並列化してチェイン 1 つあた りの長さを短くしている. SET のパルス幅測定回路にはパルス幅の変動を抑え, 測定精度 を高めた回路構造が求められる. また文献 [46] のように短いチェインを測定対象とする 場合では、測定対象と比較して測定回路の面積が大きくなる. 短いチェインを用いて測定 を行う場合では、回路規模の小さい測定回路が必要となる.

本研究では測定精度を高めたパルス幅測定回路と,回路面積を抑えたパルス幅測定回路の2種類を提案する.前者の回路ではチェインを通過する間にSETのパルス幅が減少することを利用した測定回路である.一方で後者の回路では図3.12に示す測定回路のラッチチェイン部分をリングオシレータを用いることで冗長なラッチチェインの面積を削減

図 3.11: SET によって生じるフリップフロップのエラー率を評価する回路構造 [67].

図 3.12: ラッチチェインを用いた SET パルス幅測定回路 [42].

した. 次節で測定原理であるバッファチェインにおけるパルス幅縮小現象について説明 し、次に提案回路の構造を示す.

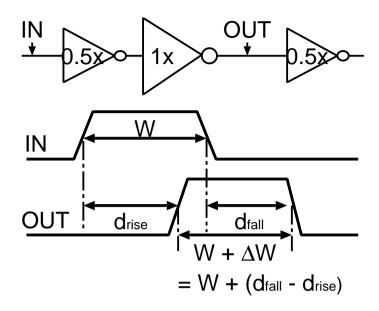

# 3.3.2 チェイン通過によるパルス幅変動現象

本節ではチェイン通過によるパルス幅変動現象をバッファチェインを例に説明する. 図 3.13 は駆動力が 0.5 倍のインバータと 1 倍 (標準) のインバータからなるバッファによって構成されるバッファチェインである. チェイン通過によるパルス幅変動現象はバッファの立ち上がり入力の伝播遅延時間  $d_{rise}$  と立ち下がり入力の伝播遅延時間  $d_{fall}$  が異なるこ

とによって生じる. インバータの立ち上がり入力の伝播遅延時間  $d_{\text{Irise}}$  は出力の負荷容量 C と, nMOS トランジスタのトランスコンダクタンス  $g_{mn}$  を用いて以下のように近似できる [71].

$$d_{\text{Irise}} \approx k \frac{C}{g_{\text{mn}}}$$

(3.1)

k は比例定数である. インバータの立ち下がり入力の伝播遅延時間  $d_{\text{Ifall}}$  も同様に pMOS トランジスタのトランスコンダクタンス  $g_{\text{mp}}$  を用いて以下のように近似できる.

$$d_{\text{Ifall}} \approx k \frac{C}{g_{\text{mp}}}$$

(3.2)

バッファチェインの場合負荷容量は次段の入力容量  $C_g$  となるため,  $d_{\mathrm{rise}}$  と  $d_{\mathrm{fall}}$  は以下のように近似できる.

$$d_{\text{fall}} \approx k \left( \frac{C_{\text{g}}}{0.5g_{\text{mp}}} + \frac{0.5C_{\text{g}}}{g_{\text{mn}}} \right)$$

(3.3)

$$d_{\text{rise}} \approx k \left( \frac{C_{\text{g}}}{0.5g_{\text{mn}}} + \frac{0.5C_{\text{g}}}{g_{\text{mp}}} \right)$$

(3.4)

第 1 項が駆動力 0.5x のインバータの伝播遅延時間, 第 2 項が駆動力 1x のインバータの伝播遅延時間を表す. パルス幅変動現象によるパルス幅の変動量  $\Delta W$  は図 3.13 で示すように  $d_{rise}$  と  $d_{fall}$  の差によって決定されるため, 式 (3.3) と式 (3.4) を用いて以下のように表される.

$$\Delta W = d_{\text{fall}} - d_{\text{rise}} = \frac{3}{2}kC_{\text{g}}\left(\frac{1}{g_{\text{mp}}} - \frac{1}{g_{\text{mn}}}\right)$$

(3.5)

式 (3.5) から pMOS トランジスタと nMOS トランジスタのサイズ比を変更することでバッファ1 段当たりのパルス幅変動量  $\Delta W$  を調節できることが分かる. 例えば  $g_{mn}$  を  $g_{mp}$  の 0.9 倍とすると, 式 (3.5) より  $\Delta W$  は  $-\frac{1}{4}k\frac{C}{g_{mp}}$  となる. この値は式 (3.2) のインバータの遅延時間の 1/4 の値であり, インバータの立ち下がり遅延時間を 10ps とすれば約 -2.5ps となる.

チェイン通過によるパルス幅変動現象の変動量  $\Delta W$  は、pMOS トランジスタと nMOS トランジスタのトランスコンダクタンスの値や負荷容量  $C_g$  によって大きく変動する. そのため製造時に生じるトランジスタ性能のばらつきによって大きく変動する. ばらつきを考慮したシミュレーションにより  $\Delta W$  の範囲を推定することは可能であるものの、製造前の段階で  $\Delta W$  を正確に推定するには困難が伴う. 回路シミュレーションを用いて  $\Delta W$  を推定する場合では、平均値として  $\Delta W$  を評価せざるを得ない.  $\Delta W$  の値は実測による評価が必要である.

図 3.13: チェイン通過によるパルス幅縮小現象.

## 回路シミュレーションによるパルス幅変動現象の評価

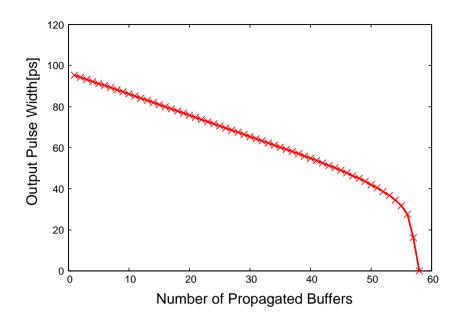

パルス幅が通過段数に対して線形に減少することを確認するため、パルス幅 100ps の矩形波をバッファチェインに入力した場合に出力されるパルス幅を回路シミュレーションを用いて評価した。評価結果を図 3.14 に示す。図 3.14 ではバラツキを考慮しておらず、標準のトランジスタ性能の場合を仮定している。横軸は通過したバッファの段数であり、縦軸は x 段のバッファを通過した後のパルス幅を示している。パルス幅が 40ps 以上ある場合ではバッファチェインを通過する間に線形に減少しており、1 段当たりの変動量は約1ps と小さい。一方で 40ps 以下になると急激にパルス幅が減少している。パルス幅がバッファの出力の遷移時間に近くなっているため、電気的遮蔽によってパルス幅が減衰することが原因である。

このパルス幅の線形減少を利用すると、入力したパルスが消滅するまでに通過したバッファの段数からパルス幅を求めることができる。バッファで SET パルスが生じた場合では、発生したバッファの位置と消滅したバッファの位置から通過段数を求め、バッファ1段当たりの変動量と乗算することで SET パルス幅を測定することができる。1段当たりの変動量も小さいため、パルス幅縮小現象を利用して SET パルス幅を測定すると高い分解能を実現できる。

図 3.14: バッファにおけるパルス幅縮小現象のシミュレーション結果. 横軸が通過したバッファの段数, 縦軸が出力されたパルス幅. このシミュレーションではバラツキを考慮していない.

# 3.3.3 パルス幅縮小現象を利用した SET パルス幅測定回路

パルス幅縮小現象を利用した SET パルス幅評価回路を図 3.15 に示す. 前節で示したように、SET のパルス幅をパルス幅縮小現象を利用して測定するには SET パルスの発生個所と消滅個所を知る必要がある. バッファチェインで生じた SET パルスの発生個所と消滅個所が分かるように、提案回路では各バッファの出力をフリップフロップのクロック入力に接続している. フリップフロップは保持データの書込みと読み出しが可能となるようにシフトレジスタ構造となっている. SET パルスがバッファチェインで生じると、SET が生じたバッファ以降のフリップフロップでは SET パルスがクロック信号として認識されるため、シフトレジスタの値がシフトする. 生じた SET パルスはパルス幅縮小現象によって通過した段数に対して線形減少するため、生じた SET のパルス幅によってシフトするフリップフロップの個数が決定される.

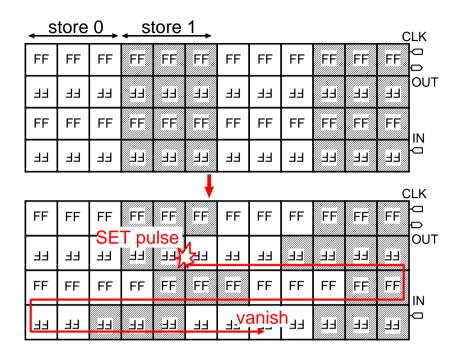

シフトしたフリップフロップの段数を測定する初期化方法を図 3.16 に示す. 白色のフリップフロップは "0" を, 灰色のフリップフロップは "1" を保持している. 図 3.16 では 3 列ごとにフリップフロップの保持データを変更しているため, 縦縞模様にシフトレジスタが初期化されている. 縦縞模様にフリップフロップの保持データを初期化した場合にバッ

図 3.15: パルス幅変動を利用した SET パルス幅測定回路.

ファで SET が生じると, SET によって図 3.16 の下のように縦縞の境界が崩れる. 縦縞模様によってシフトした FF の個数は容易に判定可能であるため, 提案回路によって SET パルス幅を高い精度で測定する事が可能となる. ただし 2 つ以上の境界がずれないと SET が生じたと判定できない. 縦縞の幅の 2 倍以上の段数のバッファを通過する前に SET が消滅してしまうと, パルス幅が測定できない.

図 3.15 は図 3.1 と同じ構造であり、フリップフロップにおけるシングルイベント効果である SEU や MCU の測定も同時に可能である.

#### SET パルス幅測定回路の性能比較

図3.12のラッチの伝播遅延を利用した SET パルス測定回路と, 図3.15のパルス幅変動を利用した SET パルス幅測定回路の性能を比較した結果を表3.4に示し, 以下に詳細な性能比較を箇条書きで示す.

測定精度 第 3.3.1 節でも示したように, ラッチの伝播遅延を利用した SET パルス幅測定 回路ではパルス幅を記憶する測定回路が測定対象の回路に直列で接続されている. そのため、チェイン通過によって SET のパルス幅が変化する. SET の発生した位置

図 3.16: SET 測定のための縦縞模様による初期化.

と測定されるパルス幅に依存性があり、測定精度が低くなる. 一方で提案回路ではパルス幅を記憶するフリップフロップが SET 発生部であるバッファチェインに並列接続されているため、SET の発生個所も測定できる. 測定結果に発生位置の依存性はなく、測定精度は高い.

- 測定分解能 ラッチの遅延時間を用いて測定する既存回路では、測定分解能はもっとも高い状態でもインバータの遅延時間となる。 65 nm プロセスでは測定分解能は必ず10 ps 以上となり、文献 [42] では90 nm プロセスで100 ps の測定分解能となっている。提案回路ではパルス幅縮小現象によって測定するため、測定分解能はバッファ1 段当たりのパルス幅の変動量  $\Delta W$  となる。式 (3.5) に示したように、 $\Delta W$  はp MOS トランジスタとn MOS トランジスタのサイズ比の変更により調節でき、後に示す実測結果では1 ps 以下となった。

- 最小測定可能パルス幅 ラッチの遅延時間を利用して測定する場合,測定可能な最小のパルス幅はラッチのセットアップ時間とホールド時間を合計した値となる.65nmプロセスでは約40psとなる.一方でパルス幅縮小現象を利用する場合では,初期化方法によって異なる.図3.16に示す縦縞模様の初期化方法では2つ以上の境界がずれないとSETが生じたと判定できない.そのため,縦縞模様の2倍の段数を通過して

| 表 3.4: 伝播遅延を利用した回路とパルス幅変動を利用した回路の性能比較. 数 | 数値は 65nm |

|------------------------------------------|----------|

| プロセスを想定した値を示す.                           |          |

|              | 伝播遅延を利用した回路  | パルス幅変動を利用した回路 |

|--------------|--------------|---------------|

| 測定回路の接続      | 直列           | 並列            |

| パルス幅変動の影響    | 大            | なし            |

| 測定精度         | 低い           | 高い            |

| 測定原理         | 伝播遅延         | パルス幅縮小現象      |

| 測定分解能        | (>10ps)      | < 1ps         |

| 最小測定可能パルス幅   | ラッチのセットアップ時間 | バッファの遅延時間     |

|              | とホールド時間の合計   |               |

| SEU, MCU の測定 | 不可           | 可能            |

| 回路面積         | 小            | 大             |

も消滅しない SET しか測定できない. また, バッファの遅延時間よりも小さいパルスは電気的遮蔽によって消滅してしまうため, 測定できる最小のパルス幅は最大でもバッファの遅延時間となる.

- SEU、MCU の測定 既存の SET パルス幅測定回路ではラッチは値を保持していないため、 SEU の測定はできない. SEU の測定をする場合にはシフトレジスタを別に用意する 必要がある. 一方で提案回路ではフリップフロップが値を保持しているため、SEU も同時に測定できる. また提案回路はバッファとフリップフロップのみで構成されるため、規則的に配置しやすく MCU の測定にも適している.

- 回路面積 既存の SET パルス幅測定回路では測定回路がラッチ数十段と SR ラッチのみであるため、面積は小さい. 一方で提案回路では測定対象のバッファ毎にフリップフロップが挿入されているため、面積は大きい. 分解能は低下するが、フリップフロップの挿入間隔を変更することで面積を抑えることができる.

提案回路は高精度かつ高分解能であり、SEU と MCU も同時に測定可能とメリットが多い. デメリットとして回路面積が大きいことが挙げられるが、SEU を測定するためのシフトレジスタ回路として機能させる場合には、既存回路とは同等の面積で実現できる.

# 3.3.4 リングオシレータ構造を用いた SET パルス幅測定回路

前節では高精度な SET パルス幅の測定を目的とした回路構造を示した. 本節では従来回路よりも省面積な SET パルス幅測定回路を示す.

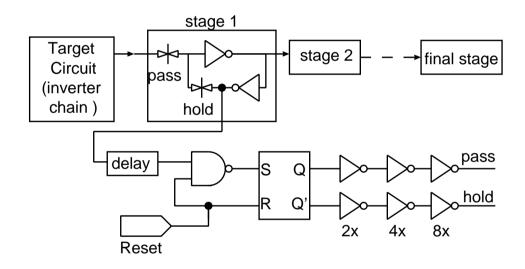

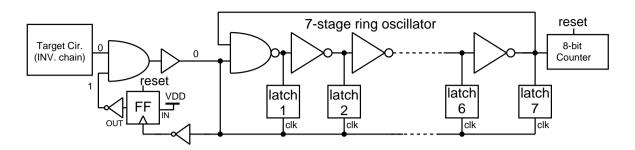

提案するリングオシレータ構造を利用した SET パルス幅測定回路を図 3.17 に示す. 提案回路は 7 段リングオシレータと発振周波数を測定するカウンタ, リングオシレータの各段に接続されたラッチ, SET の発生を検知するフリップフロップと AND ゲートから構成される. 以下に動作原理を示す.

- 測定対象の回路であるインバータチェインで SET パルスが生じると, AND ゲートとバッファを通過してリングオシレータの NAND ゲートの入力が"1"に反転する. 反転している時間リングオシレータが発振し, SET パルスによる反転が終了すると発振が止まる. よって SET パルス幅の時間だけリングオシレータが発振する.

- カウンタはリングオシレータの発振回数を保存する. リングオシレータの発振周期は NAND ゲートとインバータ 6 段の立ち上がり/立ち下がり遅延時間によって決定される. リングオシレータの発振回数と発振周期から大まかな SET パルスによる信号反転時間. すなわち SET パルス幅の測定が可能である.

- ラッチのクロック入力には SET パルスが入力されるため、SET による反転中はデータ通過状態となっている。SET パルスによる反転が終了するとラッチがデータ保持状態となり、リングオシレータの発振が停止した直後の各段の出力値を保存する。リングオシレータの各段の出力値、すなわちラッチの入力値の状態遷移を表 3.5 に示す。リングオシレータでは NAND ゲートの出力の反転がインバータを伝播するため、ラッチ 1 からラッチ 7 まで順番に入力値が反転する。リングオシレータの最後のインバータが反転すると、NAND の入力が反転する。同様にしてインバータが順番に元の値に戻っていくため、各ラッチの入力値は表 3.5 に示す 14 種類の値に遷移する。リングオシレータは発振している間表 3.5 に示す状態 1 から状態 14 の状態を繰り返す。繰り返した回数がカウンタに保存され、ラッチに状態 1 から状態 14 のいずれかの状態が保存される。よって提案回路は約インバータ 1 段分の伝播遅延時間で SET パルス幅が測定できる。

- 図 3.17 の回路では 1 度 SET パルスが生じた後では組み合わせ回路から SET パルス が伝播しないように, フリップフロップと AND ゲートを挿入している. またこのフ

図 3.17: リングオシレータ構造を用いた SET パルス幅測定回路. 図内の値は初期状態での各ノードの値を示す. カウンタとラッチの保持値(測定データ)を読み出すためのスキャンフリップフロップは省略.

リップフロップの値を読み出すことで、SET が発生したかを判定できる. 測定回路部分のラッチやカウンタで生じた SEU によるエラーと分離が可能となる.

リングオシレータ構造を用いた SET パルス幅測定回路での測定結果はカウンタとラッチの値である. ラッチの状態数  $(N_{\rm lat})$  は 14 通りであり, カウンタはリングオシレータの発振回数  $(N_{\rm RO})$  を保存している. よって測定結果であるパルス幅,  $W_{\rm SET}$  は以下のように計算される.

$$W_{\text{SET}} = N_{\text{RO}} \times 14 + (N_{\text{lat}} - 1)$$

(3.6)

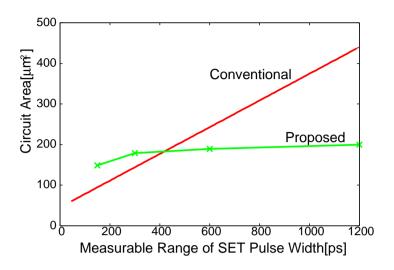

従来回路の図 3.12 ではラッチの遅延時間を SET パルス幅の測定に用いているため, 測定可能なパルス幅の範囲を倍増するにはラッチチェインの段数を倍にする必要がある. 一方で提案する図 3.17 の回路ではカウンタのビット数を 1 つ増やすだけで測定範囲が倍増する. 図 3.18 に示すように, 提案回路は従来回路より省面積で広範囲の SET パルスを測定できる.

図 3.17 の最低測定可能パルス幅はラッチのセットアップ時間とホールド時間に制約される. 図 3.12 のラッチチェインを用いた場合と等しい.

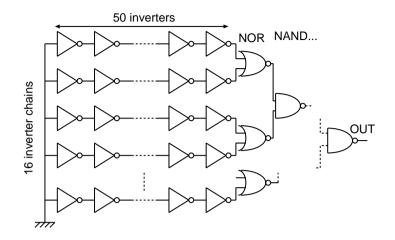

測定対象であるインバータチェインの構造を図 3.19 に示す. 測定対象にインバータチェイン 50 段を 16 行並べ, NOR と NAND のツリーでまとめた構造とした. 文献 [70] と比較するとチェインを 50 段と長くしている. NAND ゲートや NOR ゲートで生じる SET を相対的に少なくするために 50 段とした. 文献 [45] で示されている 90nm プロセスでのチェイン通過によるパルス幅の変動量は 1ps である. この値を参考にすると, 50 段では変動量が 50ps 程度と予測されるため、その影響は小さい.

図 3.18: 提案するリングオシレータ構造を用いた SET パルス幅測定回路 (図 3.17) と従来回路 (図 3.12) の面積の比較.

表 3.5: リングオシレータ発振時のラッチの入力値の状態遷移. ラッチの番号は図 3.17 の番号に対応する. 初期値に対して反転している場合は太字で値を示す. 15 番目では初期状態に戻る.

| 状態番号    | ラッチ番号 |   |   |   |   |   |   |

|---------|-------|---|---|---|---|---|---|

|         | 1     | 2 | 3 | 4 | 5 | 6 | 7 |

| 1(初期状態) | 1     | 0 | 1 | 0 | 1 | 0 | 1 |

| 2       | 0     | 0 | 1 | 0 | 1 | 0 | 1 |

| 3       | 0     | 1 | 1 | 0 | 1 | 0 | 1 |

| 4       | 0     | 1 | 0 | 0 | 1 | 0 | 1 |

| 5       | 0     | 1 | 0 | 1 | 1 | 0 | 1 |

| 6       | 0     | 1 | 0 | 1 | 0 | 0 | 1 |

| 7       | 0     | 1 | 0 | 1 | 0 | 1 | 1 |

| 8       | 0     | 1 | 0 | 1 | 0 | 1 | 0 |

| 9       | 1     | 1 | 0 | 1 | 0 | 1 | 0 |

| 10      | 1     | 0 | 0 | 1 | 0 | 1 | 0 |

| 11      | 1     | 0 | 1 | 1 | 0 | 1 | 0 |

| 12      | 1     | 0 | 1 | 0 | 0 | 1 | 0 |

| 13      | 1     | 0 | 1 | 0 | 1 | 1 | 0 |

| 14      | 1     | 0 | 1 | 0 | 1 | 0 | 0 |

図 3.19: 測定対象のインバータチェインの構造. 16 並列のインバータチェインを NAND, NOR ゲートで 1 つにまとめている. インバータで SET が生じると反転が伝播し, 出力が反転する.

# **3.4** 論理ゲートにおけるシングルイベント効果の特性評価結果

本節では提案する2つのSETパルス幅測定回路を用いてSETのパルス幅分布を測定した結果を示す.加速試験はフリップフロップと同様に大阪大学核物理研究センターで行った.

図 3.15 のパルス幅変動を利用した SET パルス幅測定回路をバッファチェイン型測定回路と呼び、図 3.17 のリングオシレータ構造を用いた SET パルス幅測定回路をリング型測定回路と呼ぶ. 本節ではこれらの単語を用いて測定回路を引用する.

# 3.4.1 加速試験によるシングルイベント効果の評価方法

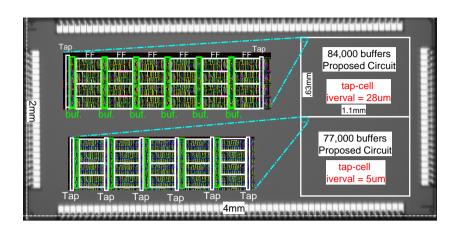

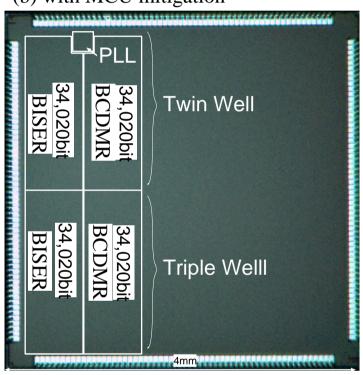

中性子線の照射実験を行うために、65nm プロセスを用いてバッファチェイン型測定回路とリング型測定回路の設計を行った。設計したチップを図3.20と図3.21に示す。

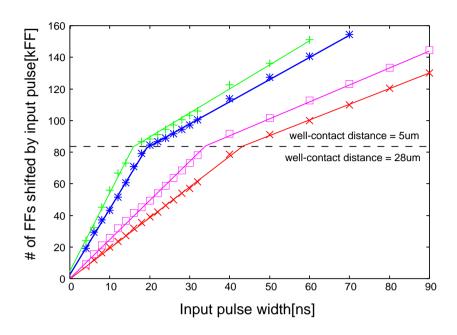

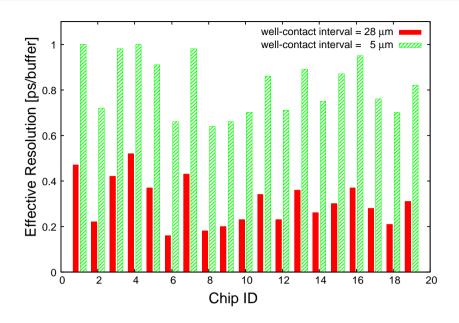

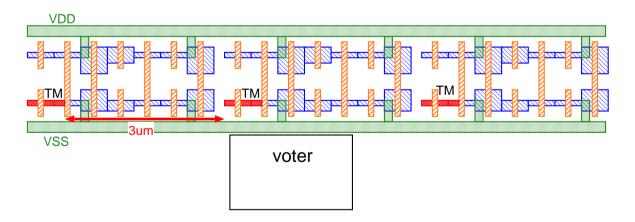

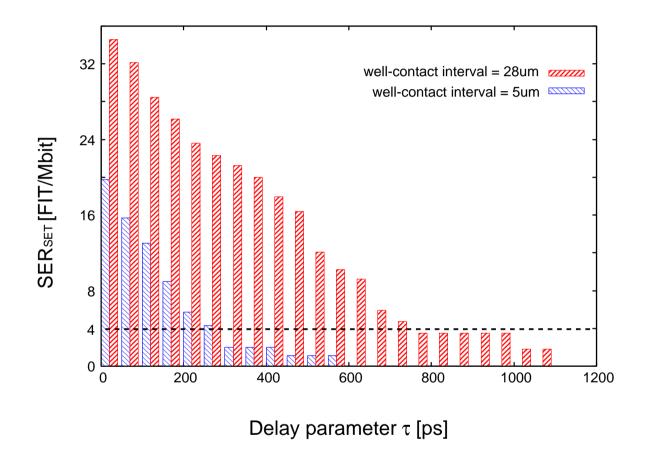

ウェルコンタクト密度の異なる 2 種類のバッファチェイン型測定回路を試作した. チップ写真を図 3.20 に示す. 図 3.20 の上側の回路ではウェルコンタクトで構成されるタップセルを  $28\mu m$  ごとに挿入しており, 下側の回路では  $5\mu m$  ごとに挿入した. これによりウェルコンタクト距離に対する SET パルス幅と発生率の依存性を測定する. 一方で図 3.17 と図 3.19 を 1 単位回路としたリング型回路を図 3.21 に示すチップ上に 360 個設計した. 駆

図 3.20: パルス幅縮小現象を利用した SET パルス幅測定回路を試作したチップの顕微鏡写真.

| 表 3.6: 測定対象のインバータの種類. | ドレイン面積は 1x | インバータを1とした場合. |

|-----------------------|------------|---------------|

|-----------------------|------------|---------------|

| 測定回路          | 駆動力       | ドレイン面積 [a. u.] | ウェルコンタクト間隔 |

|---------------|-----------|----------------|------------|

| 図 3.15        | 1x ≥ 0.5x | 1 ځ 0.5        | 28 μm      |

| バッファチェイン型測定回路 | (バッファ)    |                | 5 μm       |

| 図 3.17        | 1x        | 1              | 50 μm      |

| リング型測定回路      | 2x        | 1.1            |            |

|               | 4x        | 2.2            |            |

|               | 16x       | 6              |            |

動力が 1x, 2x, 4x, 16x のインバータを各 72,000 個搭載している. 測定対象のインバータの種類を表 3.6 にまとめて示す. 駆動力の違いによる SET 発生率の変化のみを測定するために, ウェルコンタクトの挿入間隔は駆動力によらず  $50\mu$ m として設計した.

測定時には SEU, MCU の測定と同じように図 3.6 に示す 7 段積みの DUT ボードを用いて 28 チップ同時に測定を行った. 中性子線をチップに対して垂直方向に照射し, 5 分毎にカウンタとラッチの値を読み出した.

## 3.4.2 SET パルス幅測定回路の動作確認結果

中性子線による評価結果を示す前に、設計した SET パルス幅測定回路にパルスを入力して動作確認と測定分解能を評価した結果を示す.

図 3.21: リングオシレータ構造を用いた SET パルス幅測定回路を試作したチップの顕微 鏡写真.

チップ外部から図 3.15 の CLK\_IN に 4ns から 90ns のパルスを入力し, バッファチェイン型測定回路の動作確認を行った. 動作確認の結果を図 3.22 と図 3.23 に示す. 入力したパルス幅に対して通過したバッファの段数は線形に増加しており, バッファチェイン型測定回路を用いることでパルス幅を測定可能であることが分かる. 分解能が 1ps 以下と非常に高いものの, チップ間で大きな差が見られた. これはチップ間ばらつきによってpMOS トランジスタと nMOS トランジスタのトランジスタ性能がチップ間で異なるためである. 実際にコーナーモデルを用いてシミュレーションを行い, 式 (3.5) の ΔW を求めた結果を表 3.7 に示す. ΔW はばらつきによって変化し, -3.0 ps から 1.1ps まで変化する. ウェルコンタクトの間隔が異なる場合でも大きな差が見られる. トランジスタの拡散領域と基板間に存在する寄生容量に蓄えられた電荷がバッファ動作時に基板に流れ, 基板の電位が上昇する. ウェルコンタクトの間隔が大きい場合では基板抵抗が大きいため, 基板電位の変動量が大きくなる. ウェルコンタクトの間隔が異なるとトランジスタの性能

図 3.22: バッファチェイン型測定回路の動作確認結果 (4 チップ分).

表 3.7: コーナーモデルによる式 (3.5) の ΔW の変化.

| 27 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - |          |             |          |         |        |  |

|------------------------------------------|----------|-------------|----------|---------|--------|--|

| ばらつき                                     | SS(slow) | TT(typical) | FF(fast) | SF      | FS     |  |

| $\Delta W$                               | -1.2 ps  | -0.60 ps    | -0.89 ps | -3.0 ps | 1.1 ps |  |

が変化し、遅延時間が変化していると推測される.

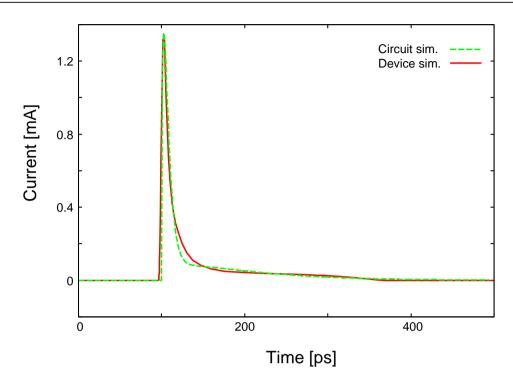

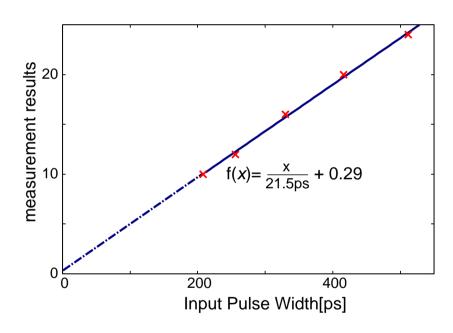

リング型測定回路の動作確認結果を図3.24に示す. 縦軸は式(3.6)を用いて計算した値である. 入力パルスのパルス幅に対して測定結果は線形に増加しており, 測定回路として正しく動作していることが確認できる. 測定分解能はその傾きの逆数から求められ, 値は21.5ps となった. また近似直線がほぼ原点を通ることから, チェイン通過によるパルス幅変動の影響が小さいことが分かる.

動作確認結果からパルス幅縮小現象を利用すると 1ps 以下と非常に高い分解能を実現できることが確認された. しかし今回の測定では図 3.16 に示した初期化方法である縦縞模様の幅を 20 段とし, 両回路の測定分解能を同程度にして測定した.

図 3.23: バッファチェイン型測定回路の測定分解能.

図 3.24: リング型測定回路の動作確認結果.

# 3.4.3 中性子線による評価結果

本節ではまず、測定精度の高いバッファチェイン型測定回路の測定結果であるバッファで生じた SET のパルス幅分布を示し、SET パルスのウェルコンタクト距離依存性を示す。 その後にリング型測定回路の測定結果である、インバータの駆動力に対する SET パルス の変化を示す.

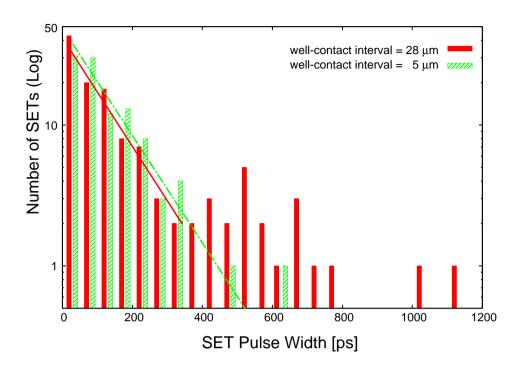

### ウェルコンタクトによるパルス幅分布の変化

バッファチェイン型測定回路を用いてバッファで生じた SET のパルス幅分布を図 3.25 に示す。SET により値がシフトしたフリップフロップの段数を測定し、図 3.23 に示した 各チップの分解能を乗算することで SET パルスのパルス幅を計算している。また測定時にはクロック信号は "1" で固定しており、バッファの 1x インバータの出力が "1" の状態で測定している。

パルス幅が小さい SET ほど発生数が多く, SET の 8 割以上が 200ps 以下のパルスである. パルス幅の変動を抑えた文献 [46] の結果と比較すると, SET のパルス幅分布の形状は似た結果となった. しかし, 本実験結果ではパルス幅の大きい SET の発生率が文献 [46] の結果の結果よりも高くなっている.

ウェルコンタクトの挿入間隔が  $5\mu$ m のバッファでは 50ps 以下の SET 発生数がやや少ないが、この原因はウェルコンタクトの挿入間隔が  $5\mu$ m の場合では測定分解能が 0.5ps ほど低いためである。分解能が低いため、測定可能な最小のパルス幅が大きくなっている。パルス幅の短い SET を測定できていないため、発生数が少なくなっていると推測される。パルス幅が大きい部分に着目すると、ウェルコンタクトの挿入間隔を  $5\mu$ m と短くすることでパルス幅が長い SET が減少しており、400ps 以上の SET の個数が 22 個から 2 個に減少している。パルス幅の大きい SET を除去するには遅延時間が長い遅延素子が必要となるが、遅延素子とウェルコンタクトを同時に使用することで遅延素子の遅延時間を抑制できる。

図 3.25 の縦軸を対数にしてプロットしたパルス幅分布を図 3.26 に示す. ウェルコンタクトを  $5\mu$ m で挿入した場合では、SET パルスの分布はほぼ直線で減少しており、SET のパルス幅は指数関数で減少する. 一方でウェルコンタクトを  $28\mu$ m で挿入した場合では、400ps 以上で直線から大きくずれる結果となった. 基板電位の変動が SET のパルス幅を増加させていると推測される.

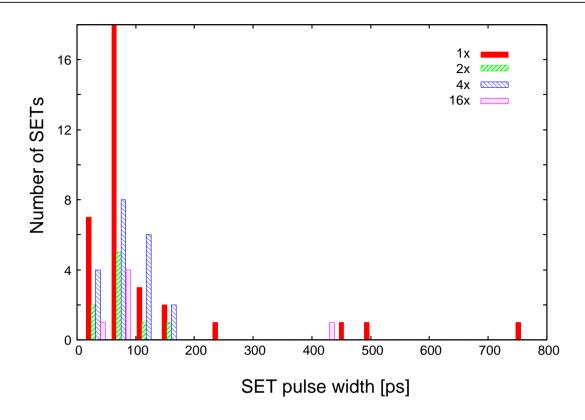

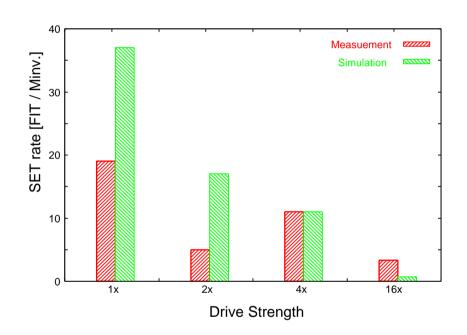

#### 駆動力の違いによる SET のパルス幅分布の変化

リング型測定回路を用いて駆動力の異なる4種類のインバータのSETパルス分布を測定した結果を図3.27に示す. 横軸は測定結果に図3.24で示した分解能,21.5psを乗算した結果である.

図 3.25: ウェルコンタクトによる SET パルス幅分布の変化.

SET パルスの分布の形状は駆動力の増加に対してあまり変化しない. どの駆動力でも大部分のパルスが 200ps 以下であり, 80ps 前後に分布のピークがある. 駆動力 1x のインバータを除くと 200ps 以上の範囲では 1 つの SET しか生じていない. 今回の測定では生じた SET 自体の個数が少ないものの, 16x インバータでも SET が生じている. その発生率は 1x インバータの約 1/6 である. 16x インバータでは負荷容量が大きいため, 反転に必要な電荷量が大きく, SET 発生率は非常に低いと考えられている. しかし今回の測定結果では 16x インバータでも SET が生じており, クロックツリーなどでも SET が問題となりうる. また 2x インバータと 4x インバータの SET 発生数を比較すると, どのパルス幅でも4x インバータの方が発生数の方が大きい. 2x インバータと 4x インバータではトランジスタの配置間隔やウェルコンタクトの配置位置は等しい構造であり, 違いはトランジスタ数に起因するインバータの面積である. 4x インバータの場合ではインバータを構成するトランジスタ数が多く, ドレイン領域の面積が 2x のインバータの 2 倍大きい. そのため, 中性子線が通過する確率が 2 倍高く, SET 発生数が高くなっていると推測される.

図 3.26: ウェルコンタクトによる SET パルス幅分布の変化. 縦軸を対数でプロットした場合.

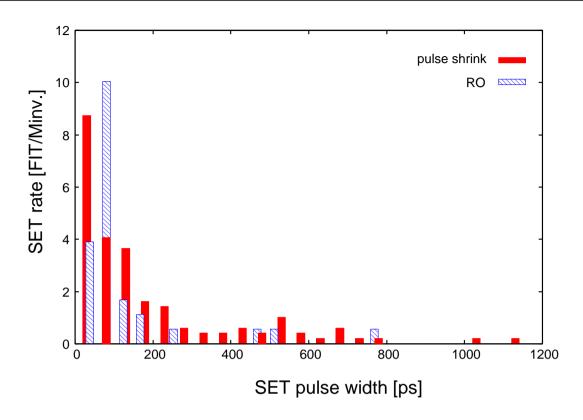

### SET パルス幅測定回路の測定結果の比較

バッファチェイン型測定回路とリング型測定回路の測定結果を比較する. 比較のために、リング型測定回路において 1x インバータで発生した SET 分布 (図 3.27) と、バッファチェイン型測定回路においてバッファで発生した SET 分布 (図 3.25) を図 3.28 にまとめて示す. 図 3.25 の方ではインバータ単位にするために、縦軸の SET 発生率を 1/2 とした. 2 つの測定回路で測定した SET パルス幅分布の最も大きな違いは 200ps 以上の SET 発生率である. リングオシレータ構造を用いた SET パルス幅測定回路では 200ps 以上の SET の発生割合は低い. この原因はパルス縮減効果 (pulse quenching) であると考えられる. リング型測定回路ではインバータを隣接して配置しているため、パルス縮減効果の影響が強いと推測される. 一方でバッファチェイン型測定回路ではバッファ間にフリップフロップを配置しており、バッファの固の距離は 5μm 離れている. バッファの出力側のインバータで SET が生じるとパルス縮減効果よる影響を受けず、長い SET が生じやすい.

図 3.27: インバータの駆動力に対する SET パルス幅分布の変化.

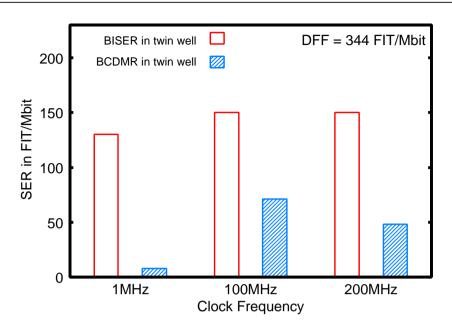

#### SET 発生率と平均パルス幅

図 3.27 から計算した SET 発生率と平均パルス幅, SET によるフリップフロップのエラー率を表 3.8 に示す。SET によるフリップフロップのエラー率は, 測定結果のパルス幅分布を式 (1.1) に代入して計算した。ラッチの保持制約 w は 40ps とし, 動作周波数は 1 GHz として計算した。比較のためにフリップフロップにおける SEU の発生率も同様に表 3.8 に示す。SEU 発生率にはクロック信号が"0" の場合のシフトレジスタ (a) の SEU 発生率を用いた。SEU 発生率は保持データで大きく異なるため, 平均値を用いている。

バッファチェイン型測定回路を用いて測定したバッファの場合では平均 SET パルス幅が大きく、それ以外では 100ps 程度と小さい。前節で説明したように pulse quenching によって減少したと推測される。SET によるエラー率は SEU の発生率の 0.14% から 2.5% と小さい。しかし 1 つのフリップフロップに対して接続される組み合わせ回路は複数の論理ゲートで形成されるため、SET によるエラー率は組み合わせ回路の規模に依存する。組み合わせ回路規模に合わせた SET の対策が必要となる。特に多重化回路では SEU 発生率が低いため、SET によるエラーが顕在化すると推測される。また 16x インバータなどのク

図 3.28: 測定回路の違いによる SET パルス幅測定結果の違い.

ロック部分やフリップフロップ内部のクロックバッファで SET が生じた場合では、パルス幅によらず SET が生じるとエラーとなりうる. ソフトエラー耐性を高めるには SET を考慮した設計も必要となる.

最後に回路シミュレーションとの比較結果を図 3.29 に示す. 値は異なるものの, 4x や 16x でもエラーが生じている点では一致している. また基板電位の変動を考慮しない既存手法の場合, 4x や 16x では SET は生じていない. 寄生バイポーラトランジスタによって供給される電荷によってトランジスタの出力が反転し, 駆動力の大きいものでも SET が生じていると推測される.

### **3.4.4** 論理ゲートにおけるシングルイベント効果の特性のまとめ

2種類のSETパルス幅測定回路を用いてSETパルス幅を測定することで以下の特性が明らかとなった。

● SET はパルス幅が小さいほど発生率が高く、200ps 以下が大部分を占める.

|            | 発生率            | 平均パルス幅 | SET によるエラー率 |

|------------|----------------|--------|-------------|

| 測定対象       | [FIT/Minv.]    | [ps]   | [FIT/Minv.] |

| 1x         | 19             | 135    | 2.4         |

| 2x         | 5.0            | 91     | 0.5         |

| 4x         | 11             | 99     | 1.0         |

| 16x        | 3.3            | 180    | 0.6         |

| バッファ(28μm) | 50             | 180    | 8.8         |

| バッファ(5μm)  | 46             | 130    | 5.0         |

| SEU        | 344 [FIT/Mbit] | N/A    | N/A         |

表 3.8: SET 発生率と平均パルス幅.

図 3.29: インバータの駆動力に対する SET 発生率の変化

- ウェルコンタクトをバッファに隣接した場合では 400ps 以上の長いパルスが減少する.

- 2x インバータよりも 4x インバータの方が SET の発生率が高く, SET 発生率は駆動力の増加に対して減少しない場合がある. 駆動力を強くしても SET によるエラーはあまり減少しない.

- 16x インバータでも SET は生じており、1x インバータの 1/6 程度の発生率である.

クロック部分でも SET の対策が必要となる.

● 動作周波数 1GHz の場合では、SET によるエラーは SEU 発生率の 0.14% から 3.2% となった。 多重化フリップフロップなどでは SET の対策が必要になる.

# 3.5 まとめ

本章では中性子線を用いた加速試験により、集積回路で生じるシングルイベント効果の特性評価を行った結果について報告した。フリップフロップにおけるシングルイベント効果の測定では、4種類のシフトレジスタを用いることで SEU や MCU の発生率を評価した。フリップフロップでも SRAM 同様に MCU が生じており、MCU /SEU の値は最大で 23% になった。フリップフロップの配置をずらすことでラッチ間距離依存性を測定し、ラッチ間距離に対して MCU がべき乗または指数で減少することを明らかにした。ウェルコンタクト密度に対する MCU 発生率の依存性を評価した。上下に配置したフリップフロップの間にウェルコンタクトを配置することで MCU の 99%を除去できることを実測により示した。今回の測定に用いた 65nm プロセスなどの微細プロセスでは、MCU によるエラーは多重化回路のエラー耐性を減少させる大きな問題となりうる。しかし MCU はラッチ間距離やウェルコンタクト密度などに強い依存性を持つため、これらの特性を考慮した設計を行うことで大きくエラー耐性が向上することが期待できる。

論理ゲートのシングルイベント効果である SET の測定ために, 2 つの SET パルス幅測定回路を提案した. 従来の SET パルス幅測定回路の問題点である測定精度を向上させた測定回路を提案した. また回路面積の小さい測定回路も同時に提案した. 提案した SET パルス幅測定回路を用いて SET のパルス幅分布を測定した. SET パルス幅の分布は指数分布となっており, パルス幅の大きい SET ほど発生率が小さいことを確認した. またウェルコンタクトの挿入間隔を密にすることで, 200ps 以上の SET パルスを 90%以上低減できることを示した. 駆動力の違いによる SET パルスの変化を評価した結果を報告した. クロックに用いられるような 16x と大きいインバータでも SET が生じており, その発生率は 1x インバータの 1/6 となった. 測定結果から SET がフリップフロップに取り込まれてエラーとなる確率を計算した. バッファ1 段の SET によるエラー率は SEU と比較すると, 0.14%から 2.5%と小さい. しかしフリップフロップ 1 段当たりに接続される論理ゲートのが多い場合や, SEU が生じてもエラーとはならない多重化回路では, SET によるエラーの割合が増加するため, SET を低減する設計が必要となる.

# 第4章

# ソフトエラー耐性向上手法

本章ではソフトエラー耐性の高い回路構造や、ソフトエラー耐性が向上する設計手法 を示す.

# 4.1 まえがき

第2章や第3章で示したように、65nmプロセスのフリップフロップではMCUが発生する.中性子線による実測結果ではMCU/SEUは最大で23%となった.フリップフロップのソフトエラー対策として一般的に用いられる多重化回路はMCUに脆弱であるため、MCUの耐性を考慮した設計を用いる必要がある.多重化回路ではMCUによるエラーだけでなく、SETによるエラーも無視できない.動作周波数を1GHzと想定する場合では、バッファ1段で生じるSETによるエラー率はSEU発生率の0.14%から2.5%となる.フリップフロップ1段あたりに接続される論理ゲートが多い場合や、SEUが生じてもエラーとはならない多重化回路では、SETによるエラーの割合が増加する.ソフトエラー耐性を高めるにはSEUだけでなく、MCUやSETも考慮した設計が必要である.

本章では面積や遅延のオーバーヘッドの少ないソフトエラー耐性フリップフロップを提案する. 第2章や第3章の結果を基に、多重化回路で生じるMCUを低減する設計手法や、論理ゲートのSETを低減する手法を示す。最後にMCUを低減する設計手法を用いて提案するソフトエラー耐性フリップフロップを試作し、中性子線によってソフトエラー耐性を実測した結果を示す。MCUを考慮せずに設計した場合や従来回路のエラー耐性と比較することで、提案する回路構造と設計手法の有効性を確認する.

# 4.2 従来の耐ソフトエラー回路

本節ではこれまでに提案されている耐ソフトエラーフリップフロップの構造を紹介し、 その課題を述べる.

# 4.2.1 三重化フリップフロップ

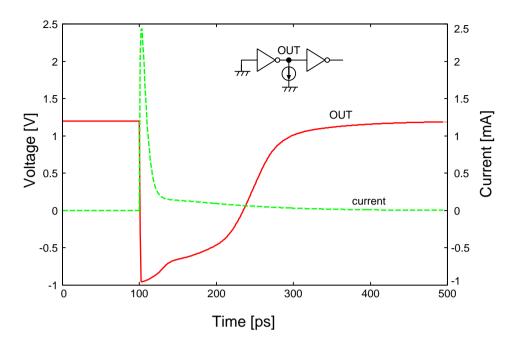

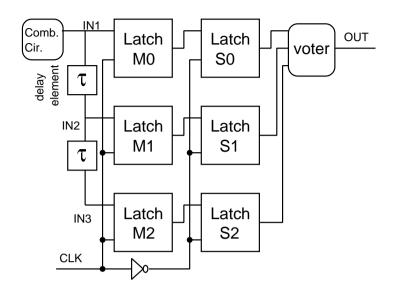

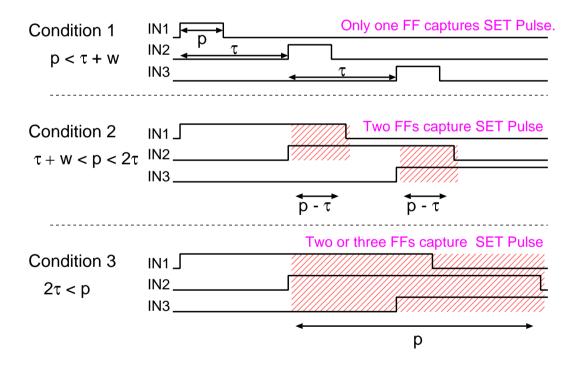

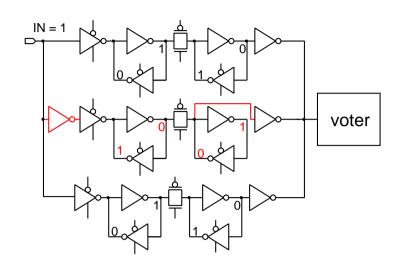

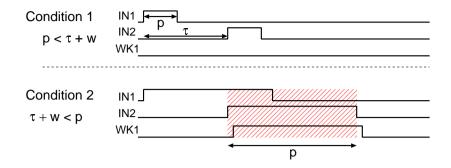

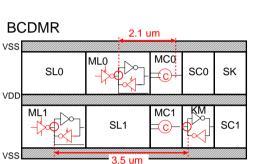

三重化フリップフロップの構造を図 4.1 に示す [72]. 三重化フリップフロップは3つ のフリップフロップの出力を多数決回路 (voter) に接続した構造となっている. 三重化フ リップフロップの出力は3つのフリップフロップの保持データの多数決によって決定さ れるため、SEUによって1つのフリップフロップの保持データが反転しても正しい値が 出力される。三重化フリップフロップでは各フリップフロップの入力である IN1 と IN2 の間と、IN2とIN3の間に遅延素子が挿入されている、遅延素子によって SET の到達時間 がずれるため、SET が複数のフリップフロップに取り込まれることを防ぐ構造となって いる. 遅延素子による SET の除去を図 4.2 に示す. 図 4.2 には図 4.1 の IN1, IN2, IN3 の電 圧波形を示している. 組み合わせ回路で生じた SET のパルス幅の範囲で3種類の条件に 分けて示している. 24.2 の条件 1 のように遅延素子の遅延時間  $\tau$  より SET のパルス幅 pが小さい場合では、SET によって反転するフリップフロップは多くとも 1 つとなる. そ のため、SEU と同様に SET のエラーも多数決回路によって除去される. しかし図 4.2 の条 件 2, 3 のように SET パルス幅の方が $\tau$ より大きい場合では、複数の入力が SET によって 同時に反転している範囲が存在し、図4.2ではその範囲を斜線で示している. 斜線部でク ロックが遷移すると、SETによって複数のフリップフロップの保持データが反転する。こ の場合では三重化フリップフロップでもエラーとなってしまう.

SET に対する耐性は遅延素子の遅延時間によって変化する。三重化フリップフロップの入力が遷移してから出力が遷移するまでに必要な時間を遅延時間と定義すると、遅延時間とソフトエラー耐性はトレードオフの関係となる。効果的にソフトエラー耐性を向上させるには、SET のパルス幅分布を正確に評価して遅延時間を決定する必要がある。完全に SET を除去する方法として、組み合わせ回路も三重化する構造もあるが、この方法では組み合わせ回路の面積も3倍となる。三重化フリップフロップは SEU と SET 両方に対して耐性を持ち、1クロック周期の間に2つのフリップフロップが反転しない限りエラーとならない。しかし面積や消費電力の増加は通常のフリップフロップの3倍以上となる。

図 4.1: 2 つの遅延素子を挿入した三重化フリップフロップ [72].

図 4.2: 遅延素子による SET の除去.

### DICE ラッチ

DICE (Dual Interlocked strage CEll) ラッチの構造を図 4.3 に示す [47]. DICE ラッチは ラッチの持つインバータ 2 段によるループ構造をインバータ 4 段で構成した回路である.

図 4.3: DICE (Dual Interlocked Storage Cell) ラッチ [47].

インバータを構成する nMOS トランジスタと pMOS トランジスタの入力をそれぞれ別々のインバータの出力に接続している. 1 つのインバータが放射線によって反転しても, 次段のインバータを構成するトランジスタの片方の入力が反転するだけである. そのため次段の出力は中間電位となり, さらに次段のインバータでは正しい値が保たれる構造となっている.

DICE ラッチは面積の増加がインバータ 2 つのみと少ないが、SEU の耐性も 29 倍から 103 倍しか増加しない [14]。この原因は 4 つのインバータが隣接して配置されるため、シングルイベント効果の影響を複数のインバータが受けるためである。そのためインバータ間の距離を  $1\mu$ m 以上離して用いたり [24]、インバータのウェルを分離することで寄生バイポーラ効果の影響を複数のインバータが受けないようにした回路が考案されている [50]。図 4.3 に示した構造の他にもラッチ部分のループ構造を改良して SEU 耐性を向上させた回路が多数提案されている [49,73]。しかし DICE ラッチのようにループ構造を改良した回路では SET に対する耐性はない。遅延素子を 2 つの入力間に接続すると、保持データの書き換え時に遅延素子の遅延時間  $\tau$  の期間中インバータに貫通電流が流れてしまう。DICE ラッチを用いた回路のソフトエラー耐性は SET に起因するエラー率に制約される。正確に DICE ラッチのソフトエラー耐性を測定するには SEU によるエラー率と SET によるエラー率の測定をする必要がある。

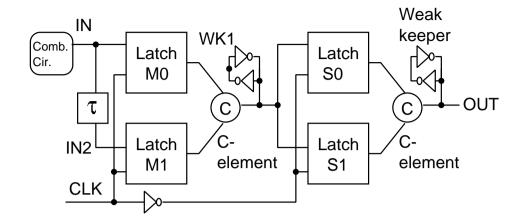

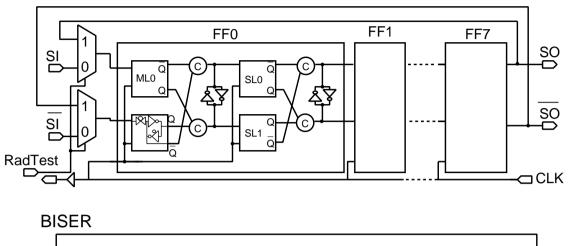

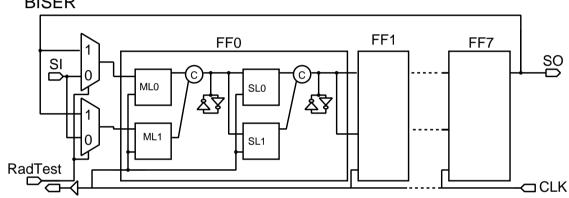

#### BISER

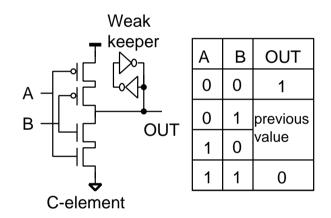

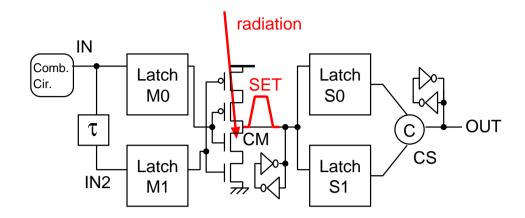

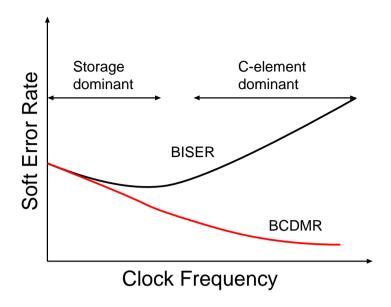

BISER (Built In Soft Error Resilience) を図 4.4 に示す [52]. C素子 (C-element) と保持力の弱い記憶素子 (weak keeper) の構造を図 4.5 に示す. C素子の 2 つの入力信号が等しい場合では、保持力の弱い記憶素子の保持データは C素子の出力によって書き換えられる. 一方で C素子の 2 つの入力信号が異なる場合ではハイインピーダンス状態になるため、保持力の弱い記憶素子によって直前の値が保持される. そのため、BISER で SEU が生じ、1 つのラッチの保持データが反転しても正しい値を保つ. SET に関しても三重化フリップフロップと同様に遅延素子などにより除去する. 三重化フリップフロップと比較してBISER は面積が小さく、消費電力も小さい. 遅延素子も 1 つであるため、遅延素子で消費される電力や面積も BISER では半分となる.

BISER は面積,消費電力の面で三重化フリップフロップよりも性能が良い.しかしBISER は内部で生じる SET に対して脆弱である. BISER では C 素子の出力が直接 2 つのスレイブラッチの入力に接続されている.マスターラッチとスレイブラッチの間に存在する C 素子で SET が生じた場合は、2 つのスレイブラッチの入力が同時に反転してエラーとなりやすい.この BISER の内部で生じる SET に対する脆弱性を図 4.6 に示す.マスターラッチとスレイブラッチ間の C 素子である図 4.6 の CM で SET が生じると、スレイブラッチ SO、S1 の入力は同時に反転してしまう. SO、S1 の入力が同時に反転している間にクロック信号が遷移すると、スレイブラッチである SO と S1 は反転した値を保持し、BISER の保持データが反転する.そのため、BISER は CM で生じた SET に対して脆弱である.一方でスレイブラッチの後段に接続されている C 素子の CS で SET が生じた場合では、次段の遅延素子によって除去される.

C素子はnMOSトランジスタとpMOSトランジスタを2つずつ直列に接続しているため、電流量が小さく面積が大きい. そのためインバータと比較してSETが生じやすい. 動作周波数が高い場合ではSETによるエラーが増加するため、BISERのエラー耐性は低くなると推測される.

また BISER ではラッチ構造ではなく、保持力の弱い記憶素子を用いているため、ばらつきに弱い. ばらつきによって保持力の弱い記憶素子の保持力が強い方にばらつき、C素子の駆動力が弱い方にばらついた場合では、C素子が値を書き換える際の遅延時間が増加したり、値そのものを書き換えられなくなる状況も発生する. ばらつきは低電圧で増加するため、BISER は低電圧では動作し難いという欠点を持つ.

図 4.4: 二重化フリップフロップ (BISER)[52].

図 4.5: C 素子の構造と真理値表 [52].

# 4.3 耐ソフトエラー回路の提案

二重化フリップフロップの BISER はフリップフロップ内部で生じる SEU や, フリップフロップへの入力データを生成する組み合わせ回路で発生する SET に対して高い耐性を持たせることができる。しかし図 4.6 に示したようにフリップフロップ内部で発生する SET に対して脆弱である。マスターラッチとスレイブラッチの間にある C 素子で SET が生じると, スレイブラッチが同時に反転してエラーとなりうる。第 3.4.3 節で示したように, バッファで生じた SET によるフリップフロップのエラー率は 1GHz の動作周波数で 2.5%である。 C 素子がバッファ1 段と同等の SET 発生率を持つと仮定すると, BISER のソフトエラー耐性は通常のフリップフロップの 30 倍程度であると予想される。より高いソ

図 4.6: BISER の SET に対する脆弱性.

フトエラー耐性を実現するには C 素子で生じた SET によるエラーを抑える必要がある.

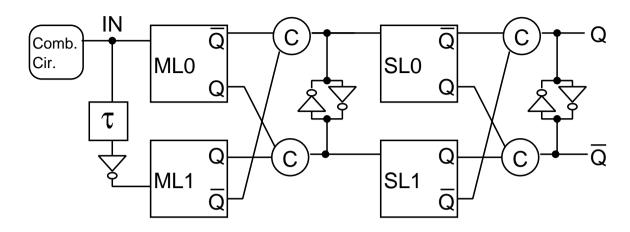

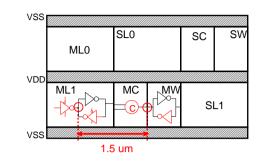

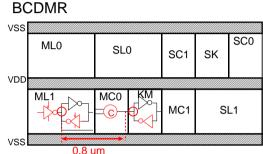

C素子で生じた SET によるエラーを抑える方法として、図 4.7 に示す BCDMR (Bistable Cross-coupled Dual Modular Redundancy Flip-Flop) を提案する. BCDMR では C 素子を二重化して出力を別々のスレイブラッチの入力に接続することで、C 素子で SET が生じても最大で 1 つのスレイブラッチしか反転しないようにしている. 単に二重化するだけでは保持力の弱い記憶素子も二重化する必要があるが、BCDMR では片方の C 素子の入力にマスターラッチの反転出力を用いることで保持力の弱い記憶素子を 2 つの C 素子で共有している. そのため 2 つの C 素子の出力は保持力の弱い記憶素子を介して接続されているが、片方の C 素子で生じた SET パルスは保持力の弱い記憶素子のインバータを通過するため、正しい値を出力している駆動力の強い C 素子の出力を反転することがない.