# 髙井研究室の紹介

~誰も思いつかない回路の自動設計~

電気電子工学系 教授 髙井伸和

2023年4月3日(月)

### 工学とは?

人類は無知であることを認めたことが科学の始まり

真理を突き止めるのが理学

それをエンジニアリングで社会に還元し、人々の生活を豊かにするのが工学

工学では様々な道具を利用する

道具とは?→「数学」「物理」「化学」「アルゴリズム」など

例

円の面積や円周の求め方を考えるのは理学 その考え方を使って車輪を作るのが工学

(車輪があればものが楽に運べる。そのためには円の面積や円周の求め方が必要)

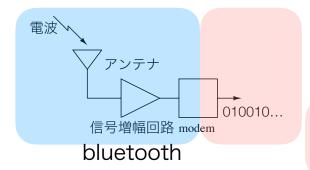

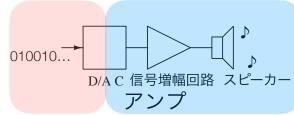

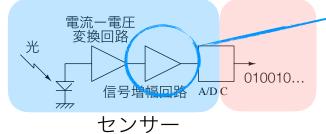

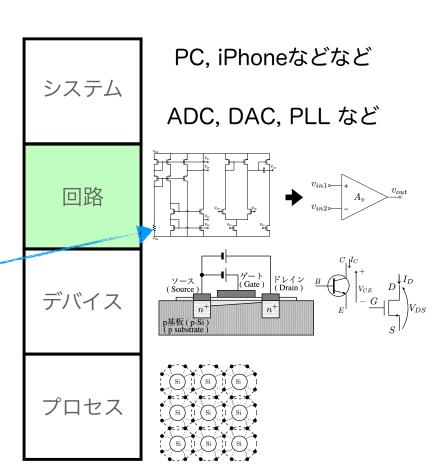

# アナログ集積回路設計

アナログ信号って何? 回路設計って?

アナログ信号:連続に変化する信号 我々の身の回りにある信号

デジタル信号:0と1で表現された信号 計算機で処理可能な信号

増幅回路:信号処理回路の基本回路

人工知能で計算機にアナログ集 積回路を自動で設計させる!

### 人工知能を用いた回路設計の現状

⑧試作

⑨量産

日本經濟新聞

トップ 速報 オピニオン 経済 政治 ビジネス 金融 マーケット マネーのまなび テック ・・・

AIが半導体の「設計者」に Google、回路配置100倍早く

AI +フォローする

2021年12月9日 2:00 [有料会員限定]

人工知能 (AI) が半導体設計に革新をもたらし始めた。米グーグルは中核の回路配置工程に かかる時間を従来より100倍早くし、膨らむ開発費の抑制につなげる。カギを握るのは、AI 自身が試行錯誤して「職人」を圧倒する技を身につける「強化学習」と呼ぶ技術だ。物流な どの分野でも導入が広がりつつあり、生産性の大幅向上が期待される。

グーグルは半導体の自社設計に力を入れている(同社が5月に開催したイベント)

設計者の労力を何千時間も節約できる可能性がある――。グーグルの研究グループは6月、 AIを用いた半導体回路の設計手法を英科学誌ネイチャーに発表した。演算性能や消費電力、 チップの大きさなどについて、人間の設計者が数カ月かけたものと同等以上の回路配置を6 時間以内に生成できるという。

半導体の設計は高度で複雑だ。指先にのるサイズのチップ上に大量の論理回路を集積し、配 置パターンは10の2500乗以上、つまり1の後に0が2500個以上並ぶほどになる。天文学的 た数の組み合わせの中から最適な設計を導く必要がある。

そこで威力を発揮するのが、AIが成功と失敗を重ねて性能を高めていく強化学習だ。AIはす でに「教師あり学習」と呼ぶ手法を中心に業務効率化などに役立っているが、膨大な選択肢 から最適解を導く計算は難易度が高い。強化学習はそうした複雑な課題の克服に道を開くと 期待を集めている。

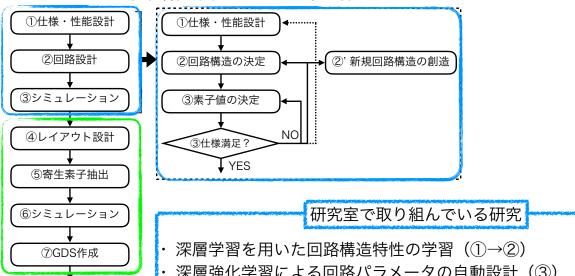

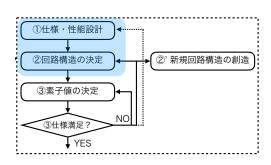

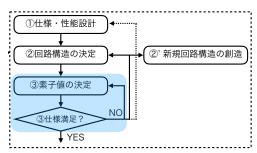

#### アナログ回路設計フローの概略

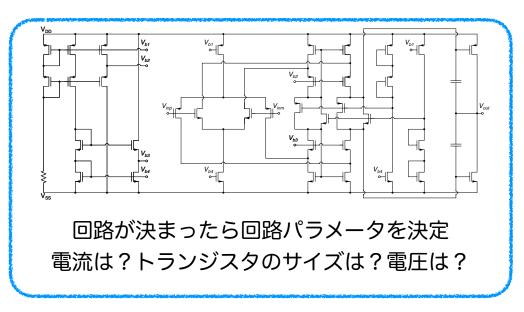

- 深層強化学習による回路パラメータの自動設計(③)

- 深層学習・深層強化学習によるアナログ回路構造の自動合成(②)

設計者の労力を何千時間も節約できる可能性がある――。グーグルの研究グループは6月、 Alを用いた半導体回路の設計手法を英科学誌ネイチャーに発表した。演算性能や消費電力、 チップの大きさなどについて、人間の設計者が数カ月かけたものと同等以上の回路配置を6 時間以内に生成できるという。

# アナログ集積回路の自動設計 (①→②)

知識・経験・勘を駆使して最高の回路を作る

#### 演算増幅器の仕様

| 特性                    | 最低要件     |

|-----------------------|----------|

| 消費電力 (PC) [W]         | 100mW以下  |

| 直流利得 (DC Gain) [dB]   | 45dB以上   |

| 位相余裕 (PM) [°]         | 45°以上    |

| 利得帯域幅積 (GBW) [Hz]     | 1MHz以上   |

| スルーレート (SR) [V/s]     | 0.1V/s以上 |

| 全高調波歪 (THD) [%]       | 1%以下     |

| 同相除去比 (CMRR) [dB]     | 40dB以上   |

| 電源電圧変動除去比 (PSRR) [dB] | 40dB以上   |

| 出力電圧範囲 (OVR) [%]      | 5%以上     |

| 同相入力範囲 (CMIR) [%]     | 5%以上     |

| 占有面積 (Area) [mm²]     | 1mm²以下   |

| 出力抵抗 (OR) [Ω]         | 要件無し     |

| 入力換算雑音 (IRN) [V/Hz]   | 要件無し     |

➡ 熟練の設計者は過去の経験・知識から適切な回路を選択

人工知能で学習し計算機が適切な回路選択を可能に!(特許出願中)

# アナログ集積回路の自動設計(③)

#### 決定した回路パラメータの自動設計

#### 演算増幅器の仕様

| 特性                    | 最低要件                |

|-----------------------|---------------------|

| 消費電力 (PC) [W]         | 100mW以下             |

| 直流利得 (DC Gain) [dB]   | 45dB以上              |

| 位相余裕 (PM) [°]         | 45°以上               |

| 利得帯域幅積 (GBW) [Hz]     | 1MHz以上              |

| スルーレート(SR)[V/s]       | 0.1V/s以上            |

| 全高調波歪 (THD) [%]       | 1%以下                |

| 同相除去比 (CMRR) [dB]     | 40dB以上              |

| 電源電圧変動除去比 (PSRR) [dB] | 40dB以上              |

| 出力電圧範囲 (OVR) [%]      | 5%以上                |

| 同相入力範囲 (CMIR) [%]     | 5%以上                |

| 占有面積 (Area) [mm²]     | 1mm <sup>2</sup> 以下 |

| 出力抵抗 (OR) [Ω]         | 要件無し                |

| 入力換算雑音 (IRN) [V/Hz]   | 要件無し                |

深層強化学習で計算機が適切なパラメータを自動設計! (特許出願中)

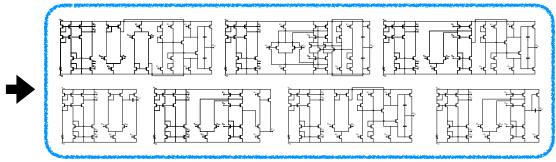

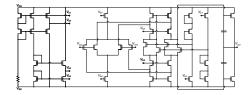

### アナログ集積回路の自動合成

#### 誰も思いつかない回路を計算機で自動合成

#### 演算増幅器の仕様

| 特性                    | 最低要件                |

|-----------------------|---------------------|

| 消費電力 (PC) [W]         | 100mW以下             |

| 直流利得 (DC Gain) [dB]   | 45dB以上              |

| 位相余裕 (PM) [°]         | 45°以上               |

| 利得帯域幅積 (GBW) [Hz]     | 1MHz以上              |

| スルーレート (SR) [V/s]     | 0.1V/s以上            |

| 全高調波歪 (THD) [%]       | 1%以下                |

| 同相除去比 (CMRR) [dB]     | 40dB以上              |

| 電源電圧変動除去比 (PSRR) [dB] | 40dB以上              |

| 出力電圧範囲 (OVR) [%]      | 5%以上                |

| 同相入力範囲 (CMIR) [%]     | 5%以上                |

| 占有面積 (Area) [mm²]     | 1mm <sup>2</sup> 以下 |

| 出力抵抗 (OR) [Ω]         | 要件無し                |

| 入力換算雑音 (IRN) [V/Hz]   | 要件無し                |

|                       |                     |

計算機に新たな回路構造を自動で 設計させるチャレンジングな研究 JST A-STEP(国からの大型予算)のもと 企業と共同で研究に取り組み 3年後の完成、5年後の商品化を目指す

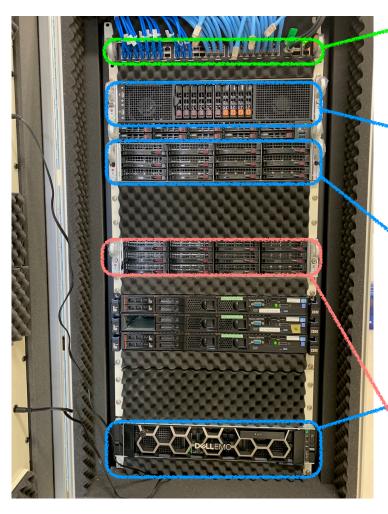

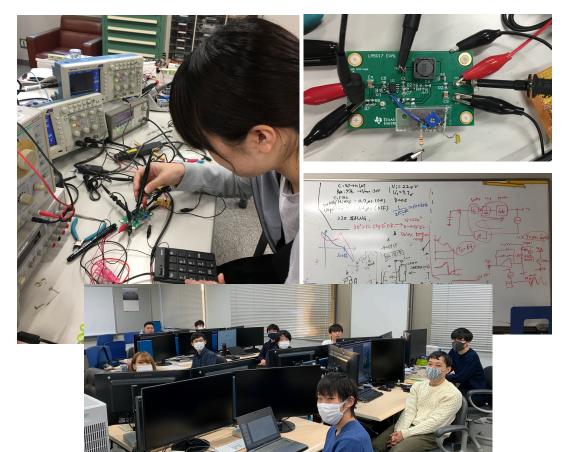

## 研究設備

X3348T

48 port 10GBase-T

Layer 2 / 3 / 4 Prioritization

ネットワークスイッチ

CPU: Xeon Gold 6326 (16Core 2.9GHz) x 2 [計:32コア]

Memory: 1TB

SSD1: SATA 480GB x2本

SSD2: SATA 1.92TB x5本 (RAID6) GPU: NVIDIA A100 (80GB) ×1基

CPU: EPYC 7313 (16Core 3.0GHz) x 2 [計:32コア]

Memory: 1TB

SSD1: SATA 480GB x 2本

SSD2: SATA 1.92TB x 5本 (RAID6)

GPU: NVIDIA RTX A6000 (48GB) × 1基

CPU:Xeon Platinum 8270 (26Core, 2.7GHz) x 4 [計:108コア]

Memory:1TB

SSD1:SATA 240GB x2本

CPU:Xeon Bronze 320R (8Core, 1.9GHz)

Memory:64GB

SSD1:SATA 2TB x8本

ファイルサーバ

計算ノード

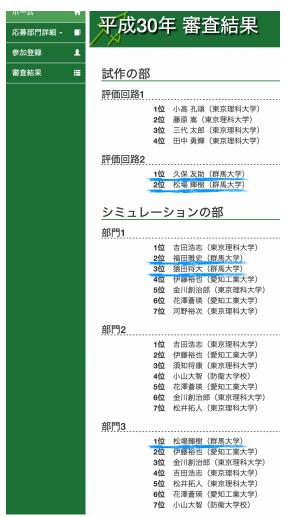

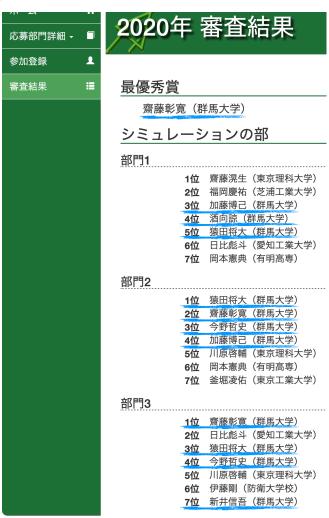

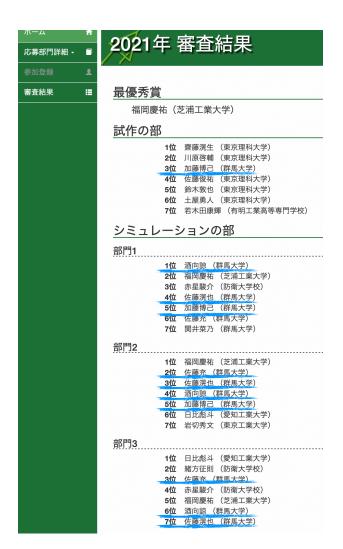

### 演算増幅器設計コンテスト

## 研究室の様子と研究室の1年

\* 4月~7月:新人ゼミ

\*8~9月:オペアンプコンテスト参加

\*9月:SKK(4大学合同勉強合宿)

\* 2月:卒業研究発表会

\* 不定期:飲み会、タコ焼きパーティ

SKK in 草津温泉

### まとめ

来れ!新しい研究室の立ち上げを楽しめる学生

- \*アナログ回路設計の知識を習得

- ・就職活動の幅が広がります

- ・オペアンプコンテスト入賞者多数

- \*人工知能アルゴリズムを道具として習得

- ・これからの時代に必要不可欠な人材

- \*就職活動も安心!

- ・企業はアナログ回路設計者を求めています

- ・システム系の会社にも就職可能